當精心設計的語音產品發出提示音時,背景中若隱若現的“嘶嘶聲”或“嗡嗡聲”如同不和諧的音符,嚴重影響著用戶體驗的純凈度。這種令人煩惱的底噪(Background Noise),尤其在廣州唯創電子等語音芯片的DAC(數模轉換器)輸出端(如DACL腳)出現時,其根源往往直指兩大關鍵環節:電源純凈度與信號通路完整性。

一、DAC底噪:并非“天生”,實乃“環境干擾”

語音芯片內部的DAC模塊,承擔著將數字語音編碼轉換成模擬音頻信號的核心任務。理想的DAC輸出應是干凈、純粹的音頻信號。然而,現實中的底噪如同信號上的“塵埃”,主要來源包括:

電源“漣漪”的滲透:

為芯片供電的VCC線路并非理想直流。開關電源的紋波、數字電路高速切換引起的瞬態電流、甚至外部電磁干擾耦合進來的噪聲,都會沿著電源線“爬”進敏感的模擬電路(如DAC和內部基準源),最終污染輸出信號。

DAC自身的“呼吸”:

任何實際DAC芯片在轉換過程中都會產生微小的本底噪聲(量化噪聲、熱噪聲等),雖然通常很低,但在高增益放大后可能變得可聞。

輸出端的“天線效應”:

DAC輸出引腳(如DACL)及其走線,就像一根小型天線,容易拾取周圍環境中的高頻電磁干擾(EMI)。如果沒有適當的濾波,這些干擾會直接混入音頻信號。

二、實戰克噪:兩招破解唯創語音芯片DAC底噪

針對廣州唯創電子語音芯片DACL腳的底噪問題,以下兩個經過驗證的硬件優化策略效果顯著:

策略一:打造“超凈”電源防線——VCC入口的電容組合拳

問題核心:電源噪聲是DAC底噪的頭號元兇。

解決方案:在語音芯片的VCC供電入口處,采用“大小電容并聯”的經典濾波組合。

“大”電容擔當(主力儲能/低頻濾波):在原有設計(如已有一個10uF/106電容)的基礎上,并聯一個更大容量的電解電容或鉭電容(如47uF, 100uF)。它的作用如同水庫,能吸收電源線上低頻紋波和較大幅度的電流波動,穩定芯片供電電壓。

“小”電容精兵(狙擊高頻噪聲):緊挨著芯片VCC引腳和GND引腳,并聯一個或多個小容量的陶瓷電容(如0.1uF/104, 0.01uF/103)。這類電容具有極低的等效串聯電阻(ESR)和電感(ESL),響應速度快,能高效濾除電源線上高頻噪聲尖峰和開關干擾。

關鍵要點:

位置!位置!位置!大小電容都必須盡可能靠近語音芯片的VCC和GND引腳放置。走線過長會引入寄生電感,大大削弱高頻濾波效果。

接地回路短而粗:電容的接地端到芯片GND引腳的路徑要短且寬,確保低阻抗接地。

選型參考: 大電容常用鋁電解或鉭電容(注意耐壓和極性);小電容首選X7R/X5R等介質的陶瓷電容(NPO/C0G更佳但成本高)。

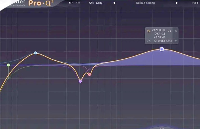

策略二:DAC輸出端的“守門人”——RC低通濾波

問題核心: DAC輸出信號本身可能包含高頻量化噪聲,且輸出線易受電磁干擾(EMI)。

解決方案: 在語音芯片的DACL輸出腳串聯一個小電阻(R),并接一個濾波電容(C)到地(GND),形成一個簡單的RC低通濾波器。

原理揭秘:該RC電路允許人耳可聽范圍內的低頻音頻信號(通常<20kHz)幾乎無衰減地通過,同時強力衰減DAC輸出中無用的高頻噪聲分量(遠高于音頻范圍)以及外部耦合進來的高頻EMI干擾。

元件選擇:

電阻(R): 常用阻值在100Ω 至 1kΩ之間。阻值太小濾波效果弱;阻值太大可能略微衰減高頻音頻信號(需權衡)。建議從330Ω或470Ω開始嘗試。

電容(C): 常用容值在100pF (101) 至 0.1uF (104) 之間。容值越大,對高頻的濾除越狠,但需注意與電阻配合形成的截止頻率(f_c = 1/(2πRC))不宜過低,以免影響正常音頻高頻響應(通常設在30kHz - 100kHz以上即可有效濾除超聲噪聲和射頻干擾)。常用選擇如1000pF (102), 0.01uF (103), 0.1uF (104)。

連接方式: DACL腳 → 串聯電阻(R)→ 輸出到后級電路(功放等)。電容(C)一端接在電阻R的后端(即輸出點),另一端就近接純凈GND。

關鍵要點:

就近接地:濾波電容C的接地端必須連接到芯片附近的、干凈的地平面(模擬地最佳),避免噪聲通過地線耦合回來。

PCB布局: R和C的元件以及連接線應盡量短,減小寄生參數影響。

三、進階思考:系統級降噪

地平面分割與單點連接:對于混合信號(數字+模擬)系統,合理的地平面分割(將敏感的模擬地AGND與嘈雜的數字地DGND分開)并在電源入口處或芯片下方進行單點連接,能有效阻止數字噪聲竄入模擬區域。

物理隔離:讓DAC輸出走線遠離高頻數字信號線(如時鐘、數據總線)、開關電源模塊和繼電器等強干擾源。

屏蔽: 在干擾特別嚴重的環境或對音質要求極高的場合,考慮對語音芯片及其模擬電路部分使用屏蔽罩。

軟件靜音: 在語音播放的間隙,通過芯片控制命令將DAC輸出靜音(Mute),徹底切斷噪聲通路。

結語:純凈之音,源于對“電環境”的精雕細琢

DAC底噪并非不可戰勝的頑疾。唯創電子語音芯片的“嘶嘶”雜音,本質是噪聲能量在電源與信號路徑上的失控泄露。通過VCC入口的“大小電容協同濾波”構筑穩固的能源堡壘,再輔以DACL輸出端精準的RC低通濾波架起信號凈化屏障,絕大多數惱人的背景噪聲都能被顯著壓制甚至消除。優秀的硬件設計,正是在這些細微之處見真章——每一次電容的精準選型與布局,每一條地線的優化路徑,都是通往“純凈之聲”的必經階梯。記住:在模擬電路的世界里,細節處的寧靜,方能成就整體體驗的完美。

-

dac

+關注

關注

43文章

2383瀏覽量

193117 -

語音芯片

+關注

關注

12文章

1971瀏覽量

37661 -

嵌入式硬件

+關注

關注

1文章

961瀏覽量

8697

發布評論請先 登錄

PCM3168A DAC輸出底噪問題如何解決

請問DAC8830噪底指標如何優化?

使用SRC4192輸出底噪雜音太大的原因?

求助各位老師: 自制1969功放底噪聲怎樣消除?

請教關于CODEC芯片ADAU1372\ADAU1777\ADAU1702 底噪問題

請問ADC芯片如何降低底噪

鎖相環芯片芯片底噪在低頻處是平的

ADAU1372\\ADAU1777\\ADAU1702的底噪問題怎么改善?

示波器如何測量底噪?示波器測量底噪的步驟

芯知識 語音芯片解決底噪的幾個實用技巧

芯知識|語音芯片(以廣州唯創電子WT588F02B為例)底噪聲優化指南

芯知識|廣州唯創電子錄音語音芯片底噪問題全解析與實戰解決方案

芯知識|語音芯片的“背景雜音”困擾:解碼DAC底噪的成因與克敵之道

芯知識|語音芯片的“背景雜音”困擾:解碼DAC底噪的成因與克敵之道

評論