01

簡介

SoC 設計團隊的任務是在創建昂貴的生產掩膜之前完成完整的系統級驗證。這意味著徹底審核所有硬件模塊、這些模塊之間的所有交互以及為最終應用創建的所有專用軟件,而且所有這些任務都要在芯片構建之前完成。雖然硬件加速器和桌面原型板是這項驗證中兩個眾所周知的參與者,但企業原型同樣具備重要的意義。

盡管仿真在設計的早期階段占據主導地位,但由于性能的原因,其更多的適用于模塊級驗證。一旦開始全芯片驗證,勢必需要以更快的速度處理實現完整覆蓋率所需的龐大數量的測試。硬件加速仿真承擔了其中大部分的工作負荷,而桌面原型單元則主要協助軟件開發人員檢驗他們的應用代碼。

最近,市場上出現了填補硬件加速器的強大功能與原型設計系統性能之間缺口的需求。這種解決方法被稱為企業原型設計,因為它融合了硬件加速仿真和桌面原型設計的特性,可以滿足在數據中心環境減輕硬件加速器負荷的新型使用案例的需求。利用它,驗證團隊可以在優化總體擁有成本的同時,強化其基于高速硬件的驗證資源。將硬件加速仿真、企業原型設計和桌面原型設計相結合,可以將 SoC 更快地推向市場,并增強對于芯片正確性的信心。

02

硬件加速器任務 — 新舊比較

硬件加速器已成為 SoC 硬件驗證的主力軍。它們的執行速度能夠高出普通仿真幾個數量級,是審核布置在單個芯片上大量硬件的關鍵要素。

硬件加速器設計體現了性能、實現各種可能的設計所需的基礎設施,以及最重要的,在出現問題時可實現全面調試的眾多工具之間的平衡。即使它們的運行速度達不到最終應用的速度,但要執行關鍵軟件仍舊綽綽有余,這也意味著,它們可以在啟動操作系統的同時探索類似軟件的低層驅動程序。

在線硬件加速仿真 (ICE) 是硬件加速器的另一種任務,這種任務在以前比較常見。ICE 的目標是為被測設計 (DUT) 輸入真實世界的工作負載,連接網絡或其他硬件以提供真實的數據流。由于 ICE 連接需要速率適配器來降低數據速率,以匹配硬件加速器的速度,因此驗證團隊已轉而使用虛擬化流量生成器,而不是 ICE。

VirtuaLab 虛擬化流量生成器可根據命令創建真實的工作負載。由于硬件加速器現在位于可從世界任何地方訪問的數據中心內,這些激勵源可通過網絡建立連接,輕而易舉地匹配硬件加速器的速度。因此,硬件速率適配器不是必要的,并且還能輕松、靈活地支持更廣泛的工作負載。

03

硬件加速器需要減負

硬件加速器承擔了 SoC 驗證的中央角色。這意味著每當電路發生變化時,必須重新運行回歸測試。這些回歸套件必須以盡可能快的速度執行數量持續增長的測試。這些測試已經通過一次,因此除非暴露出回歸錯誤,否則它們預計都會通過后續的每次測試。這意味著通常不需要硬件加速器的眾多調試功能。如果有失敗的回歸測試,那么硬件加速器可能是確定失敗原因的最佳角色,但正常而言,這只是極少的例外情況。

04

企業原型設計填補缺口

硬件加速仿真減負是企業原型設計單元的作用之一。它采用與硬件加速器相同的方式安裝在機架中并可遠程訪問。于是便可以將回歸套件從稀缺且更昂貴的硬件加速器轉移到成本較低的企業原型上。如果回歸測試失敗并且需要硬件加速器提供調試資源,則可以輕松地將該測試移回到硬件加速仿真環境進行根本錯誤原因調試。

除了以更低的成本提供更大容量之外,硬件加速器 DUT 也可以直接在原型上運行,幾乎不需要手動修改,運行速度大約是在硬件加速器上運行時的五倍。借助一些額外的 FPGA 優化工作,相比 Emulation,往往可以將回歸性能提升到 10 倍之多。這意味著回歸套件的運行速度也會加快,有助于分擔夜間回歸工作負荷,避免硬件加速器不堪重負。

最后,就像他們的桌面競爭產品一樣,企業原型也可以用于 ICE,利用非虛擬化的直接數據源連接。雖然由于網絡連接的原因,用于硬件加速仿真的虛擬化數據源會遭遇額外的事務處理延遲,但直接數據連接提供的數據更接近于實時數據。

通過承擔回歸、軟件驗證和 ICE 測試任務,企業原型可以減輕硬件加速仿真工作負載,同時實現原型在功能、速度和成本方面的優勢。

硬件加速器可在任何時候加載任意數量的設計。它們甚至大到足以同時加載多個項目。它們可以通過網絡輕松進行配置,有助于最大限度地提高它們的利用率。因此,一組給定的測試可能第一天在一個硬件加速器上運行,第二天又在另一個硬件加速器上運行。

相形之下,由于企業原型通常使用專用硬件配置,例如布線配置或 ICE 外圍設備,因此更典型的做法是,在項目持續期間配置一組特定的企業原型。包括連接 ICE 數據源在內,配置操作發生在項目開始時,之后便可根據需要使用這些原型,直到項目完成。這時便可以將它們重新用于另一個項目,而無需發運到世界各地。

05

桌面原型板的作用

桌面原型板是應用軟件的更優解決方案。一旦硬件設計穩定下來,就會對原型驗證板進行配置,并且在剩余的驗證周期內只進行少量的改動。它們通常采用 FPGA,可以在實現 DUT 的過程中優化性能。它們的運行速度可能比硬件加速器快一個數量級。

將這些低成本的原型板分發給軟件開發人員,由他們將這些板插入自己的桌面服務器。當需要運行軟件測試時,他們就可以更快地收到基于實際硬件設計的結果。

由于它們的速度很快,將這些板直接連接到真實世界的數據源也更加輕松。于是,ICE 便基本上從硬件加速器轉移到桌面原型板上。

06

完整的 SoC 驗證環境

Veloce 提供了三種關鍵的基于硬件的完整 SoC 驗證工具:

Veloce Strato 硬件加速器提供了驗證大型 SoC(包括硬件、軟件驅動程序、操作系統和部分應用代碼) 所需的容量和調試可見性

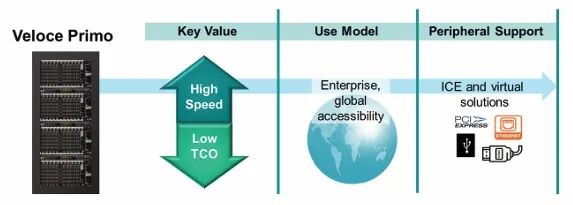

Veloce Primo 企業原型為運行硬件加速仿真回歸套件、執行 ICE 測試和驗證應用軟件提供了更高性能的硬件

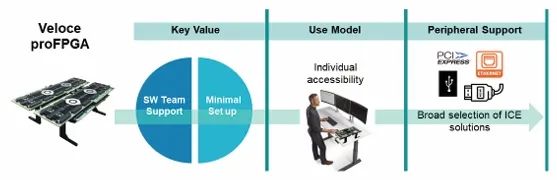

對于希望更直接地接觸其原型板以進行本地測試的軟件開發人員,則可使用 Veloce proFPGA 桌面原型。此外,開發人員還可以將桌面原型發送給他們的客戶,以便順利進行系統集成、驗證和有效性確認

Veloce Primo 企業原型系統提供了比桌面原型更高的容量,以及比硬件加速器更低的每門成本和每 MHz 成本。這有助于驗證團隊降低其硬件驗證資源的總體擁有成本,同時也有助于加快驗證周期。

-

soc

+關注

關注

38文章

4354瀏覽量

221813 -

芯片驗證

+關注

關注

5文章

39瀏覽量

47550 -

硬件加速器

+關注

關注

0文章

43瀏覽量

13000 -

Veloce

+關注

關注

0文章

13瀏覽量

14035 -

西門子EDA

+關注

關注

1文章

8瀏覽量

90

原文標題:Veloce Primo 補全完整的 SoC 驗證環境

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【道生物聯TKB-620開發板試用】TK8620 RISC-V開發環境搭建和固件編譯和燒錄

中微公司ICP雙反應臺刻蝕機Primo Twin-Star取得新突破

西門子EDA亮相2025玄鐵RISC-V生態大會

AMD技術賦能西門子FPGA原型設計解決方案

西門子EDA邀您相約2025玄鐵RISC-V生態大會

新思科技推出全新硬件輔助驗證產品組合

西門子Veloce硬件輔助驗證平臺升級

Oracle數據庫的多功能集成開發環境

SoC的數字簽名加解密過程

如何提升SoC的安全性

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

Veloce Primo補全完整的SoC驗證環境

Veloce Primo補全完整的SoC驗證環境

評論