RISC-V架構以追趕者的姿態在多個應用領域與X86架構和ARM架構展開競爭。在服務器應用領域,RISC-V架構正在重新定義服務器芯片領域必備的安全、虛擬化和RAS等規格和規范。

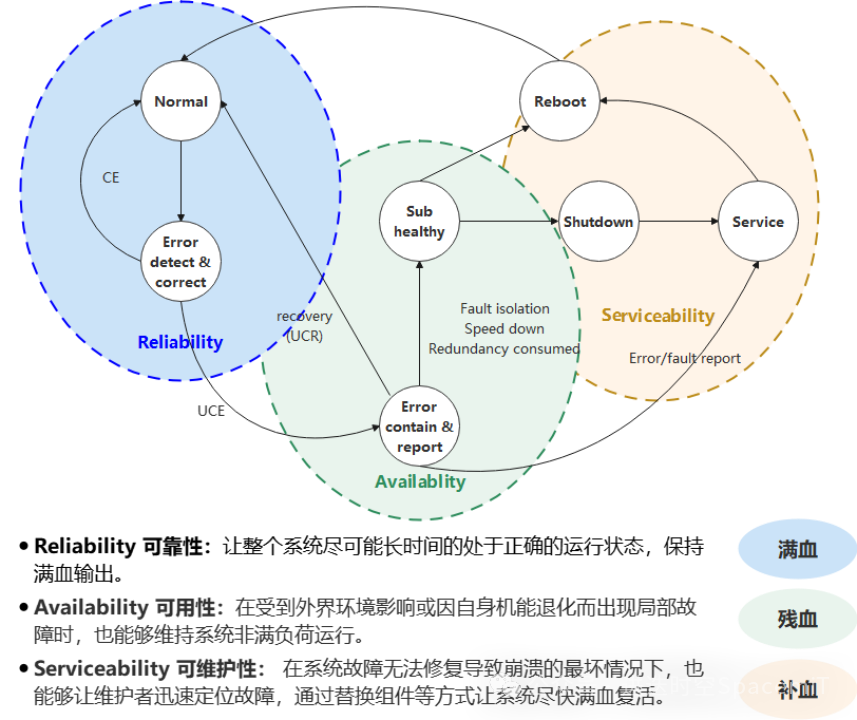

服務器CPU芯片作為服務器核心部件,承擔了CPU算力、高速內存接口和高速IO傳輸接口等功能。從應用場景和需求出發,RAS(Reliability、Availability、Serviceability)已經成為服務器系統必備的功能屬性:高可靠性(Reliability)可以延長整個系統硬件“滿血”運行的持續時間,此階段為服務器系統最理想狀態;高可用性(Availability)使得硬件系統發生隨機或者持續硬件故障時,通過軟硬件協同處理,系統仍然可以維持“殘血”運行,不至于因為關機導致服務中斷;高可維護性(Serviceability)使得在系統崩潰時,能夠迅速定位故障,通過替換部件等方式對服務器進行“補血”,為系統盡快恢復運行提供保障。

(圖1:RAS定義框架)

進迭時空以RISC-V高性能算力計算核心SpacemiTX100 Core為基礎構建的服務器CPU芯片,充分考慮了服務器的RAS需求,集成了包含RAS組件功能特性和RAS管理功能特性的完整RAS軟硬件方案,并在應用層上對X86和ARM服務器的RAS方案做了兼容適配:RAS處理機制遵循Firmware First準則;通過RISC-V協議棧,支持ACPI的APEI規范,獲得面向OS的錯誤信息格式兼容。進迭時空的RAS方案完全遵循RISC-V RERI(RAS ErrorRecordRegisterInterface)故障處理接口規范,通過內存映射的寄存器接口統一了各種RAS信息的記錄和上報。

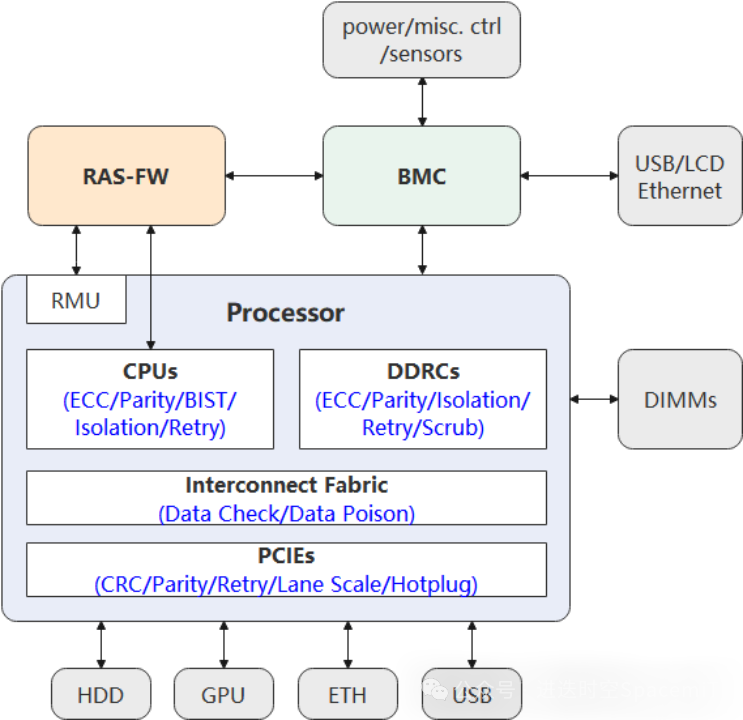

進迭時空RAS組件架構

進迭時空服務器CPU芯片的RAS硬件方案主要圍繞SpacemiTX100Core、DDR控制器、PCIe控制器、片上互連總線等幾個核心部件展開。

(圖2:進迭時空RAS組件架構)

SpacemiT X100 Core 和 Cluster

- 實現L1/L2 Cache的Parity校驗和ECC,TLB 的Parity校驗,對于Parity錯誤和ECC不可糾正錯誤會進行Cachelineinvalid并Reload,對于ECC可糾正錯誤會進行數據回刷 (Scrubbing);

- 實現系統總線數據的Data check和Data poison檢測,在Core讀取Cache line時若檢測到數據錯誤則觸發異常中斷;

- 集成Core Boot MBIST,在啟動中測試CPU內部的所有RAM單元,若MBIST failed則通知系統啟動固件對Core進行隔離;

- 集成RISC-V規范RAS RERI接口模塊;

- 支持Warm Reset,允許在保留RAS錯誤信息的同時重啟CPU核。

DDR控制器

- 實現控制器端系統總線數據的Data check和Data poison;

- 實現控制器內部RAM的Parity校驗;

- 通過ECC機制實現對DRAM的命令式和自動式巡檢回刷 (Scrubbing);

- 對DRAM讀寫數據進行CRC校驗,若有錯誤自動Retry;

- 支持DDR5的EAPAR(Encoded Address Parity)機制;

- 支持72-bit和80-bit的DDR5 ECC DIMM,可以實現內存顆粒Chipkill功能;

- 支持對DRAM顆粒的PPR(Post Package Repair)修復功能。

PCIe控制器

實現控制器端系統總線數據的Data check和Data poison;

實現控制器內部RAM的Parity校驗;

支持傳輸層的ECRC校驗;

支持鏈接層的LCRC校驗;

在Lane training failed時,可以進行Lane isolation;

支持PCIe設備熱插拔。

片上互連總線

實現所有總線數據的Data check和Data poison;

實現互連總線的錯誤Response傳遞;

支持SLC和SF的RAMECC;

支持片間互連總線接口的ECRC和LCRC校驗。

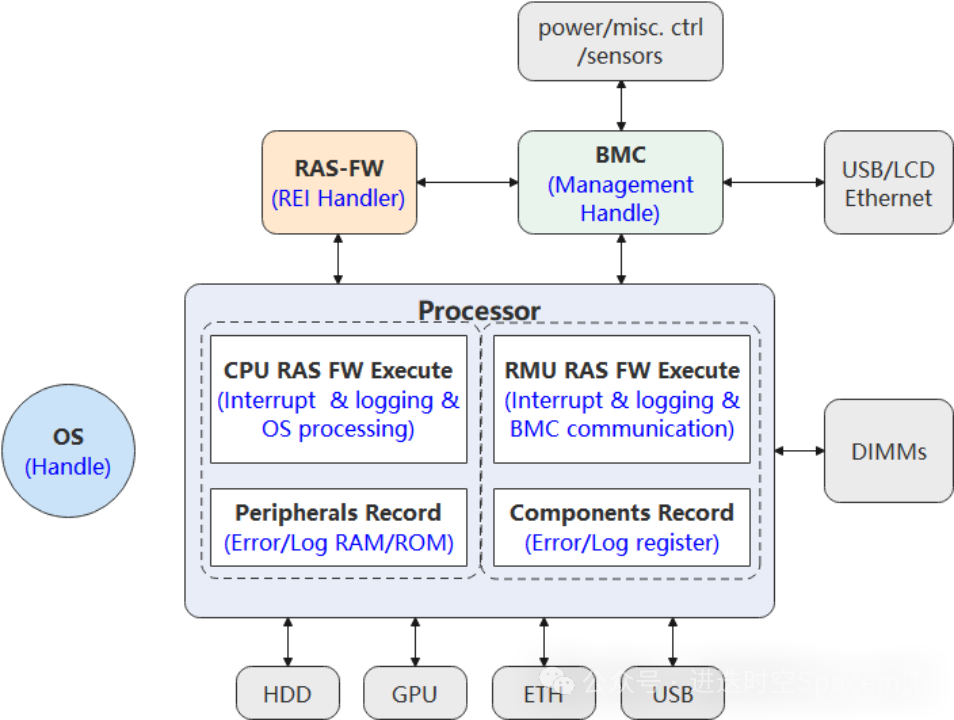

進迭時空RAS管理架構

(圖3:進迭時空RAS管理架構)

服務器CPU芯片對RAS信息的處理主要通過SpacemiT X100 Core 主CPU單元和RMU管理單元實現,兩者協同分工,實現了對本芯片中所有重要系統組件和多芯互連系統中其他芯片的RAS處理(如OS交互、BIOS固件執行、帶外BMC通信等),極大提升了RAS處理的可靠性,它的管理架構特性主要有:

SpacemiT X100 Core 支持RAS中斷接口,通過Cluster內部RERI模塊,實現符合RISC-V RERI規范的CPU核故障記錄和異常中斷;

PCIe支持符合規范的AER(Advanced Error Reporting);

通過CPU芯片的管理單元(RMU),實現整芯片RAS錯誤故障的異常處理:故障信息收集和存儲、故障的軟件通知和處理;

通過CPU芯片的帶外接口,實現BMC芯片的帶外RAS故障收集和交互。

進迭時空通過由RAS功能組件和RAS管理軟硬件架構協同組建的RAS系統,實現完整的RISC-V架構服務器RAS解決方案,即將推出業界首個完整支持服務器RAS的CPU產品。

文字:博志、風行、Stephen、hw、Zetalog審核:Sophie

-

cpu

+關注

關注

68文章

11040瀏覽量

216042 -

RISC-V

+關注

關注

46文章

2502瀏覽量

48292

發布評論請先 登錄

RISC-V 生態架構淺析

為什么選擇RISC-V?

科普RISC-V生態架構(認識RISC-V)

瑞薩基于RISC-V核心架構的預編程ASSP器件

ARM與RISC-V架構的區別是什么?

RISC-V 生態架構淺析

RISC-V架構簡介

談一談RISC-V架構的優勢和特點

兩大架構RISC-V 和 ARM 的各種關系

基于RISC-V開放架構的存算一體化芯片解決方案

RISC-V推動下的CPU架構變局

Imagination CPU 系列研討會 | RISC-V 平臺的性能分析和調試

RISC-V架構CPU的RAS解決方案

RISC-V架構CPU的RAS解決方案

評論