RISC-V 正受到整個(gè)半導(dǎo)體行業(yè)的關(guān)注。它提供了一個(gè)開(kāi)源解決方案的誘惑,任何人都可以利用它來(lái)創(chuàng)建自己的 CPU 或自定義加速器。

當(dāng)然,深入挖掘并出現(xiàn)挑戰(zhàn)。RISC-V 是新的,還沒(méi)有多年現(xiàn)場(chǎng)驗(yàn)證經(jīng)驗(yàn)的好處。這意味著精心選擇和執(zhí)行的 CPU 驗(yàn)證策略至關(guān)重要。這也意味著“黃金參考模型”的可用性是必須保護(hù)的關(guān)鍵組件。如果沒(méi)有已知的良好參考,就不可能對(duì)驗(yàn)證結(jié)果有信心。擁有自定義指令集模擬器 (ISS) 對(duì)成功至關(guān)重要。

CPU 設(shè)計(jì)和相關(guān)指令集架構(gòu) (ISA) 的正確驗(yàn)證是 CPU 核心工程組必須解決的最具挑戰(zhàn)性的活動(dòng)之一。與固定功能設(shè)計(jì)或模塊不同,CPU 是可編程的,旨在執(zhí)行許多不同的任務(wù)。最終,它是由其 ISA 的廣度和深度以及程序員利用 ISA 的不同方式來(lái)定義的。即使使用超級(jí)計(jì)算機(jī),考慮到指令、內(nèi)存利用率、數(shù)據(jù)模式等的所有組合,實(shí)現(xiàn)對(duì) CPU 的 100% 驗(yàn)證也需要數(shù)千年的時(shí)間。

相反,CPU 驗(yàn)證小組必須更聰明地工作,并專(zhuān)注于進(jìn)行“足夠”的驗(yàn)證以發(fā)現(xiàn)最有可能出現(xiàn)的問(wèn)題。“足夠”的定義基于特定的 CPU 和 ISA 變化——例如廣泛的功能集與狹窄的集中集——以及可能是安全關(guān)鍵或通用的最終應(yīng)用程序市場(chǎng),例如。

大型處理器公司花費(fèi)數(shù)年時(shí)間和數(shù)億美元為其特定處理器和指令集開(kāi)發(fā)驗(yàn)證流程和方法。他們從時(shí)間和經(jīng)驗(yàn)中受益,即便如此,多年來(lái)的顯著問(wèn)題表明,針對(duì)每種可能的情況驗(yàn)證 CPU 設(shè)計(jì)是多么困難。

在構(gòu)建用于 CPU 驗(yàn)證的方法、流程和工具集時(shí),RISC-V 設(shè)計(jì)和驗(yàn)證小組有很多選擇。例如,一些團(tuán)體可能更喜歡基于經(jīng)驗(yàn)的 Accellera 通用驗(yàn)證方法 (UVM) 標(biāo)準(zhǔn),而另一些團(tuán)體可能更喜歡 C。任何一種方法都是合適的。

同樣,在模擬平臺(tái)方面有多種選擇,通常根據(jù)經(jīng)驗(yàn)或已經(jīng)使用的模擬平臺(tái)做出決定。較新的公司權(quán)衡投資于 EDA 行業(yè)的事實(shí)上的標(biāo)準(zhǔn)模擬器或開(kāi)源模擬器(如 Verilator)的優(yōu)缺點(diǎn)。雖然沒(méi)有任何答案適用于所有情況,但在前進(jìn)之前就驗(yàn)證環(huán)境達(dá)成一致是必須的。

該流程的另一個(gè)關(guān)鍵組成部分是所選 ISA 的 CPU 參考模型。可能很容易認(rèn)為它可以在內(nèi)部開(kāi)發(fā),這是一個(gè)固有的風(fēng)險(xiǎn)提議。開(kāi)發(fā) CPU 是一項(xiàng)艱巨的任務(wù)。最好尋找一個(gè)經(jīng)過(guò)驗(yàn)證的外部參考模型,即驗(yàn)證 CPU 和 ISA 所依據(jù)的“黃金”標(biāo)準(zhǔn)。

裝備驗(yàn)證流程

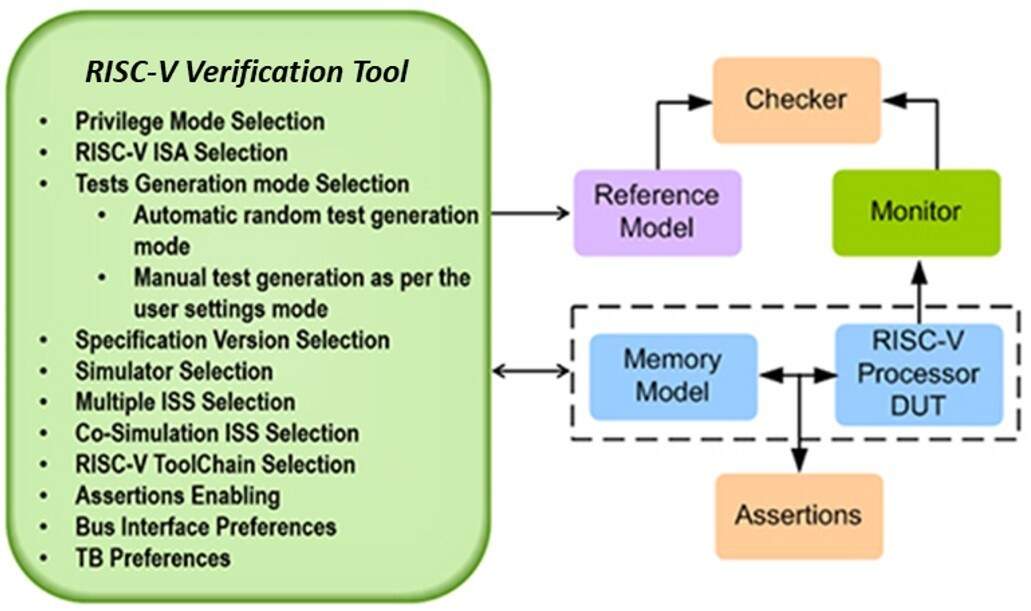

RISC-V 驗(yàn)證流程應(yīng)包含大量組件,以確保 RISC-V CPU 開(kāi)發(fā)人員實(shí)現(xiàn)其驗(yàn)證目標(biāo)。(圖片:SmartDV)

有了這么長(zhǎng)的標(biāo)準(zhǔn)列表,確定一個(gè)符合所有條件的驗(yàn)證流程似乎是一項(xiàng)無(wú)望的任務(wù)。一個(gè) RISC-V CPU 驗(yàn)證平臺(tái)是一個(gè)完整的環(huán)境,用于嚴(yán)格驗(yàn)證基于 RISC-V 的新 CPU 設(shè)計(jì),專(zhuān)門(mén)為 RISC-V CPU 開(kāi)發(fā)人員實(shí)現(xiàn)對(duì)其設(shè)計(jì)的全面驗(yàn)證。它與 SystemVerilog/UVM 和基于 C 的流程以及所有行業(yè)標(biāo)準(zhǔn)的模擬器和 Verilator 兼容。支持所有 RISC-V ISA 的測(cè)試套件以及經(jīng)過(guò)驗(yàn)證的黃金參考模型。

RISC-V CPU 或定制加速器的商業(yè)驗(yàn)證流程將為驗(yàn)證組提供對(duì)其驗(yàn)證結(jié)果的急需信心,并創(chuàng)造開(kāi)放式協(xié)作和創(chuàng)新。

-

處理器

+關(guān)注

關(guān)注

68文章

19793瀏覽量

233404 -

cpu

+關(guān)注

關(guān)注

68文章

11029瀏覽量

215860 -

可編程

+關(guān)注

關(guān)注

2文章

1033瀏覽量

40390 -

RISC-V

+關(guān)注

關(guān)注

46文章

2474瀏覽量

48217

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA與RISC-V淺談

RISC-V MCU技術(shù)

RISC-V架構(gòu)及MRS開(kāi)發(fā)環(huán)境回顧

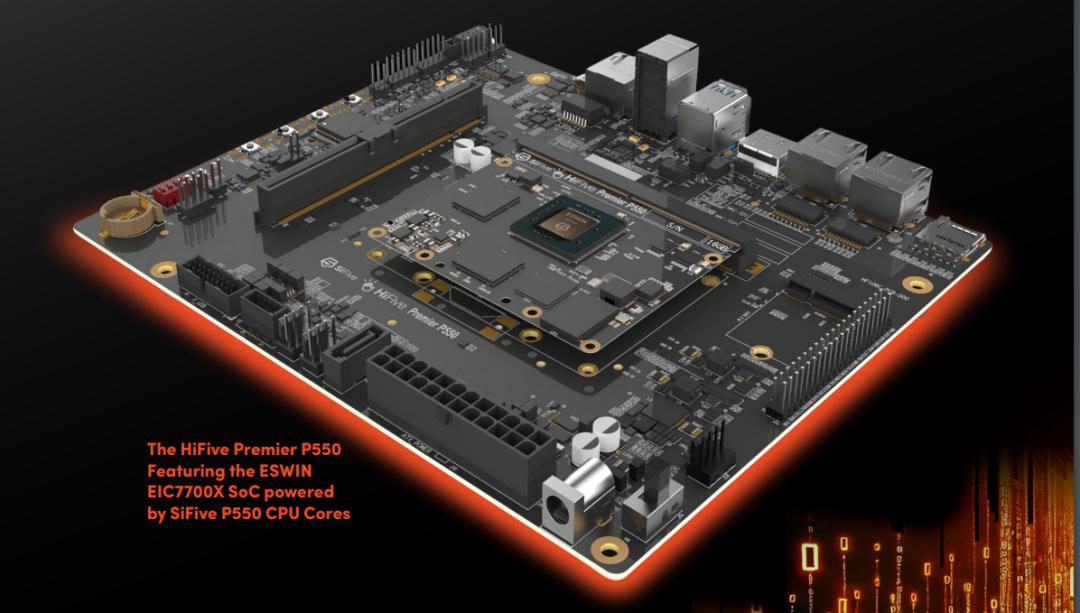

SiFive 推出高性能 Risc-V CPU 開(kāi)發(fā)板 HiFive Premier P550

《RISC-V能否復(fù)制Linux 的成功?》

RISC-V,即將進(jìn)入應(yīng)用的爆發(fā)期

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來(lái) !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

思爾芯亮相RISC-V中國(guó)峰會(huì),展示架構(gòu)建模與混合仿真驗(yàn)證方法

2024 RISC-V 中國(guó)峰會(huì):華秋電子助力RISC-V生態(tài)!

2024 RISC-V 中國(guó)峰會(huì):華秋電子助力RISC-V生態(tài)!

Imagination CPU 系列研討會(huì) | RISC-V 平臺(tái)的性能分析和調(diào)試

RISC-V的 CPU 驗(yàn)證挑戰(zhàn)

RISC-V的 CPU 驗(yàn)證挑戰(zhàn)

評(píng)論