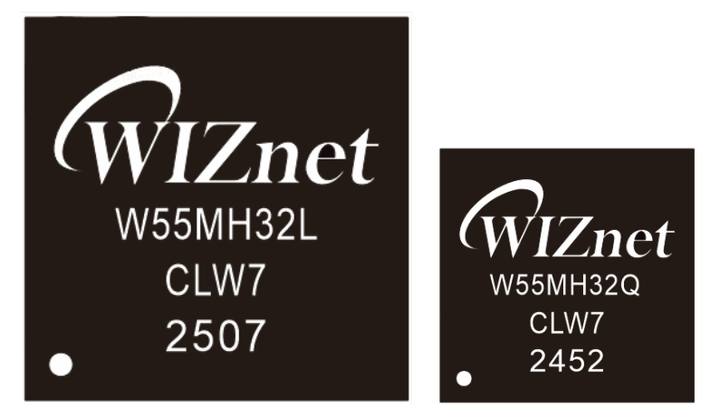

單芯片解決方案,開啟全新體驗——W55MH32 高性能以太網單片機

W55MH32是WIZnet重磅推出的高性能以太網單片機,它為用戶帶來前所未有的集成化體驗。這顆芯片將強大的組件集于一身,具體來說,一顆W55MH32內置高性能Arm? Cortex-M3核心,其主頻最高可達216MHz;配備1024KB FLASH與96KB SRAM,滿足存儲與數據處理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP協議棧、內置MAC以及PHY,擁有獨立的32KB以太網收發緩存,可供8個獨立硬件socket使用。如此配置,真正實現了All-in-One解決方案,為開發者提供極大便利。

在封裝規格上,W55MH32 提供了兩種選擇:QFN68和QFN100。

W55MH32Q采用QFN68封裝版本,尺寸為8x8mm,它擁有36個GPIO、3個ADC、12通道DMA、17個定時器、2個I2C、3個串口、2個SPI接口(其中1個帶I2S接口復用)、1個CAN以及1個USB2.0。在保持與同系列其他版本一致的核心性能基礎上,僅減少了部分GPIO以及SDIO接口,其他參數保持一致,性價比優勢顯著,尤其適合網關模組等對空間布局要求較高的場景。緊湊的尺寸和精簡化外設配置,使其能夠在有限空間內實現高效的網絡連接與數據交互,成為物聯網網關、邊緣計算節點等緊湊型設備的理想選擇。 同系列還有QFN100封裝的W55MH32L版本,該版本擁有更豐富的外設資源,適用于需要多接口擴展的復雜工控場景,軟件使用方法一致。

此外,本W55MH32支持硬件加密算法單元,WIZnet還推出TOE+SSL應用,涵蓋TCP SSL、HTTP SSL以及MQTT SSL等,為網絡通信安全再添保障。

為助力開發者快速上手與深入開發,基于W55MH32Q這顆芯片,WIZnet精心打造了配套開發板。開發板集成WIZ-Link芯片,借助一根USB C口數據線,就能輕松實現調試、下載以及串口打印日志等功能。開發板將所有外設全部引出,拓展功能也大幅提升,便于開發者全面評估芯片性能。

第十一章 通用定時器(上篇)

W55MH32的通用定時器為TIM2~TIM5/TIM9~TIM14,由于篇幅有限,這里我們講解TIM2~TIM5的相關功能,對于通用定時器TIM9~TIM14,感興趣的朋友查閱《W55MH32參考手冊》使用方法一致,功能上存在些許差異,掌握了方法之后都是一通百通的。

本章分為如下幾個小節:

1 通用定時器概述

2 程序設計

3 下載驗證

1 通用定時器概述

1.1 通用定時器簡介

通用定時器是一個通過可編程預分頻器驅動的 16 位自動裝載計數器構成。它適用于多種場合,包括測量輸入信號的脈沖長度(輸入捕獲)或者產生輸出波形(輸出比較和PWM)。使用定時器預分頻器和 RCC 時鐘控制器預分頻器,脈沖長度和波形周期可以在幾個微秒到幾個 毫秒間調整。每個定時器都是完全獨立的,沒有互相共享任何資源。

1.2 主要功能

通用TIMx (TIM2、TIM3、TIM4和TIM5)定時器功能包括:

?16位向上、向下、向上/向下自動裝載計數器

?16位可編程(可以實時修改)預分頻器,計數器時鐘頻率的分頻系數為1~65536之間的任意 數值

?4個獨立通道:

······輸入捕獲

······輸出比較

······PWM生成(邊緣或中間對齊模式)

······單脈沖模式輸出

?使用外部信號控制定時器和定時器互連的同步電路

?如下事件發生時產生中斷/DMA:

······更新:計數器向上溢出/向下溢出,計數器初始化(通過軟件或者內部/外部觸發)

······觸發事件(計數器啟動、停止、初始化或者由內部/外部觸發計數)

······輸入捕獲

······輸出比較

?觸發輸入作為外部時鐘或者按周期的電流管理

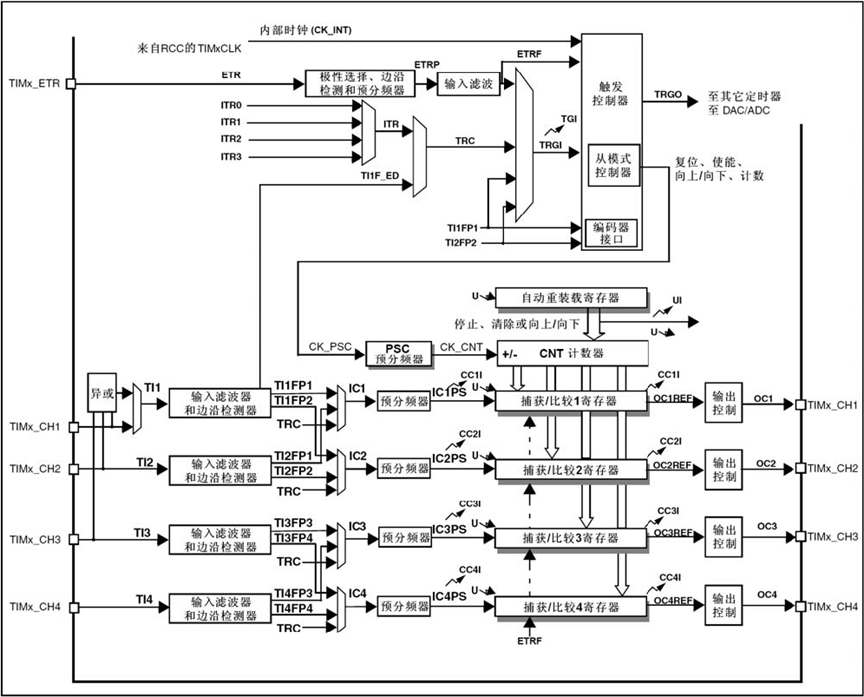

通用定時器框圖如下:

1.3 功能描述

1.3.1時基單元

可編程通用定時器的主要部分是一個16位計數器和與其相關的自動裝載寄存器。這個計數器可以向上計數、向下計數或者向上向下雙向計數。此計數器時鐘由預分頻器分頻得到。

計數器、自動裝載寄存器和預分頻器寄存器可以由軟件讀寫,在計數器運行時仍可以讀寫。時基單元包含:

?計數器寄存器(TIMx_CNT)

?預分頻器寄存器 (TIMx_PSC)

?自動裝載寄存器 (TIMx_ARR)

自動裝載寄存器是預先裝載的,寫或讀自動重裝載寄存器將訪問預裝載寄存器。根據在 TIMx_CR1寄存器中的自動裝載預裝載使能位(ARPE)的設置,預裝載寄存器的內容被立即或在 每次的更新事件UEV時傳送到影子寄存器。當計數器達到溢出條件(向下計數時的下溢條件)并當 TIMx_CR1寄存器中的UDIS位等于'0'時,產生更新事件。更新事件也可以由軟件產生。隨后會詳細描述每一種配置下更新事件的產生。

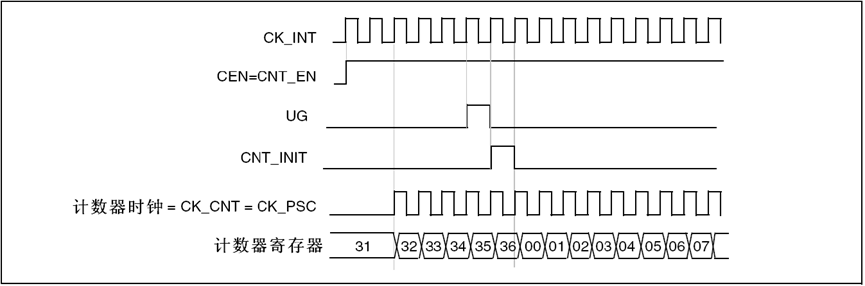

計數器由預分頻器的時鐘輸出CK_CNT驅動,僅當設置了計數器TIMx_CR1寄存器中的計數器使能位(CEN)時,CK_CNT才有效。(有關計數器使能的細節,請參見控制器的從模式描述)。

注:真正的計數器使能信號CNT_EN是在CEN的一個時鐘周期后被設置。

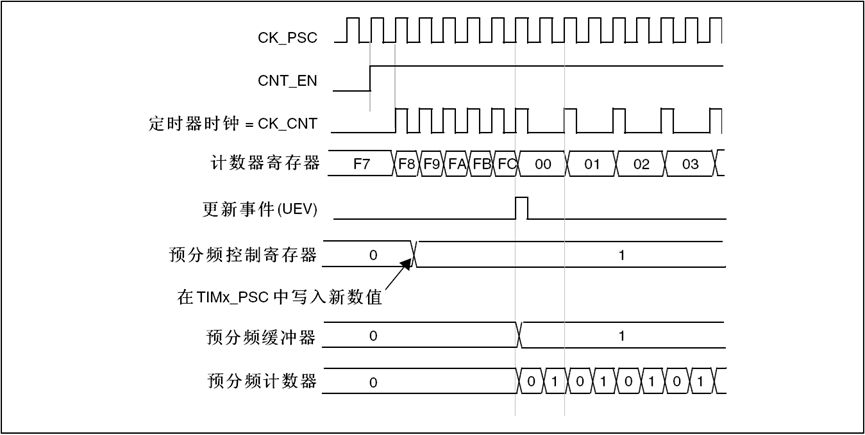

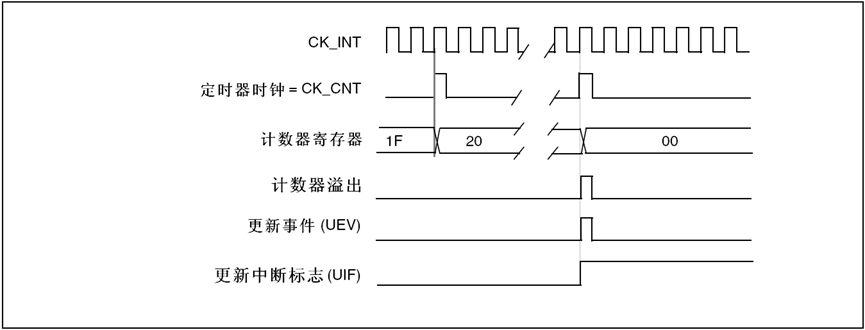

預分頻器描述

預分頻器可以將計數器的時鐘頻率按1到65536之間的任意值分頻。它是基于一個(在TIMx_PSC 寄存器中的)16位寄存器控制的16位計數器。這個控制寄存器帶有緩沖器,它能夠在工作時被改 變。新的預分頻器參數在下一次更新事件到來時被采用。

下面出了在預分頻器運行時,更改計數器參數的例子:

當預分頻器的參數從1變到2時,計數器的時序圖

當預分頻器的參數從1變到4時,計數器的時序圖

1.3.2計數器模式

向上計數模式

在向上計數模式中,計數器從0計數到自動加載值(TIMx_ARR計數器的內容),然后重新從0開始 計數并且產生一個計數器溢出事件。

每次計數器溢出時可以產生更新事件,在TIMx_EGR寄存器中(通過軟件方式或者使用從模式控 制器)設置UG位也同樣可以產生一個更新事件。

設置TIMx_CR1寄存器中的UDIS位,可以禁止更新事件;這樣可以避免在向預裝載寄存器中寫 入新值時更新影子寄存器。在UDIS位被清'0'之前,將不產生更新事件。但是在應該產生更新事 件時,計數器仍會被清'0',同時預分頻器的計數也被請0(但預分頻系數不變)。此外,如果設置 了TIMx_CR1寄存器中的URS位(選擇更新請求),設置UG位將產生一個更新事件UEV,但硬件 不設置UIF標志(即不產生中斷或DMA請求);這是為了避免在捕獲模式下清除計數器時,同時產 生更新和捕獲中斷。

當發生一個更新事件時,所有的寄存器都被更新,硬件同時(依據URS位)設置更新標志位 (TIMx_SR寄存器中的UIF位)。

?預分頻器的緩沖區被置入預裝載寄存器的值(TIMx_PSC寄存器的內容)。

?自動裝載影子寄存器被重新置入預裝載寄存器的值(TIMx_ARR)。

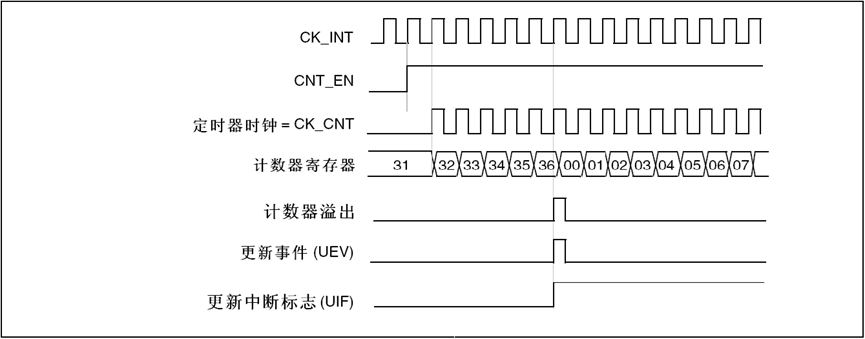

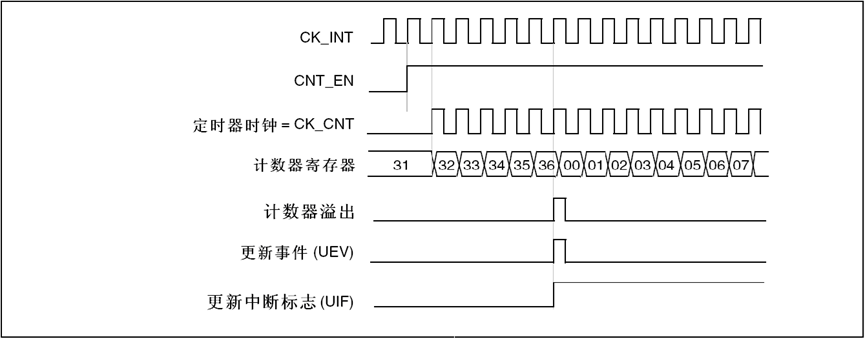

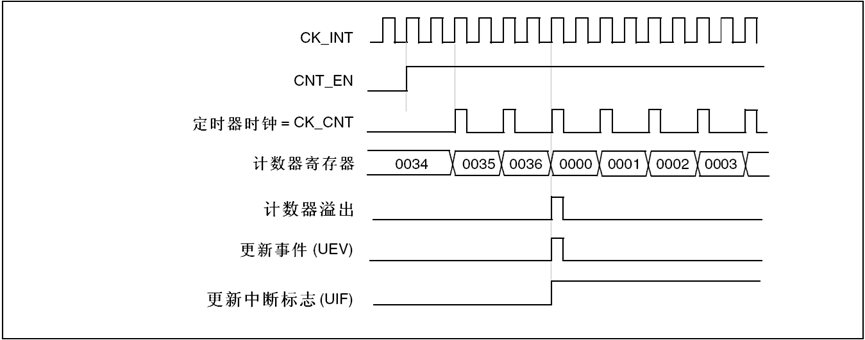

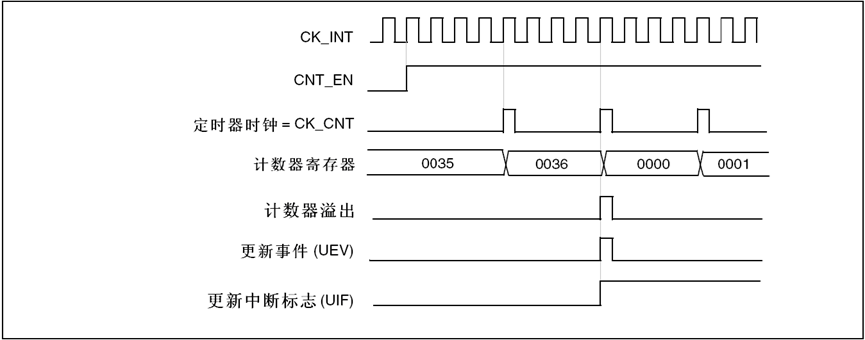

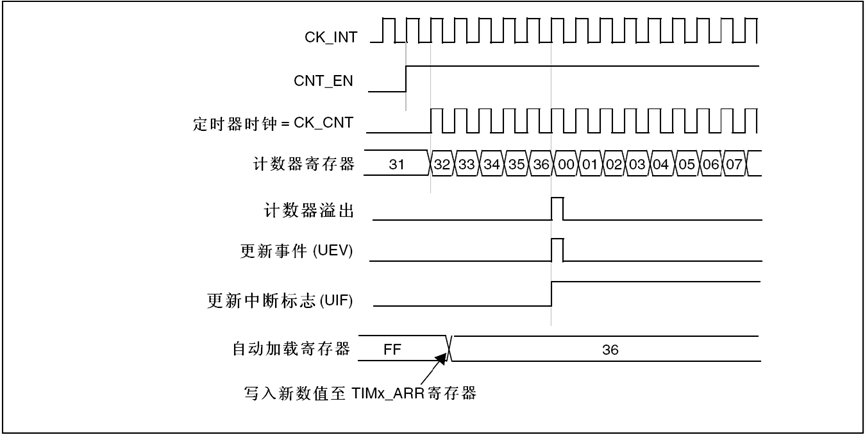

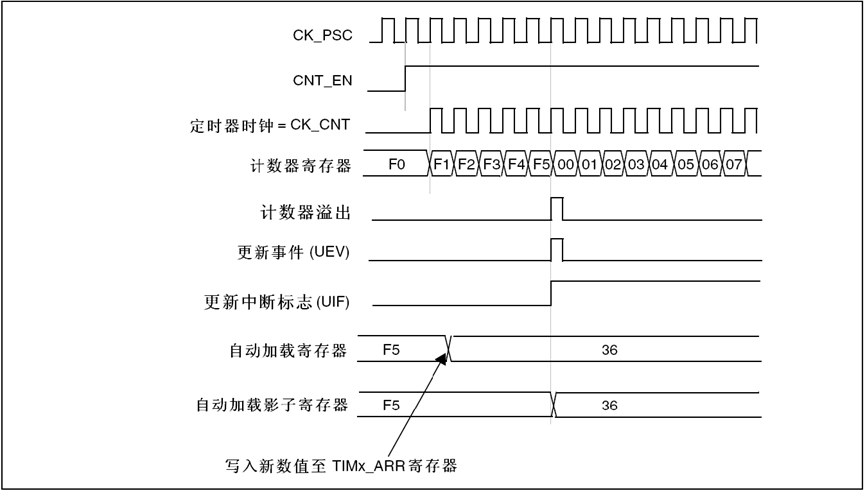

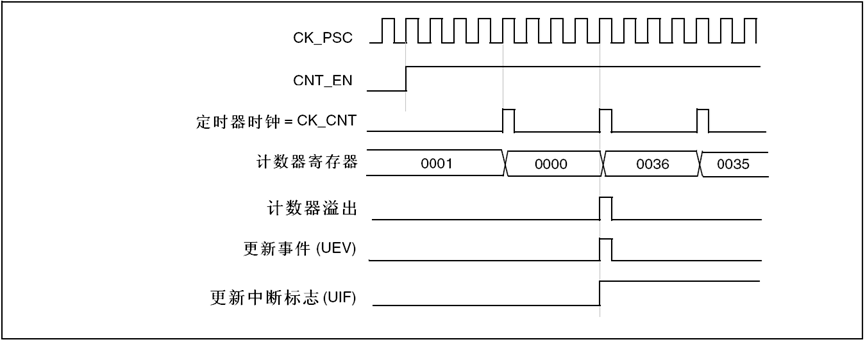

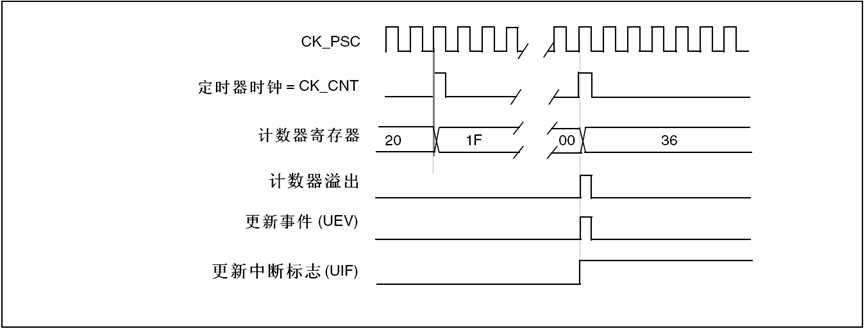

下圖給出一些例子,當TIMx_ARR=0x36時計數器在不同時鐘頻率下的動作:

計數器時序圖,內部時鐘分頻因子為1

計數器時序圖,內部時鐘分頻因子為2

計數器時序圖,內部時鐘分頻因子為4

計數器時序圖,內部時鐘分頻因子為N

計數器時序圖,當ARPE=0時的更新事件(TIMx_ARR沒有預裝入)

計數器時序圖,當ARPE=1時的更新事件(預裝入了TIMx_ARR)

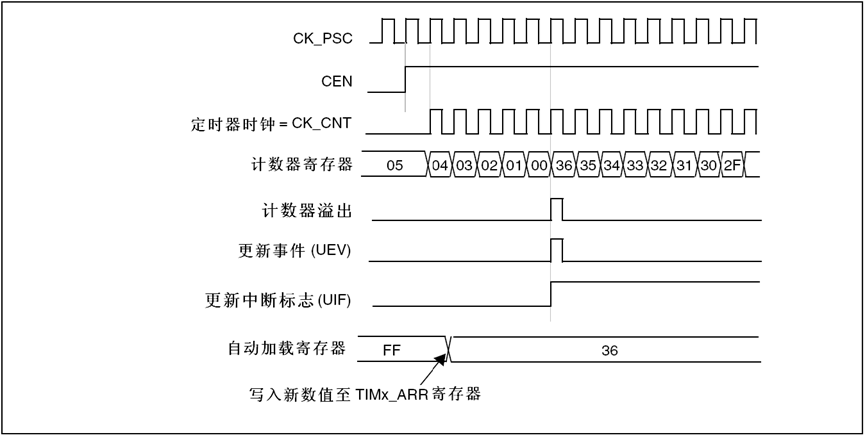

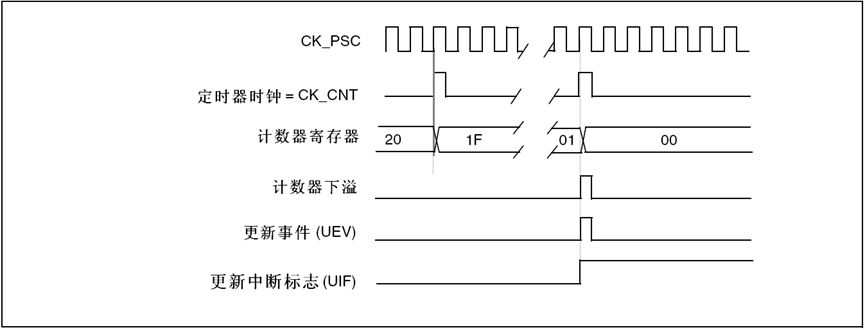

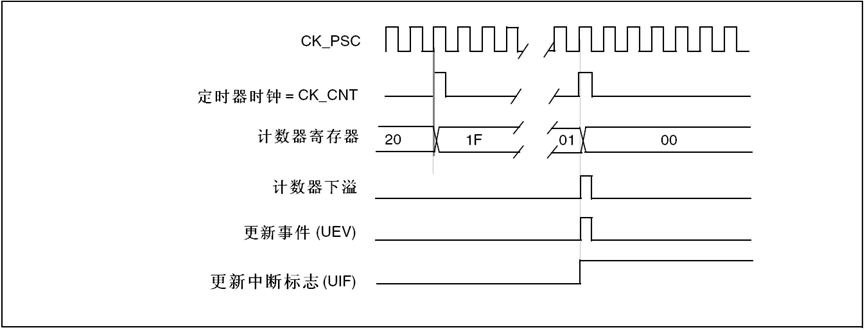

向下計數模式

在向下模式中,計數器從自動裝入的值(TIMx_ARR計數器的值)開始向下計數到0,然后從自動 裝入的值重新開始并且產生一個計數器向下溢出事件。

每次計數器溢出時可以產生更新事件,在TIMx_EGR寄存器中(通過軟件方式或者使用從模式控 制器)設置UG位,也同樣可以產生一個更新事件。

設置TIMx_CR1寄存器的UDIS位可以禁止UEV事件。這樣可以避免向預裝載寄存器中寫入新值 時更新影子寄存器。因此UDIS位被清為'0'之前不會產生更新事件。然而,計數器仍會從當前自 動加載值重新開始計數,同時預分頻器的計數器重新從0開始(但預分頻系數不變)。

此外,如果設置了TIMx_CR1寄存器中的URS位(選擇更新請求) ,設置UG位將產生一個更新事 件UEV但不設置UIF標志(因此不產生中斷和DMA請求),這是為了避免在發生捕獲事件并清除計 數器時,同時產生更新和捕獲中斷。

當發生更新事件時,所有的寄存器都被更新,并且(根據URS位的設置)更新標志位(TIMx_SR寄 存器中的UIF位)也被設置。

?預分頻器的緩存器被置入預裝載寄存器的值(TIMx_PSC寄存器的值)。

?當前的自動加載寄存器被更新為預裝載值(TIMx_ARR寄存器中的內容) 。

注:自動裝載在計 數器重載入之前被更新,因此下一個周期將是預期的值。

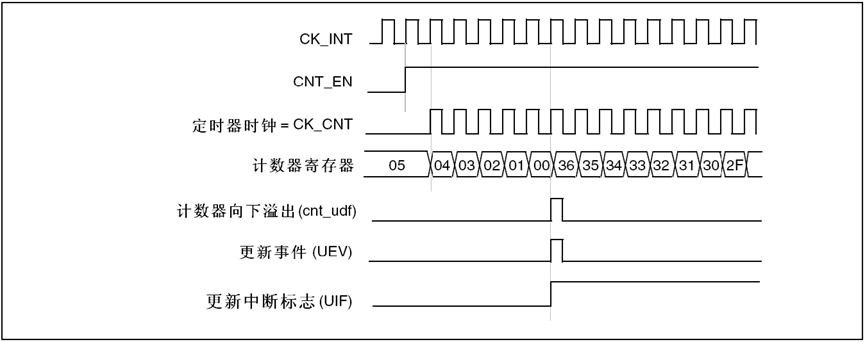

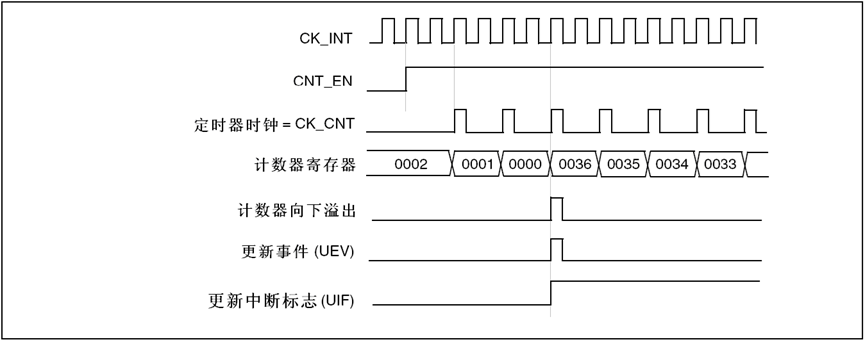

以下是一些當TIMx_ARR=0x36時,計數器在不同時鐘頻率下的操作例子。

計數器時序圖,內部時鐘分頻因子為1

計數器時序圖,內部時鐘分頻因子為2

計數器時序圖,內部時鐘分頻因子為4

計數器時序圖,內部時鐘分頻因子為N

計數器時序圖,當沒有使用重復計數器時的更新事件

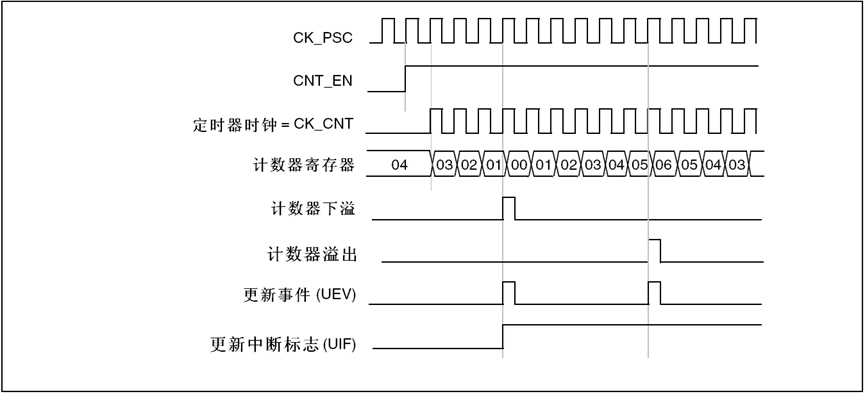

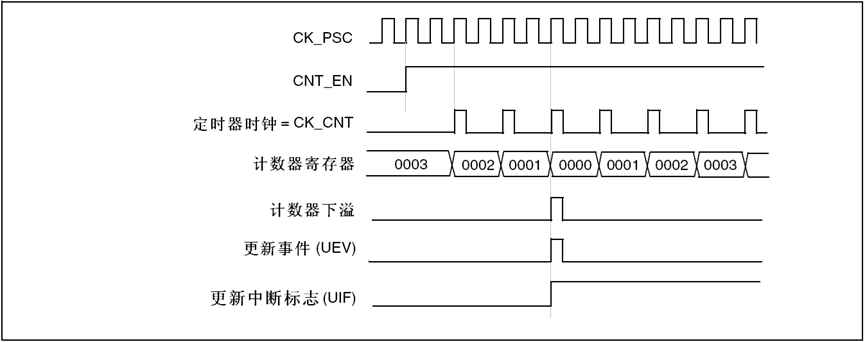

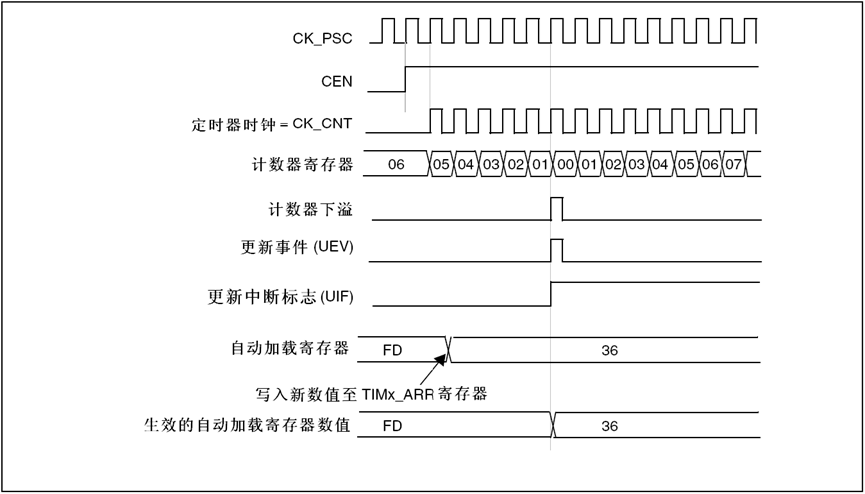

中央對齊模式(向上/向下計數)

在中央對齊模式,計數器從0開始計數到自動加載的值(TIMx_ARR寄存器)-1,產生一個計數器 溢出事件,然后向下計數到1并且產生一個計數器下溢事件;然后再從0開始重新計數。

在這個模式,不能寫入TIMx_CR1中的DIR方向位。它由硬件更新并指示當前的計數方向。

可以在每次計數上溢和每次計數下溢時產生更新事件;也可以通過(軟件或者使用從模式控制器) 設置TIMx_EGR寄存器中的UG位產生更新事件。然后,計數器重新從0開始計數,預分頻器也 重新從0開始計數。

設置TIMx_CR1寄存器中的UDIS位可以禁止UEV事件。這樣可以避免在向預裝載寄存器中寫入 新值時更新影子寄存器。因此UDIS位被清為'0'之前不會產生更新事件。然而,計數器仍會根據 當前自動重加載的值,繼續向上或向下計數。

此外,如果設置了TIMx_CR1寄存器中的URS位(選擇更新請求) ,設置UG位將產生一個更新事 件UEV但不設置UIF標志(因此不產生中斷和DMA請求),這是為了避免在發生捕獲事件并清除計 數器時,同時產生更新和捕獲中斷。

當發生更新事件時,所有的寄存器都被更新,并且(根據URS位的設置)更新標志位(TIMx_SR寄 存器中的UIF位)也被設置。

?預分頻器的緩存器被加載為預裝載(TIMx_PSC寄存器)的值。

?當前的自動加載寄存器被更新為預裝載值(TIMx_ARR寄存器中的內容)。

注:如果因為計數 器溢出而產生更新,自動重裝載將在計數器重載入之前被更新,因此下一個周期將是預期 的值(計數器被裝載為新的值)。

以下是一些計數器在不同時鐘頻率下的操作的例子:

計數器時序圖,內部時鐘分頻因子為1,TIMx_ARR=0x6

1.這里使用了中心對齊模式1。

計數器時序圖,內部時鐘分頻因子為2

計數器時序圖,內部時鐘分頻因子為4,TIMx_ARR=0x36

計數器時序圖,內部時鐘分頻因子為N

計數器時序圖,ARPE=1時的更新事件(計數器下溢)

計數器時序圖,ARPE=1時的更新事件(計數器溢出)

1.3.3時鐘選擇

計數器時鐘可由下列時鐘源提供:

?內部時鐘(CK_INT)

?外部時鐘模式1:外部輸入腳(TIx)

?外部時鐘模式2:外部觸發輸入(ETR)

?內部觸發輸入(ITRx):使用一個定時器作為另一個定時器的預分頻器,如可以配置一個定時器Timer1而作為另一個定時器Timer2的預分頻器。

內部時鐘源(CK_INT)

如果禁止了從模式控制器(TIMx_SMCR寄存器的SMS=000),則CEN 、DIR(TIMx_CR1寄存器) 和UG位(TIMx_EGR寄存器)是事實上的控制位,并且只能被軟件修改(UG位仍被自動清除)。只 要CEN位被寫成'1',預分頻器的時鐘就由內部時鐘CK_INT提供。

下圖顯示了控制電路和向上計數器在一般模式下,不帶預分頻器時的操作:

一般模式下的控制電路,內部時鐘分頻因子為1

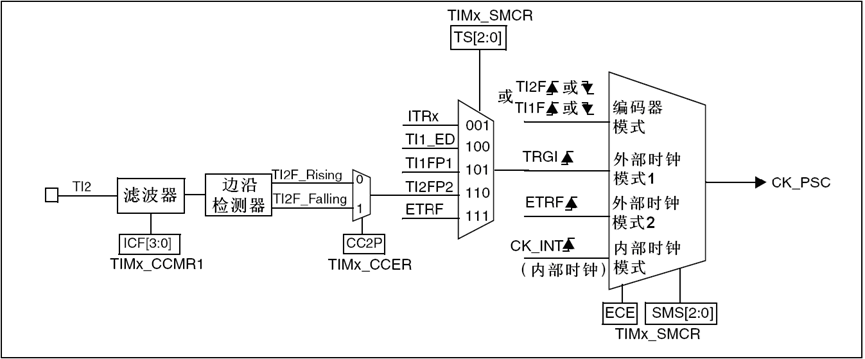

外部時鐘源模式1

當TIMx_SMCR寄存器的SMS=111時,此模式被選中。計數器可以在選定輸入端的每個上升沿 或下降沿計數。

TI2外部時鐘連接例子

例如,要配置向上計數器在T12輸入端的上升沿計數,使用下列步驟:

1.配置TIMx_CCMR1寄存器CC2S='01',配置通道2檢測TI2輸入的上升沿。

2.配置TIMx_CCMR1寄存器的IC2F[3:0],選擇輸入濾波器帶寬(如果不需要濾波器,保持 IC2F=0000)。

注:捕獲預分頻器不用作觸發,所以不需要對它進行配置。

3.配置TIMx_CCER寄存器的CC2P='0',選定上升沿極性。

4.配置TIMx_SMCR寄存器的SMS='111',選擇定時器外部時鐘模式1。

5.配置TIMx_SMCR寄存器中的TS='110',選定TI2作為觸發輸入源。

6.設置TIMx_CR1寄存器的CEN='1',啟動計數器。

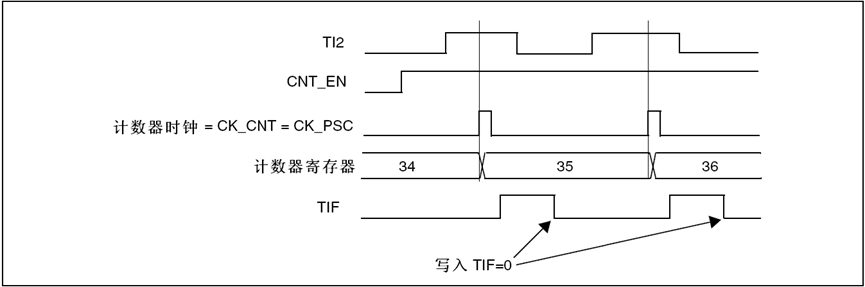

當上升沿出現在TI2,計數器計數一次,且TIF標志被設置。

在TI2的上升沿和計數器實際時鐘之間的延時,取決于在TI2輸入端的重新同步電路。

外部時鐘模式1下的控制電路

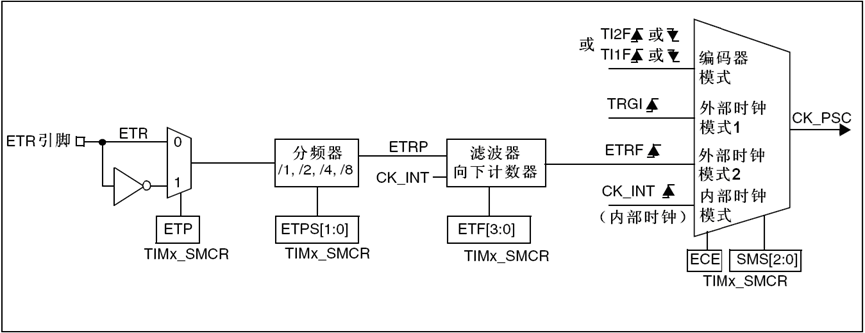

外部時鐘源模式2

選定此模式的方法為:令TIMx_SMCR寄存器中的ECE=1 計數器能夠在外部觸發ETR的每一個上升沿或下降沿計數。 下圖是外部觸發輸入的框圖:

外部觸發輸入框圖

例如,要配置在ETR下每2個上升沿計數一次的向上計數器,使用下列步驟:

1.本例中不需要濾波器,置TIMx_SMCR寄存器中的ETF[3:0]=0000

2.設置預分頻器,置TIMx_SMCR寄存器中的ETPS[1:0]=01

3.設置在ETR的上升沿檢測,置TIMx_SMCR寄存器中的ETP=0

4.開啟外部時鐘模式2,置TIMx_SMCR寄存器中的ECE=1

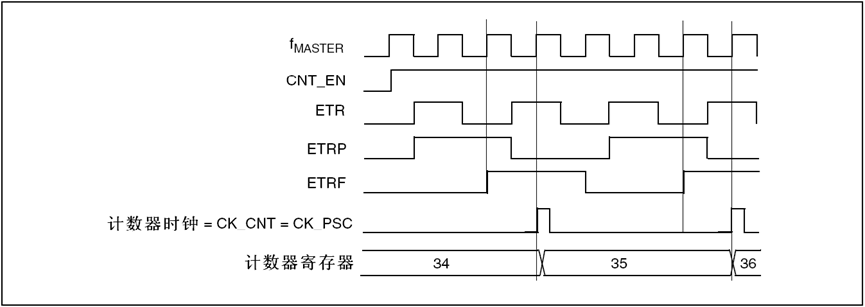

5.啟動計數器,置TIMx_CR1寄存器中的CEN=1 計數器在每2個ETR上升沿計數一次。

在ETR的上升沿和計數器實際時鐘之間的延時取決于在ETRP信號端的重新同步電路。

外部時鐘模式2下的控制電路

1.3.4捕獲/比較通道

每一個捕獲/比較通道都是圍繞著一個捕獲/比較寄存器(包含影子寄存器),包括捕獲的輸入部分

(數字濾波、多路復用和預分頻器),和輸出部分(比較器和輸出控制)。 下面幾張圖是一個捕獲/比較通道概覽。

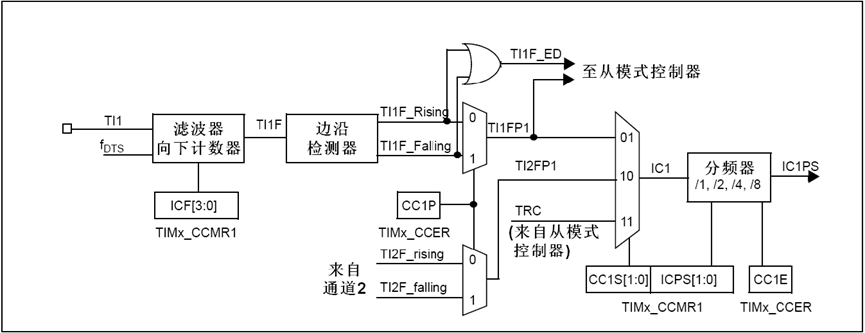

輸入部分對相應的TIx輸入信號采樣,并產生一個濾波后的信號TIxF。然后,一個帶極性選擇的 邊緣檢測器產生一個信號(TIxFPx),它可以作為從模式控制器的輸入觸發或者作為捕獲控制。該 信號通過預分頻進入捕獲寄存器(ICxPS)。

捕獲/比較通道(如:通道1輸入部分)

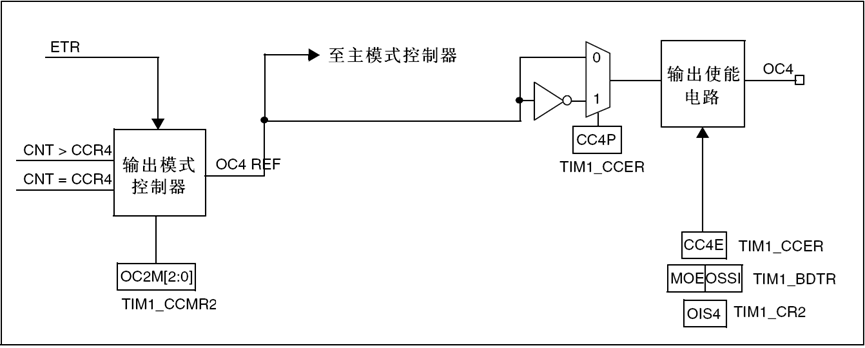

輸出部分產生一個中間波形OCxRef(高有效)作為基準,鏈的末端決定最終輸出信號的極性。

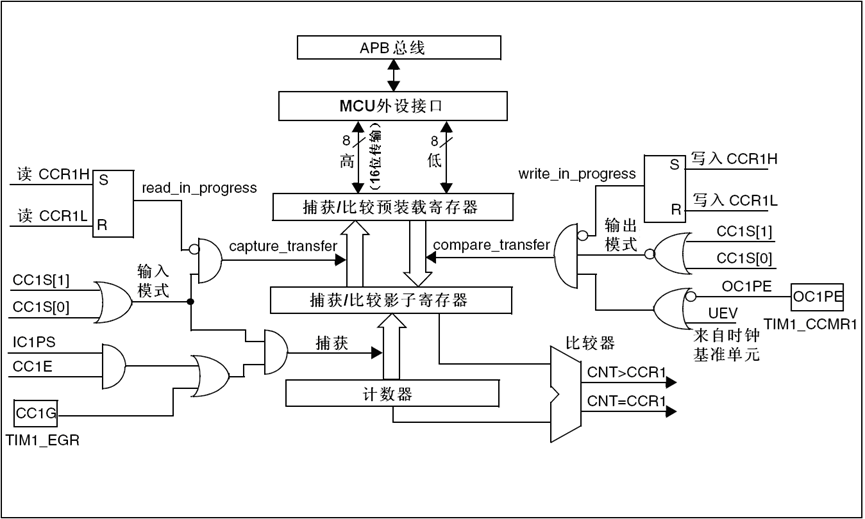

捕獲/比較通道1的主電路

捕獲/比較通道的輸出部分(通道1)

捕獲/比較模塊由一個預裝載寄存器和一個影子寄存器組成。讀寫過程僅操作預裝載寄存器。

在捕獲模式下,捕獲發生在影子寄存器上,然后再復制到預裝載寄存器中。

在比較模式下,預裝載寄存器的內容被復制到影子寄存器中,然后影子寄存器的內容和計數器進行比較。

1.3.5輸入捕獲模式

在輸入捕獲模式下,當檢測到ICx信號上相應的邊沿后,計數器的當前值被鎖存到捕獲/比較寄存 器(TIMx_CCRx)中。當捕獲事件發生時,相應的CCxIF標志(TIMx_SR寄存器)被置'1',如果使能 了中斷或者DMA操作, 則將產生中斷或者DMA操作。如果捕獲事件發生時CCxIF標志已經為 高,那么重復捕獲標志CCxOF(TIMx_SR寄存器)被置'1'。寫CCxIF=0可清除CCxIF,或讀取存 儲在TIMx_CCRx寄存器中的捕獲數據也可清除CCxIF。寫CCxOF=0可清除CCxOF。

以下例子說明如何在TI1輸入的上升沿時捕獲計數器的值到TIMx_CCR1寄存器中,步驟如下:

?選擇有效輸入端:TIMx_CCR1必須連接到TI1輸入,所以寫入TIMx_CCR1寄存器中的 CC1S=01,只要CC1S不為'00',通道被配置為輸入,并且TM1_CCR1寄存器變為只讀。

?根據輸入信號的特點,配置輸入濾波器為所需的帶寬(即輸入為TIx時,輸入濾波器控制位是 TIMx_CCMRx寄存器中的ICxF位)。假設輸入信號在最多5個內部時鐘周期的時間內抖動, 我們須配置濾波器的帶寬長于5個時鐘周期。因此我們可以(以fDTS頻率)連續采樣8次,以確 認在TI1上一次真實的邊沿變換,即在TIMx_CCMR1寄存器中寫入IC1F=0011。

?選擇TI1通道的有效轉換邊沿,在TIMx_CCER寄存器中寫入CC1P=0(上升沿)。

?配置輸入預分頻器。在本例中,我們希望捕獲發生在每一個有效的電平轉換時刻,因此預分頻器被禁止(寫TIMx_CCMR1寄存器的IC1PS=00)。

?設置TIMx_CCER寄存器的CC1E=1,允許捕獲計數器的值到捕獲寄存器中。

?如果需要,通過設置TIMx_DIER寄存器中的CC1IE位允許相關中斷請求,通過設置 TIMx_DIER寄存器中的CC1DE位允許DMA請求。

當發生一個輸入捕獲時:

?產生有效的電平轉換時,計數器的值被傳送到TIMx_CCR1寄存器。

?CC1IF標志被設置(中斷標志)。當發生至少2個連續的捕獲時,而CC1IF未曾被清除, CC1OF也被置'1'。

?如設置了CC1IE位,則會產生一個中斷。

?如設置了CC1DE位,則還會產生一個DMA請求。

為了處理捕獲溢出,建議在讀出捕獲溢出標志之前讀取數據,這是為了避免丟失在讀出捕獲溢出標志之后和讀取數據之前可能產生的捕獲溢出信息。

注:設置TIMx_EGR寄存器中相應的CCxG位,可以通過軟件產生輸入捕獲中斷和/或DMA請求。

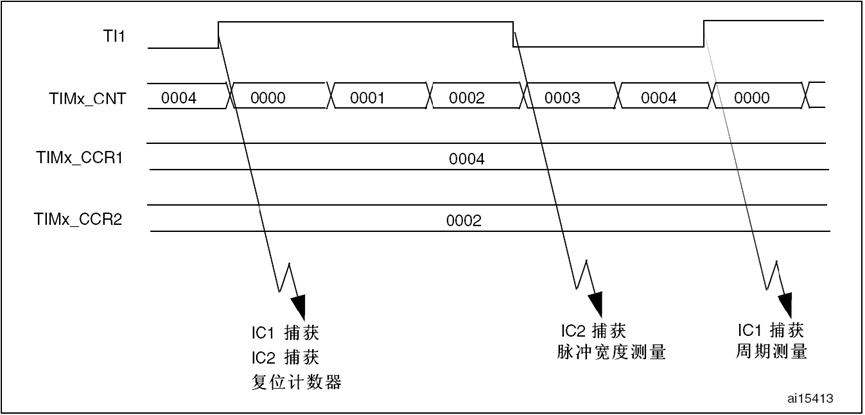

1.3.6PWM輸入模式

該模式是輸入捕獲模式的一個特例,除下列區別外,操作與輸入捕獲模式相同:

?兩個ICx信號被映射至同一個TIx輸入。

?這2個ICx信號為邊沿有效,但是極性相反。

?其中一個TIxFP信號被作為觸發輸入信號,而從模式控制器被配置成復位模式。

例如,你需要測量輸入到TI1上的PWM信號的長度(TIMx_CCR1寄存器)和占空比(TIMx_CCR2 寄存器),具體步驟如下(取決于CK_INT的頻率和預分頻器的值)。

?選擇TIMx_CCR1的有效輸入:置TIMx_CCMR1寄存器的CC1S=01(選擇TI1)。

?選擇TI1FP1的有效極性(用來捕獲數據到TIMx_CCR1中和清除計數器):置CC1P=0(上升沿 有效)。

?選擇TIMx_CCR2的有效輸入:置TIMx_CCMR1寄存器的CC2S=10(選擇TI1)。

?選擇TI1FP2的有效極性(捕獲數據到TIMx_CCR2):置CC2P=1(下降沿有效)。

?選擇有效的觸發輸入信號:置TIMx_SMCR寄存器中的TS=101(選擇TI1FP1)。

?配置從模式控制器為復位模式:置TIMx_SMCR中的SMS=100。

?使能捕獲:置TIMx_CCER寄存器中CC1E=1且CC2E=1。

PWM輸入模式時序

由于只有TI1FP1 和TI2FP2 連到了從模式控制器 ,所以 PWM 輸入模式只能使用TIMx_CH1 /TIMx_CH2信號。

1.3.7強置輸出模式

在輸出模式(TIMx_CCMRx寄存器中CCxS=00)下,輸出比較信號(OCxREF和相應的OCx)能夠 直接由軟件強置為有效或無效狀態,而不依賴于輸出比較寄存器和計數器間的比較結果。

置TIMx_CCMRx寄存器中相應的OCxM=101,即可強置輸出比較信號(OCxREF/OCx)為有效狀 態。這樣OCxREF被強置為高電平(OCxREF始終為高電平有效),同時OCx得到CCxP極性位相 反的值。

例如:CCxP=0(OCx高電平有效),則OCx被強置為高電平。

置TIMx_CCMRx寄存器中的OCxM=100,可強置OCxREF信號為低。

該模式下,在TIMx_CCRx影子寄存器和計數器之間的比較仍然在進行,相應的標志也會被修改。因此仍然會產生相應的中斷和DMA請求。這將會在下面的輸出比較模式一節中介紹。

1.3.8輸出比較模式

此項功能是用來控制一個輸出波形,或者指示一段給定的的時間已經到時。當計數器與捕獲/比較寄存器的內容相同時,輸出比較功能做如下操作:

?將輸出比較模式(TIMx_CCMRx寄存器中的OCxM位)和輸出極性(TIMx_CCER寄存器中的 CCxP位)定義的值輸出到對應的引腳上。在比較匹配時,輸出引腳可以保持它的電平(OCxM=000)、被設置成有效電平(OCxM=001)、被設置成無效電平(OCxM=010)或進行翻轉(OCxM=011)。

?設置中斷狀態寄存器中的標志位(TIMx_SR寄存器中的CCxIF位)。

?若設置了相應的中斷屏蔽(TIMx_DIER寄存器中的CCxIE位),則產生一個中斷。

?若設置了相應的使能位(TIMx_DIER寄存器中的CCxDE位,TIMx_CR2寄存器中的CCDS位 選擇DMA請求功能),則產生一個DMA請求。

TIMx_CCMRx中的OCxPE位選擇TIMx_CCRx寄存器是否需要使用預裝載寄存器。 在輸出比較模式下,更新事件UEV對OCxREF和OCx輸出沒有影響。

同步的精度可以達到計數器的一個計數周期。輸出比較模式(在單脈沖模式下)也能用來輸出一個 單脈沖。

輸出比較模式的配置步驟:

1.選擇計數器時鐘(內部,外部,預分頻器)

2.將相應的數據寫入TIMx_ARR和TIMx_CCRx寄存器中

3.如果要產生一個中斷請求和/或一個DMA請求,設置CCxIE位和/或CCxDE位。

4.選擇輸出模式,例如當計數器CNT與CCRx匹配時翻轉OCx的輸出引腳,CCRx預裝載未 用,開啟OCx輸出且高電平有效,則必須設置OCxM='011' 、OCxPE='0' 、CCxP='0'和 CCxE='1'。

5.設置TIMx_CR1寄存器的CEN位啟動計數器

TIMx_CCRx寄存器能夠在任何時候通過軟件進行更新以控制輸出波形,條件是未使用預裝載寄 存器(OCxPE='0',否則TIMx_CCRx影子寄存器只能在發生下一次更新事件時被更新)。下圖給出了一個例子:

輸出比較模式,翻轉OC1

1.3.9PWM 模式

脈沖寬度調制模式可以產生一個由TIMx_ARR寄存器確定頻率、由TIMx_CCRx寄存器確定占空比的信號。

在TIMx_CCMRx寄存器中的OCxM位寫入'110'(PWM模式1)或'111'(PWM模式2),能夠獨立地設 置每個OCx輸出通道產生一路PWM。必須設置TIMx_CCMRx寄存器OCxPE位以使能相應的預 裝載寄存器,最后還要設置TIMx_CR1寄存器的ARPE位,(在向上計數或中心對稱模式中)使能 自動重裝載的預裝載寄存器。

僅當發生一個更新事件的時候,預裝載寄存器才能被傳送到影子寄存器,因此在計數器開始計數之前,必須通過設置TIMx_EGR寄存器中的UG位來初始化所有的寄存器。

OCx的極性可以通過軟件在TIMx_CCER寄存器中的CCxP位設置,它可以設置為高電平有效或 低電平有效。TIMx_CCER寄存器中的CCxE位控制OCx輸出使能。詳見TIMx_CCERx寄存器的 描述。

在PWM模式(模式1或模式2)下,TIMx_CNT和TIMx_CCRx始終在進行比較,(依據計數器的計數 方向) 以確定是否符合TIMx_CCRx ≤ TIMx_CNT 或者TIMx_CNT ≤ TIMx_CCRx 。然而 為了與 OCREF_CLR的功能(在下一個PWM周期之前, ETR信號上的一個外部事件能夠清除OCxREF) 一致,OCxREF信號只能在下述條件下產生:

l當比較的結果改變

l當輸出比較模式(TIMx_CCMRx寄存器中的OCxM位)從“凍結”(無比較,OCxM='000')切換到某個PWM模式(OCxM='110'或'111')。

這樣在運行中可以通過軟件強置PWM輸出。

根據TIMx_CR1寄存器中CMS位的狀態,定時器能夠產生邊沿對齊的PWM信號或中央對齊的 PWM信號。

PWM 邊沿對齊模式

向上計數配置

當TIMx_CR1寄存器中的DIR位為低的時候執行向上計數。參看0節。

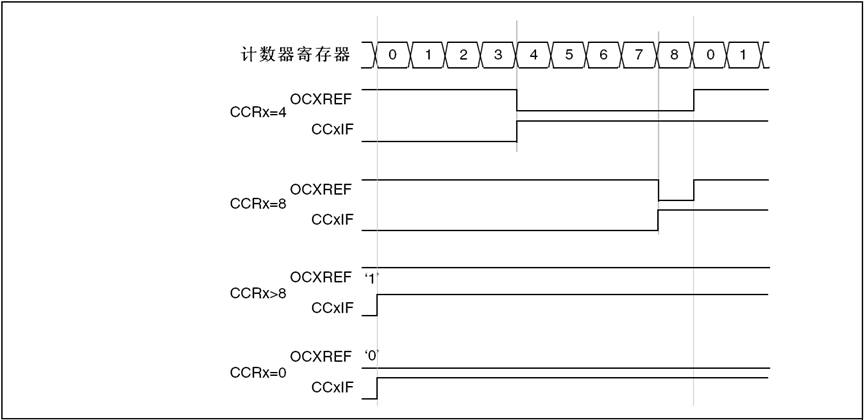

下面是一個PWM模式1的例子。當TIMx_CNT

如果比較值為0,則OCxREF保持為'0' 。 下圖為TIMx_ARR=8時邊沿對齊的PWM波形實例。:

邊沿對齊的PWM波形(ARR=8)

向下計數的配置

當TIMx_CR1寄存器的DIR位為高時執行向下計數。

在 PWM 模式 1 ,當 TIMx_CNT>TIMx_CCRx 時參考信號 OCxREF 為低,否 則為高。 如果 TIMx_CCRx中的比較值大于TIMx_ARR中的自動重裝載值,則OCxREF保持為'1'。該模式下不 能產生0%的PWM波形。

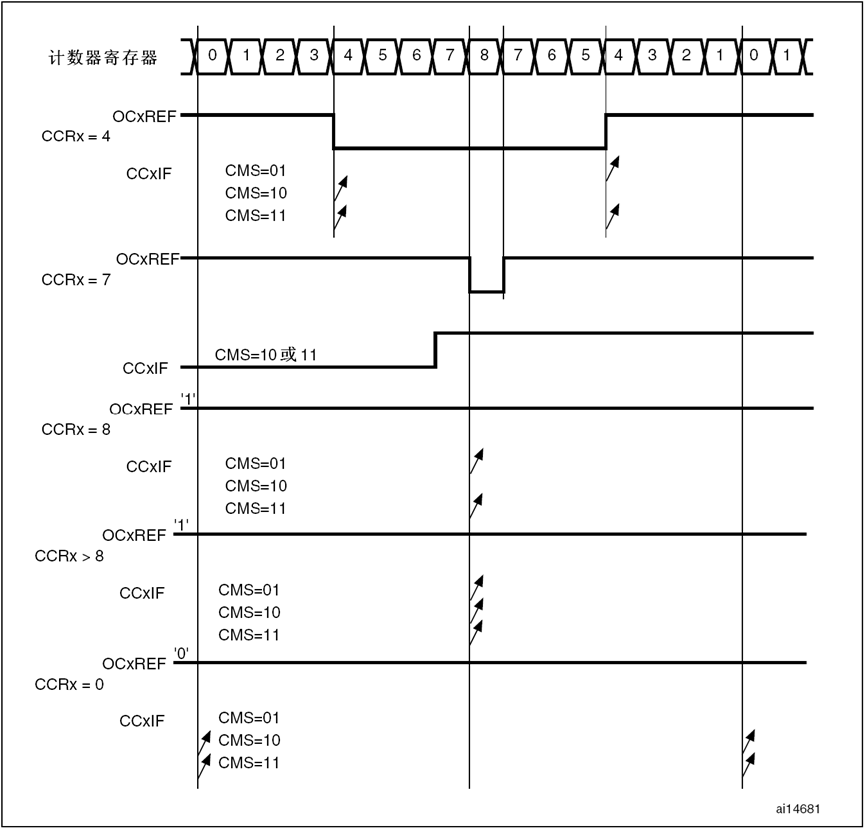

PWM 中央對齊模式

當TIMx_CR1寄存器中的CMS位不為'00'時,為中央對齊模式(所有其他的配置對OCxREF/OCx 信號都有相同的作用)。根據不同的CMS位設置,比較標志可以在計數器向上計數時被置'1'、在 計數器向下計數時被置'1'、或在計數器向上和向下計數時被置'1' 。TIMx_CR1寄存器中的計數方節的中央對齊模式。

下圖給出了一些中央對齊的PWM波形的例子:

?TIMx_ARR=8

?PWM模式1

?TIMx_CR1寄存器中的CMS=01,在中央對齊模式1時,當計數器向下計數時設置比較標 志。

中央對齊的PWM波形(APR=8)

使用中央對齊模式的提示:

進入中央對齊模式時,使用當前的向上/向下計數配置;這就意味著計數器向上還是向下計 數取決于TIMx_CR1寄存器中DIR位的當前值。此外,軟件不能同時修改DIR和CMS位。

不推薦當運行在中央對齊模式時改寫計數器,因為這會產生不可預知的結果。特別地:

如果寫入計數器的值大于自動重加載的值(TIMx_CNT>TIMx_ARR),則方向不會被更新。例如,如果計數器正在向上計數,它就會繼續向上計數。

如果將0或者TIMx_ARR的值寫入計數器,方向被更新,但不產生更新事件UEV。

使用中央對齊模式最保險的方法,就是在啟動計數器之前產生一個軟件更新(設置 TIMx_EGR 位中的UG位),不要在計數進行過程中修改計數器的值。

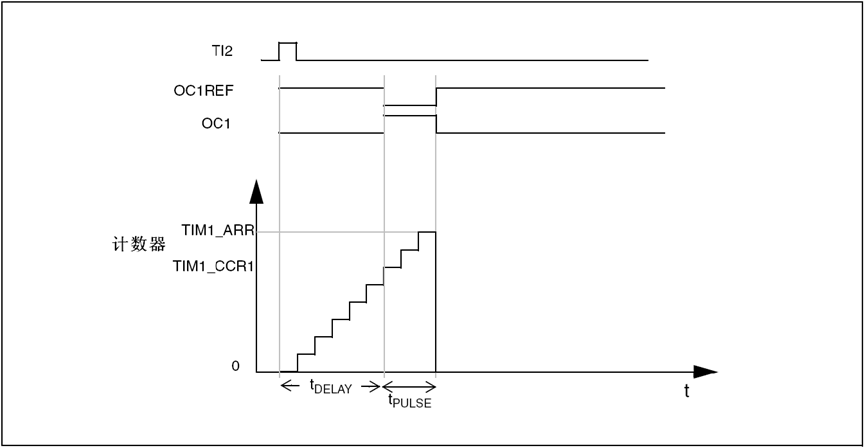

1.3.10單脈沖模式

單脈沖模式(OPM)是前述眾多模式的一個特例。這種模式允許計數器響應一個激勵,并在一個程序可控的延時之后,產生一個脈寬可程序控制的脈沖。

可以通過從模式控制器啟動計數器,在輸出比較模式或者 PWM 模式下產生波形。設置 TIMx_CR1寄存器中的OPM位將選擇單脈沖模式,這樣可以讓計數器自動地在產生下一個更新事件UEV時停止。

僅當比較值與計數器的初始值不同時,才能產生一個脈沖。啟動之前(當定時器正在等待觸發), 必須如下配置:

向上計數方式:CNT < CCRx ≤ ARR (特別地,0 < CCRx),

向下計數方式:CNT > CCRx。

單脈沖模式的例子

例如,你需要在從TI2輸入腳上檢測到一個上升沿開始,延遲tDELAY之后,在OC1上產生一個長

度為tPULSE 的正脈沖。

假定TI2FP2作為觸發1:

?置TIMx_CCMR1寄存器中的CC2S='01',把TI2FP2映像到TI2。

?置TIMx_CCER寄存器中的CC2P='0',使TI2FP2能夠檢測上升沿。

?置TIMx_SMCR寄存器中的TS='110' ,TI2FP2作為從模式控制器的觸發(TRGI)。

?置TIMx_SMCR寄存器中的SMS='110'(觸發模式),TI2FP2被用來啟動計數器。 OPM波形由寫入比較寄存器的數值決定(要考慮時鐘頻率和計數器預分頻器)

?tDELAY 由寫入TIMx_CCR1寄存器中的值定義。

?tPULSE 由自動裝載值和比較值之間的差值定義(TIMx_ARR - TIMx_CCR1)。

?假定當發生比較匹配時要產生從'0'到'1'的波形,當計數器到達預裝載值時要產生一個從'1' 到'0'的波形;首先要置TIMx_CCMR1寄存器的OC1M='111',進入PWM模式2;根據需要有 選擇地使能預裝載寄存器:置TIMx_CCMR1中的OC1PE='1'和TIMx_CR1寄存器中的ARPE;然后在TIMx_CCR1寄存器中填寫比較值,在TIMx_ARR寄存器中填寫自動裝載值,修改UG位來產生一個更新事件,然后等待在TI2上的一個外部觸發事件。本例中, CC1P='0'。

在這個例子中,TIMx_CR1寄存器中的DIR和CMS位應該置低。

因為只需一個脈沖,所以必須設置TIMx_CR1寄存器中的OPM='1',在下一個更新事件(當計數 器從自動裝載值翻轉到0)時停止計數。

特殊情況:OCx快速使能:

在單脈沖模式下,在TIx輸入腳的邊沿檢測邏輯設置CEN位以啟動計數器。然后計數器和比較值 間的比較操作產生了輸出的轉換。但是這些操作需要一定的時鐘周期,因此它限制了可得到的最小延時tDELAY。

如果要以最小延時輸出波形,可以設置TIMx_CCMRx寄存器中的OCxFE位;此時OCxREF(和 OCx)被強制響應激勵而不再依賴比較的結果,輸出的波形與比較匹配時的波形一樣。OCxFE只 在通道配置為PWM1和PWM2模式時起作用。

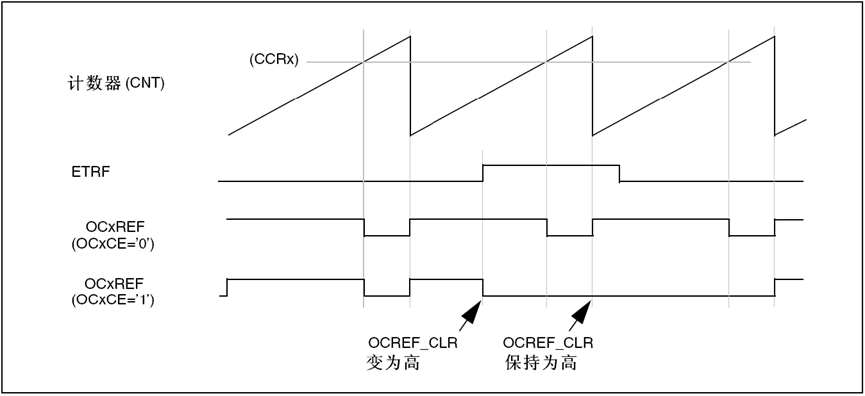

1.3.11在外部事件時清除OCxREF信號

對于一個給定的通道,設置TIMx_CCMRx寄存器中對應的OCxCE位為'1',能夠用ETRF輸入端 的高電平把OCxREF信號拉低,OCxREF信號將保持為低直到發生下一次的更新事件UEV。

該功能只能用于輸出比較和PWM模式,而不能用于強置模式。

例如,OCxREF信號可以聯到一個比較器的輸出,用于控制電流。這時,ETR必須配置如下:

1.外部觸發預分頻器必須處于關閉:TIMx_SMCR寄存器中的ETPS[1:0]='00'。

2.必須禁止外部時鐘模式2:TIMx_SMCR寄存器中的ECE='0'。

3.外部觸發極性(ETP)和外部觸發濾波器(ETF)可以根據需要配置。

下圖顯示了當ETRF輸入變為高時,對應不同OCxCE的值,OCxREF信號的動作。在這個例子 中,定時器TIMx被置于PWM模式。

清除TIMx的OCxREF

1.3.12編碼器接口模式

選擇編碼器接口模式的方法是:如果計數器只在TI2的邊沿計數,則置TIMx_SMCR寄存器中的 SMS=001;如果只在TI1邊沿計數,則置SMS=010;如果計數器同時在TI1和TI2邊沿計數,則 置SMS=011。

通過設置TIMx_CCER寄存器中的CC1P和CC2P位,可以選擇TI1和TI2極性;如果需要,還可以 對輸入濾波器編程。

兩個輸入TI1和TI2被用來作為增量編碼器的接口。參看表75,假定計數器已經啟動(TIMx_CR1 寄存器中的CEN='1'),計數器由每次在TI1FP1或TI2FP2上的有效跳變驅動。TI1FP1和TI2FP2 是TI1和TI2在通過輸入濾波器和極性控制后的信號; 如果沒有濾波和變相, 則TI1FP1=TI1 , TI2FP2=TI2。根據兩個輸入信號的跳變順序,產生了計數脈沖和方向信號。依據兩個輸入信號的跳變順序,計數器向上或向下計數,同時硬件對TIMx_CR1寄存器的DIR位進行相應的設置。 不管計數器是依靠TI1計數、依靠TI2計數或者同時依靠TI1和TI2計數。在任一輸入端(TI1或者 TI2)的跳變都會重新計算DIR位。

編碼器接口模式基本上相當于使用了一個帶有方向選擇的外部時鐘。這意味著計數器只在0到 TIMx_ARR寄存器的自動裝載值之間連續計數(根據方向,或是0到ARR計數,或是ARR到0計 數)。所以在開始計數之前必須配置TIMx_ARR;同樣,捕獲器、比較器、預分頻器、觸發輸出特性等仍工作如常。

在這個模式下,計數器依照增量編碼器的速度和方向被自動的修改,因此計數器的內容始終指示著編碼器的位置。計數方向與相連的傳感器旋轉的方向對應。下表列出了所有可能的組合,假設TI1和TI2不同時變換。

表75 計數方向與編碼器信號的關系

| 有效邊沿 | 相對信號的電平 (TI1FP1對應TI2, TI2FP2對應TI1) | TI1FP1信號 | TI2FP2信號 | ||

| 上升 | 下降 | 上升 | 下降 | ||

| 僅在TI1計數 | 高 | 向下計數 | 向上計數 | 不計數 | 不計數 |

| 低 | 向上計數 | 向下計數 | 不計數 | 不計數 | |

| 僅在TI2計數 | 高 | 不計數 | 不計數 | 向上計數 | 向下計數 |

| 低 | 不計數 | 不計數 | 向下計數 | 向上計數 | |

| 在TI1和TI2上計數 | 高 | 向下計數 | 向上計數 | 向上計數 | 向下計數 |

| 低 | 向上計數 | 向下計數 | 向下計數 | 向上計數 | |

一個外部的增量編碼器可以直接與MCU連接而不需要外部接口邏輯。但是, 一般會使用比較器 將編碼器的差動輸出轉換到數字信號,這大大增加了抗噪聲干擾能力。編碼器輸出的第三個信 號表示機械零點,可以把它連接到一個外部中斷輸入并觸發一個計數器復位。

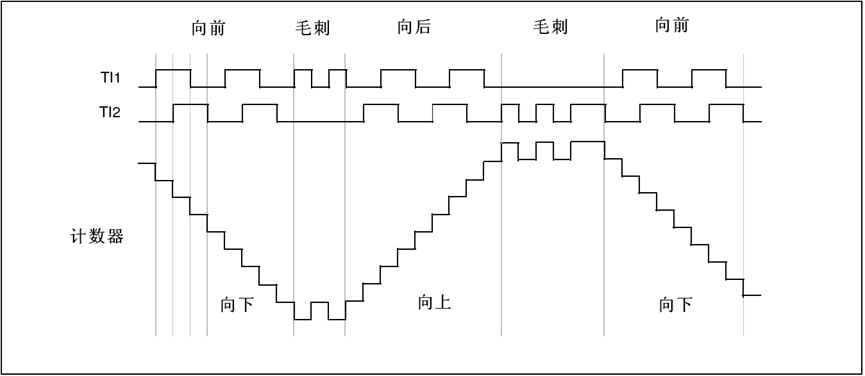

下圖是一個計數器操作的實例,顯示了計數信號的產生和方向控制。它還顯示了當選擇了雙邊沿時,輸入抖動是如何被抑制的;抖動可能會在傳感器的位置靠近一個轉換點時產生。在這個例子中,我們假定配置如下:

?CC1S='01' (TIMx_CCMR1寄存器,IC1FP1映射到TI1)

?CC2S='01' (TIMx_CCMR2寄存器,IC2FP2映射到TI2)

?CC1P='0' (TIMx_CCER寄存器,IC1FP1不反相,IC1FP1=TI1)

?CC2P='0' (TIMx_CCER寄存器,IC2FP2不反相,IC2FP2=TI2)

?SMS='011' (TIMx_SMCR寄存器,所有的輸入均在上升沿和下降沿有效).

?CEN='1' (TIMx_CR1寄存器,計數器使能)

編碼器模式下的計數器操作實例

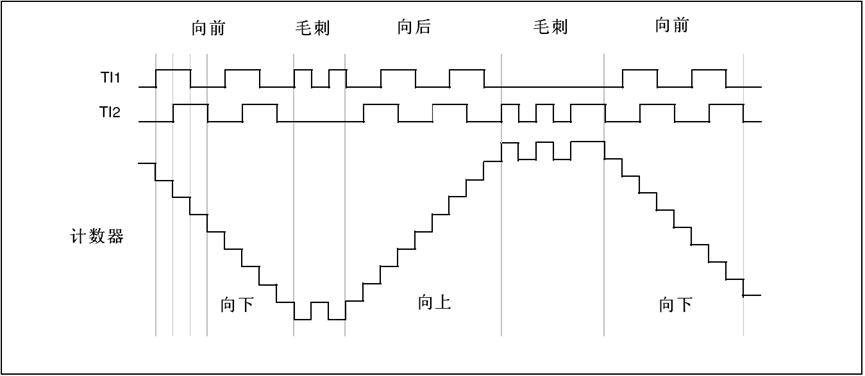

下圖為當IC1FP1極性反相時計數器的操作實例(CC1P='1',其他配置與上例相同)

IC1FP1反相的編碼器接口模式實例

當定時器配置成編碼器接口模式時,提供傳感器當前位置的信息。使用第二個配置在捕獲模式的定時器,可以測量兩個編碼器事件的間隔,獲得動態的信息(速度,加速度,減速度)。指示機 械零點的編碼器輸出可被用做此目的。根據兩個事件間的間隔,可以按照固定的時間讀出計數器。如果可能的話,你可以把計數器的值鎖存到第三個輸入捕獲寄存器(捕獲信號必須是周期的 并且可以由另一個定時器產生);也可以通過一個由實時時鐘產生的DMA請求來讀取它的值。

1.3.13定時器輸入異或功能

TIMx_CR2寄存器中的TI1S位,允許通道1的輸入濾波器連接到一個異或門的輸出端,異或門的 3個輸入端為TIMx_CH1、TIMx_CH2和TIMx_CH3。

異或輸出能夠被用于所有定時器的輸入功能,如觸發或輸入捕獲。

1.3.14定時器和外部觸發的同步

TIMx定時器能夠在多種模式下和一個外部的觸發同步:復位模式、門控模式和觸發模式。

從模式:復位模式

在發生一個觸發輸入事件時,計數器和它的預分頻器能夠重新被初始化;同時,如果TIMx_CR1 寄存器的URS位為低,還會產生一個更新事件UEV;然后所有的預裝載寄存器(TIMx_ARR , TIMx_CCRx)都會被更新。

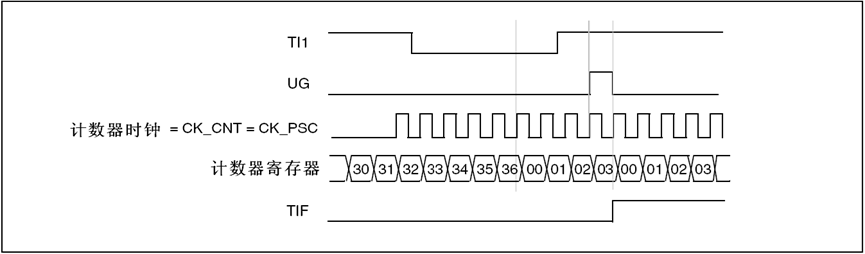

在下面的例子中,TI1輸入端的上升沿導致向上計數器被清零:

配置通道1以檢測TI1的上升沿。配置輸入濾波器的帶寬(在本例中,不需要任何濾波器,因 此保持IC1F=0000)。觸發操作中不使用捕獲預分頻器,所以不需要配置它。CC1S位只選 擇輸入捕獲源,即TIMx_CCMR1寄存器中CC1S=01。置TIMx_CCER寄存器中CC1P=0以 確定極性(只檢測上升沿)。

置TIMx_SMCR寄存器中SMS=100,配置定時器為復位模式;置TIMx_SMCR寄存器中 TS=101,選擇TI1作為輸入源。

置TIMx_CR1寄存器中CEN=1,啟動計數器。

計數器開始依據內部時鐘計數,然后正常運轉直到TI1出現一個上升沿;此時,計數器被清零然 后從0重新開始計數。同時,觸發標志(TIMx_SR寄存器中的TIF位)被設置,根據TIMx_DIER寄 存器中TIE(中斷使能)位和TDE(DMA使能)位的設置,產生一個中斷請求或一個DMA請求。

下圖顯示當自動重裝載寄存器TIMx_ARR=0x36時的動作。在TI1上升沿和計數器的實際復位之 間的延時,取決于TI1輸入端的重同步電路。

復位模式下的控制電路

從模式:門控模式

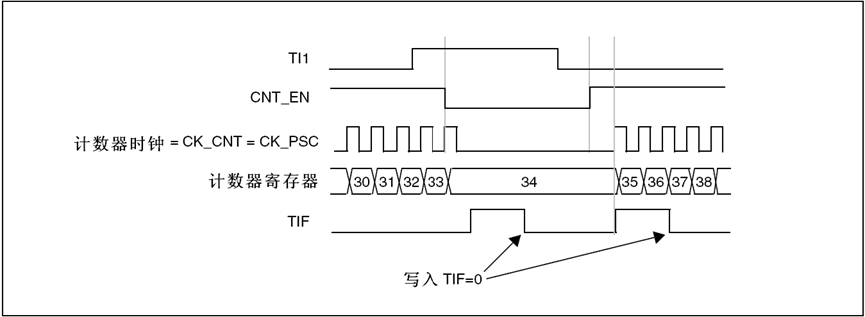

按照選中的輸入端電平使能計數器。

在如下的例子中,計數器只在TI1為低時向上計數:

?配置通道1以檢測TI1上的低電平。配置輸入濾波器帶寬(本例中,不需要濾波,所以保持 IC1F=0000)。觸發操作中不使用捕獲預分頻器,所以不需要配置。CC1S位用于選擇輸入 捕獲源,置TIMx_CCMR1寄存器中CC1S=01。置TIMx_CCER寄存器中CC1P=1以確定極 性(只檢測低電平)。

?置TIMx_SMCR寄存器中SMS=101,配置定時器為門控模式;置TIMx_SMCR寄存器中 TS=101,選擇TI1作為輸入源。

?置TIMx_CR1寄存器中CEN=1,啟動計數器。在門控模式下,如果CEN=0,則計數器不能 啟動,不論觸發輸入電平如何。

只要TI1為低,計數器開始依據內部時鐘計數,在TI1變高時停止計數。當計數器開始或停止時 都設置TIMx_SR中的TIF標置。

TI1上升沿和計數器實際停止之間的延時,取決于TI1輸入端的重同步電路。

門控模式下的控制電路

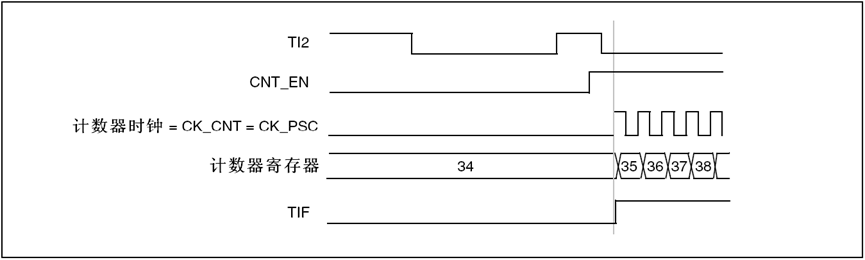

從模式:觸發模式

輸入端上選中的事件使能計數器。

在下面的例子中,計數器在TI2輸入的上升沿開始向上計數:

?配置通道2檢測TI2的上升沿。配置輸入濾波器帶寬(本例中,不需要任何濾波器,保持IC2F=0000)。觸發操作中不使用捕獲預分頻器,不需要配置。CC2S位只用于選擇輸入捕 獲源,置TIMx_CCMR1寄存器中CC2S=01。置TIMx_CCER寄存器中CC2P=1以確定極性 (只檢測低電平)。

?置TIMx_SMCR寄存器中SMS=110,配置定時器為觸發模式;置TIMx_SMCR寄存器中 TS=110,選擇TI2作為輸入源。

當TI2出現一個上升沿時,計數器開始在內部時鐘驅動下計數,同時設置TIF標志。

TI2上升沿和計數器啟動計數之間的延時,取決于TI2輸入端的重同步電路。

觸發器模式下的控制電路

從模式:外部時鐘模式2 + 觸發模式

外部時鐘模式2可以與另一種從模式(外部時鐘模式1和編碼器模式除外)一起使用。這時,ETR信 號被用作外部時鐘的輸入,在復位模式、門控模式或觸發模式時可以選擇另一個輸入作為觸發輸入。不建議使用TIMx_SMCR寄存器的TS位選擇ETR作為TRGI。

下面的例子中,TI1上出現一個上升沿之后,計數器即在ETR的每一個上升沿向上計數一次:

?通過TIMx_SMCR寄存器配置外部觸發輸入電路:

······ETF=0000:沒有濾波

······ETPS=00:不用預分頻器

······ETP=0:檢測ETR的上升沿,置ECE=1使能外部時鐘模式2

?按如下配置通道1,檢測TI的上升沿:

······IC1F=0000:沒有濾波

·······觸發操作中不使用捕獲預分頻器,不需要配置

·······置TIMx_CCMR1寄存器中CC1S=01,選擇輸入捕獲源

······置TIMx_CCER寄存器中CC1P=0以確定極性(只檢測上升沿)

?置TIMx_SMCR寄存器中SMS=110,配置定時器為觸發模式。置TIMx_SMCR寄存器中 TS=101,選擇TI1作為輸入源。

當TI1上出現一個上升沿時,TIF標志被設置,計數器開始在ETR的上升沿計數。

ETR信號的上升沿和計數器實際復位間的延時,取決于ETRP輸入端的重同步電路。

外部時鐘模式2+觸發模式下的控制電路

1.3.15定時器同步

所有TIMx定時器在內部相連,用于定時器同步或鏈接。當一個定時器處于主模式時,它可以對另一個處于從模式的定時器的計數器進行復位、啟動、停止或提供時鐘等操作。

下圖顯示了觸發選擇和主模式選擇模塊的概況。

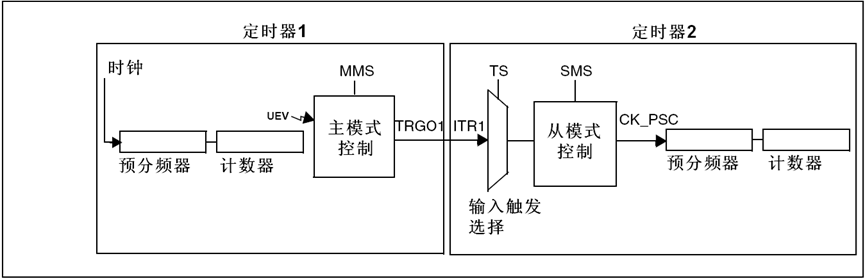

使用一個定時器作為另一個定時器的預分頻器

主/從定時器的例子

如:可以配置定時器1作為定時器2的預分頻器。參考上圖,進行下述操作:

?配置定時器1為主模式,它可以在每一個更新事件UEV時輸出一個周期性的觸發信號。在TIM1_CR2寄存器的MMS='010'時,每當產生一個更新事件時在TRGO1上輸出一個上升沿信號。

?連接定時器1的TRGO1輸出至定時器2,設置TIM2_SMCR寄存器的TS='000',配置定時器2為使用ITR1作為內部觸發的從模式。

?然后把從模式控制器置于外部時鐘模式1(TIM2_SMCR寄存器的SMS=111);這樣定時器2即可由定時器1周期性的上升沿(即定時器1的計數器溢出)信號驅動。

?最后,必須設置相應(TIMx_CR1寄存器)的CEN位分別啟動兩個定時器。

注:如果OCx已被選中為定時器1的觸發輸出(MMS=1xx),它的上升沿用于驅動定時器2的計數器。

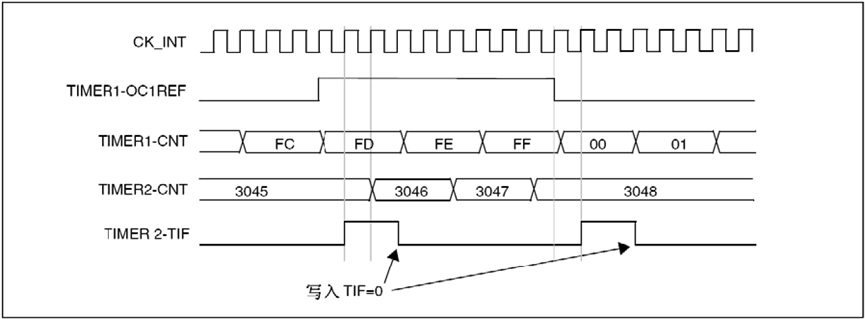

使用一個定時器使能另一個定時器

在這個例子中,定時器2的使能由定時器1的輸出比較控制。只當定時器1的OC1REF為高時,定時器2才對分頻后的內部時鐘計數。兩個定時器的時鐘頻率都是由預分頻器對CK_INT除以3(fCK_CNT=fCK_INT/3)得到。

?配置定時器1為主模式,送出它的輸出比較參考信號(OC1REF)為觸發輸出(TIM1_CR2寄存器的MMS=100)

?配置定時器1的OC1REF波形(TIM1_CCMR1寄存器)

?配置定時器2從定時器1獲得輸入觸發(TIM2_SMCR寄存器的TS=000)

?配置定時器2為門控模式(TIM2_SMCR寄存器的SMS=101)

?置TIM2_CR1寄存器的CEN=1以使能定時器2

?置TIM1_CR1寄存器的CEN=1以啟動定時器1

注:定時器2的時鐘不與定時器1的時鐘同步,這個模式只影響定時器2計數器的使能信號。

定時器1的OC1REF控制定時器2

在這個例子中,在定時器2啟動之前,它們的計數器和預分頻器未被初始化,因此它們從當前的數值開始計數。可以在啟動定時器1之前復位2個定時器,使它們從給定的數值開始,即在定時器計數器中寫入需要的任意數值。寫TIMx_EGR寄存器的UG位即可復位定時器。

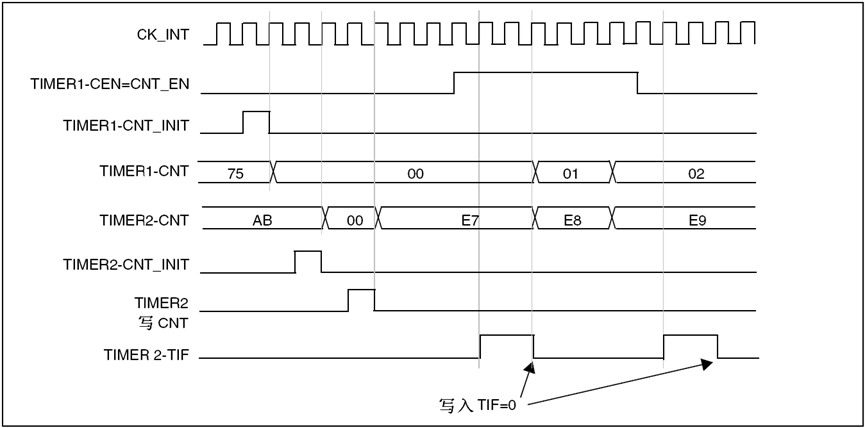

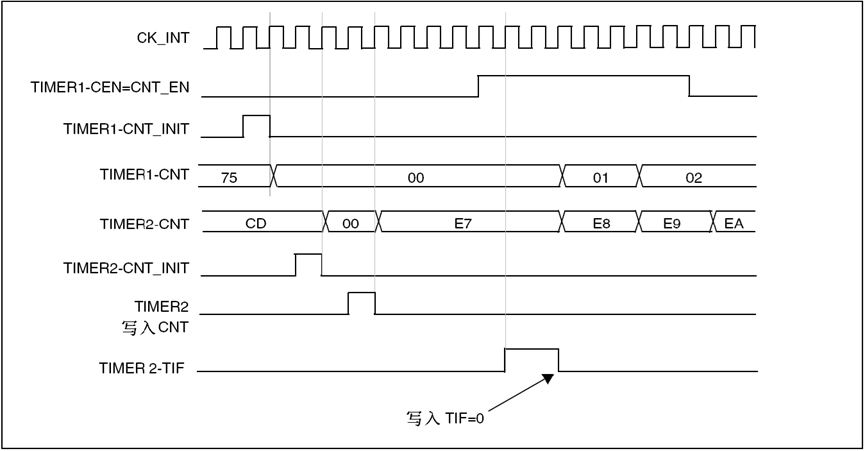

在下一個例子中,需要同步定時器1和定時器2。定時器1是主模式并從0開始,定時器2是從模式并從0xE7開始;2個定時器的預分頻器系數相同。寫'0'到TIM1_CR1的CEN位將禁止定時器1,定時器2隨即停止。

?配置定時器1為主模式,送出輸出比較1參考信號(OC1REF)做為觸發輸出(TIM1_CR2寄存器的MMS=100)。

?配置定時器1的OC1REF波形(TIM1_CCMR1寄存器)。

?配置定時器2從定時器1獲得輸入觸發(TIM2_SMCR寄存器的TS=000)

?配置定時器2為門控模式(TIM2_SMCR寄存器的SMS=101)

?置TIM1_EGR寄存器的UG='1',復位定時器1。

?置TIM2_EGR寄存器的UG='1',復位定時器2。

?寫'0xE7'至定時器2的計數器(TIM2_CNTL),初始化它為0xE7。

?置TIM2_CR1寄存器的CEN='1'以使能定時器2。

?置TIM1_CR1寄存器的CEN='1'以啟動定時器1。

?置TIM1_CR1寄存器的CEN='0'以停止定時器1。

通過使能定時器1可以控制定時器2

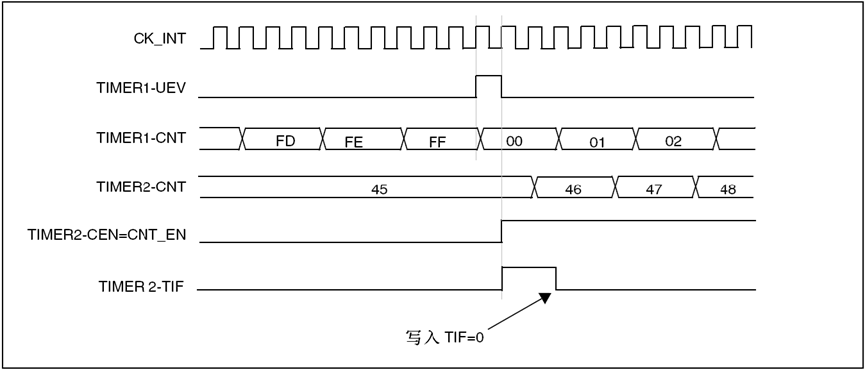

使用一個定時器去啟動另一個定時器

在這個例子中,使用定時器1的更新事件使能定時器2。一旦定時器1產生更新事件,定時器2即從它當前的數值(可以是非0)按照分頻的內部時鐘開始計數。在收到觸發信號時,定時器2的CEN位被自動地置'1',同時計數器開始計數直到寫'0'到TIM2_CR1寄存器的CEN位。兩個定時器的時鐘頻率都是由預分頻器對CK_INT除以3(fCK_CNT=fCK_INT/3)。

?配置定時器1為主模式,送出它的更新事件(UEV)做為觸發輸出(TIM1_CR2寄存器的MMS=010)。

?配置定時器1的周期(TIM1_ARR寄存器)。

?配置定時器2從定時器1獲得輸入觸發(TIM2_SMCR寄存器的TS=000)

?配置定時器2為觸發模式(TIM2_SMCR寄存器的SMS=110)

?置TIM1_CR1寄存器的CEN=1以啟動定時器1。

使用定時器1的更新觸發定時器2

在上一個例子中,可以在啟動計數之前初始化兩個計數器。下圖顯示在與0相同配置情況下,使用觸發模式而不是門控模式(TIM2_SMCR寄存器的SMS=110)的動作。

利用定時器1的使能觸發定時器2

使用一個定時器作為另一個的預分頻器

這個例子使用定時器1作為定時器2的預分頻器。配置如下:

?配置定時器1為主模式,送出它的更新事件UEV做為觸發輸出(TIM1_CR2寄存器的MMS='010')。然后每次計數器溢出時輸出一個周期信號。

?配置定時器1的周期(TIM1_ARR寄存器)。

?配置定時器2從定時器1獲得輸入觸發(TIM2_SMCR寄存器的TS=000)

?配置定時器2使用外部時鐘模式(TIM2_SMCR寄存器的SMS=111)

?置TIM1_CR2寄存器的CEN=1以啟動定時器2。

?置TIM1_CR1寄存器的CEN=1以啟動定時器1。

使用一個外部觸發同步地啟動2個定時器

這個例子中當定時器1的TI1輸入上升時使能定時器1,使能定時器1的同時使能定時器2,為保證計數器的對齊,定時器1必須配置為主/從模式(對應TI1為從,對應定時器2為主):

?配置定時器1為主模式,送出它的使能做為觸發輸出(TIM1_CR2寄存器的MMS='001')。

?配置定時器1為從模式,從TI1獲得輸入觸發(TIM1_SMCR寄存器的TS='100')。

?配置定時器1為觸發模式(TIM1_SMCR寄存器的SMS='110')。

?配置定時器1為主/從模式,TIM1_SMCR寄存器的MSM='1'。

?配置定時器2從定時器1獲得輸入觸發(TIM2_SMCR寄存器的TS=000)

?配置定時器2為觸發模式(TIM2_SMCR寄存器的SMS='110')。

當定時器1的TI1上出現一個上升沿時,兩個定時器同步地按照內部時鐘開始計數,兩個TIF標志也同時被設置。

注:在這個例子中,在啟動之前兩個定時器都被初始化(設置相應的UG位),兩個計數器都從0開始,但可以通過寫入任意一個計數器寄存器(TIMx_CNT)在定時器間插入一個偏移。下圖中能看到主/從模式下在定時器1的CNT_EN和CK_PSC之間有個延遲。

使用定時器1的TI1輸入觸發定時器1和定時器2

1.3.16調試模式

當微控制器進入調試模式(Cortex-M3核心停止),根據DBG模塊中DBG_TIMx_STOP的設置,TIMx計數器或者繼續正常操作,或者停止。詳見后面的章節:支持定時器、看門狗、bxCAN和I2C的調試。

2 程序設計

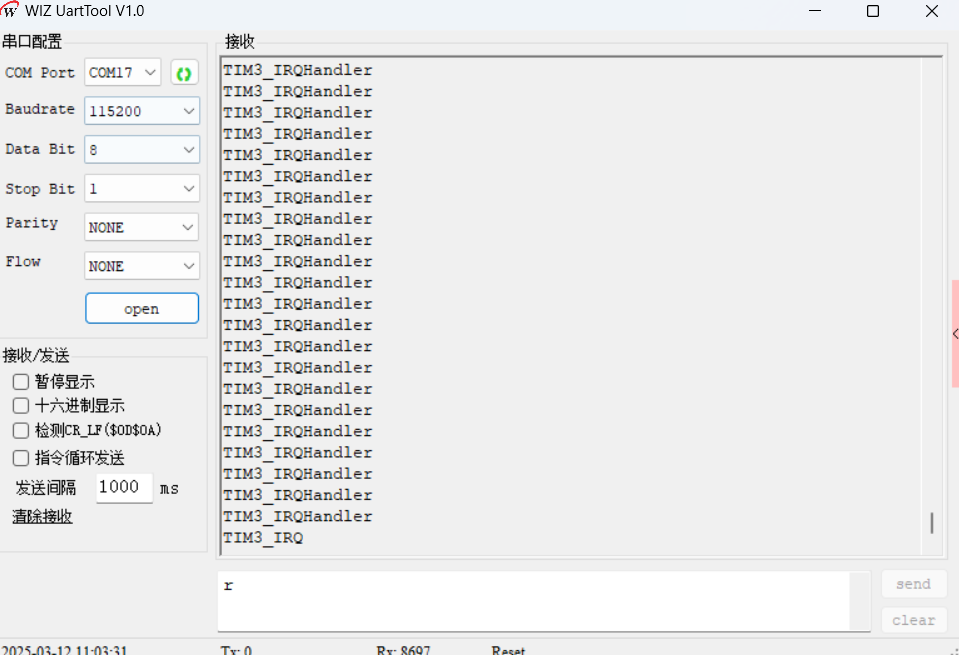

2.1 TIM_Basic例程

此例程的主要作用是進行通用定時器的測試。通過配置定時器 TIM3,使其在計數溢出時產生更新中斷,在中斷服務函數中打印中斷服務函數名,以此來驗證定時器的中斷功能是否正常工作。

系統上電或復位后,程序開始執行。首先會通過串口輸出系統時鐘頻率信息和測試提示信息,之后,定時器 TIM3 開始計數。當計數器的值達到自動重載值 9999 時,會產生更新中斷,進入中斷服務函數 TIM3_IRQHandler。在中斷服務函數中,會清除中斷標志位并通過串口輸出 TIM3_IRQHandler。

此后,每隔一段時間(由定時器的預分頻器和自動重載值決定),定時器就會產生一次更新中斷,串口會周期性地輸出 TIM3_IRQHandler,表明定時器的中斷功能正常工作。

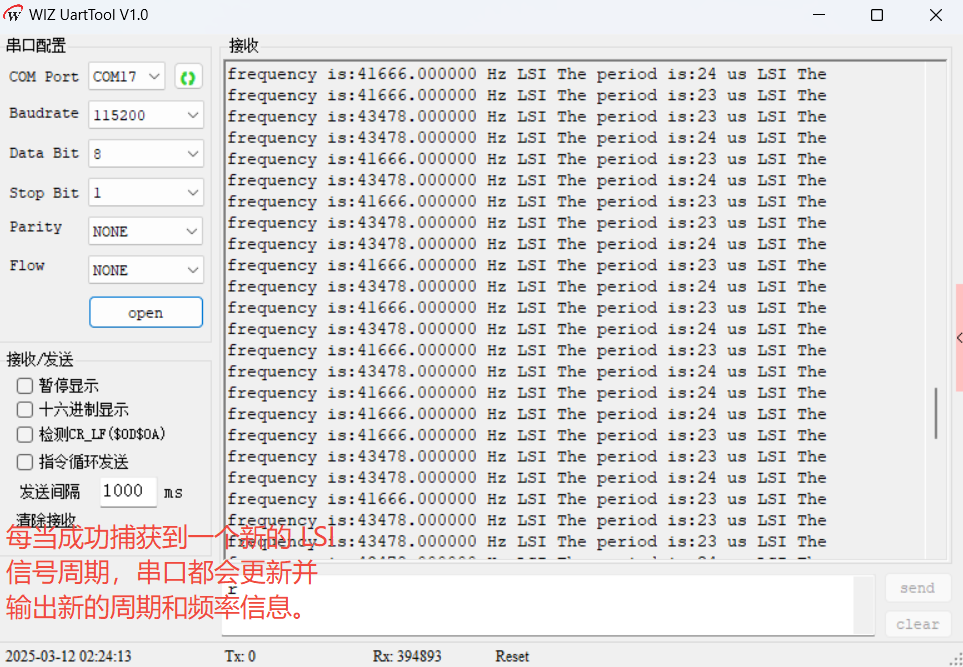

2.2 TIM_CalibrationLsi例程

此例程的主要作用是通過定時器 TIM5 的輸入捕獲功能來測量內部低速振蕩器(LSI)信號的周期和頻率。LSI 通常用于實時時鐘(RTC)等對時鐘精度要求不高的場合,通過測量其周期和頻率,可以對 LSI 的性能進行評估。

1.時鐘配置

void RCC_ClkConfiguration(void)

{

RCC_DeInit(); // 復位RCC時鐘配置到默認狀態

// 配置外部高速時鐘(HSE)

RCC_HSEConfig(RCC_HSE_ON); // 使能HSE

while (RCC_GetFlagStatus(RCC_FLAG_HSERDY) == RESET); // 等待HSE就緒

// 配置鎖相環(PLL):HSE×9=72MHz

RCC_PLLCmd(DISABLE); // 先禁用PLL

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9); // 設置PLL輸入源為HSE,倍頻系數9

RCC_PLLCmd(ENABLE); // 使能PLL

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET); // 等待PLL就緒

// 設置系統時鐘源為PLL輸出

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // 選擇PLL作為系統時鐘源

// 配置總線時鐘分頻

RCC_HCLKConfig(RCC_SYSCLK_Div1); // AHB總線時鐘 = SYSCLK/1 (72MHz)

RCC_PCLK1Config(RCC_HCLK_Div2); // APB1總線時鐘 = HCLK/2 (36MHz)

RCC_PCLK2Config(RCC_HCLK_Div1); // APB2總線時鐘 = HCLK/1 (72MHz)

// 使能內部低速時鐘(LSI)和高速時鐘(HSI)

RCC_LSICmd(ENABLE); // 使能LSI(約40kHz,用于看門狗等)

while (RCC_GetFlagStatus(RCC_FLAG_LSIRDY) == RESET); // 等待LSI就緒

RCC_HSICmd(ENABLE); // 使能HSI(16MHz內部RC時鐘)

while (RCC_GetFlagStatus(RCC_FLAG_HSIRDY) == RESET); // 等待HSI就緒

}

外部高速時鐘(HSE):使能 HSE 并等待其就緒,為后續鎖相環(PLL)提供穩定的輸入時鐘源。

鎖相環(PLL):以 HSE 為輸入源,設置倍頻系數為 9,使能 PLL 并等待其就緒,得到更高頻率的時鐘信號。

系統時鐘源:將系統時鐘源設置為 PLL 輸出,提高系統整體運行速度。

總線時鐘分頻:對 AHB、APB1 和 APB2 總線時鐘進行合理分頻,滿足不同外設的時鐘需求。

內部低速時鐘(LSI)和高速時鐘(HSI):使能 LSI 和 HSI 并等待它們就緒,其中 LSI 用于后續測量。

2.初始化操作

延時函數:調用 delay_init() 初始化延時函數,為后續可能的延時操作做準備。

串口通信:調用 UART_Configuration(115200) 配置串口通信,波特率為 115200,用于輸出系統時鐘信息、測試提示以及測量結果。

獲取時鐘頻率:使用 RCC_GetClocksFreq(&clocks) 獲取系統時鐘頻率信息,為定時器配置提供參數。

3. 定時器配置

時鐘使能:使能 TIM5 和復用功能(AFIO)的時鐘,確保 TIM5 能夠正常工作,并允許對其引腳進行重映射。

引腳重映射:將 TIM5 的通道 4 重映射到 LSI 信號,以便對 LSI 信號進行捕獲。

時基單元初始化:設置 TIM5 的自動重載值為 0xFFFF,預分頻器值根據 PCLK1 頻率計算得出,時鐘分割為 1,計數模式為向上計數,確定定時器的計數范圍和計數速度。

輸入捕獲配置:將 TIM5 的通道 4 配置為輸入捕獲模式,采用上升沿捕獲,直接映定時器溢出和捕獲到信號邊沿時能夠及時響應。

定時器使能:使能 TIM5,開始對 LSI 信號進行計數和捕獲。

4.主循環處理

int main(void)

{

// ...(前半部分初始化代碼略)

TIM_Configuration(); // 初始化TIM5

while (1)

{

if (TIM5_CAPTURE_STA & 0X80) // 檢測捕獲完成標志(最高位為1)

{

// 計算總時間(考慮定時器溢出次數)

temp = (TIM5_CAPTURE_STA & 0X3F) * 65536 + TIM5_CAPTURE_VAL; // 溢出次數×65536 + 捕獲值

printf("LSI The period is:%d usrn", temp); // 輸出周期(微秒)

printf("LSI The frequency is:%f Hzrn", (float)(1000000 / temp)); // 計算頻率并輸出

TIM5_CAPTURE_STA = 0; // 清零標志,準備下一次捕獲

}

}

}

使用TI4,不分頻且不進行濾波,以準確捕獲 LSI 信號的上升沿和下降沿。

中斷配置:配置 TIM5 的中斷優先級,使能更新中斷和通道 4 捕獲中斷,確保在

在主循環中,持續檢查 TIM5_CAPTURE_STA 的最高位。若該位為 1,表示成功捕獲到一個完整的 LSI 信號周期。此時,計算該周期的總時間(考慮定時器溢出情況),并通過串口輸出 LSI 的周期和頻率。最后,將 TIM5_CAPTURE_STA 清零,準備下一次捕獲。

5. 中斷服務函數處理

當 TIM5 產生更新中斷或通道 4 捕獲中斷時,進入中斷服務函數:

若還未成功捕獲到一個完整的周期:

對于更新中斷,若已捕獲到上升沿,則記錄定時器溢出次數。

對于通道 4 捕獲中斷:

若已捕獲到上升沿,此時捕獲到下降沿,標記成功捕獲到一個完整的高脈沖寬度,并記錄捕獲值。

若還未開始捕獲,此時捕獲到上升沿,清零相關變量,設置計數器為 0,并標記捕獲到上升沿。

最后,清除更新中斷和通道 4 捕獲中斷標志位,為下一次中斷做好準備。

3 下載驗證

3.1 TIM_Basic例程

燒錄完成后,硬件啟動,串口輸出系統時鐘頻率信息及“TIM Basic Test.”提示,定時器TIM3配置為向上計數模式,計數周期達9999時觸發更新中斷,在中斷服務函數中檢查并清除中斷標志,通過串口輸出函數名`TIM3_IRQHandler,之后主函數進入無限循環持續等待并響應定時器中斷。

3.2 TIM_CalibrationLsi例程

代碼燒錄后,系統先對時鐘進行配置,啟動串口并輸出系統時鐘頻率信息及“TIM5 Calibration LSI Test.”提示,接著配置TIM5定時器用于測量低速內部時鐘(LSI),當TIM5捕獲到LSI信號的上升沿和下降沿后,主循環會計算并通過串口輸出LSI的周期和頻率,期間持續等待新的捕獲事件。

WIZnet 是一家無晶圓廠半導體公司,成立于 1998 年。產品包括互聯網處理器 iMCU?,它采用 TOE(TCP/IP 卸載引擎)技術,基于獨特的專利全硬連線 TCP/IP。iMCU? 面向各種應用中的嵌入式互聯網設備。

WIZnet 在全球擁有 70 多家分銷商,在香港、韓國、美國設有辦事處,提供技術支持和產品營銷。

香港辦事處管理的區域包括:澳大利亞、印度、土耳其、亞洲(韓國和日本除外)。

審核編輯 黃宇

-

單片機

+關注

關注

6067文章

44991瀏覽量

650423 -

物聯網

+關注

關注

2931文章

46243瀏覽量

392456 -

通用定時器

+關注

關注

1文章

19瀏覽量

3526

發布評論請先 登錄

國外論壇帖:什么樣的單片機能很好地應用于以太網應用...

明德揚視頻分享點撥FPGA課程--第十一章 ?Signaltapll的使用技巧

WIZnet發布最新單片式以太網控制芯片W7100

第一章 W55MH32 高性能以太網單片機的學習方法概述

第二章 開發板與芯片介紹 詳解W55MH32芯片及開發板

W55MH32高性能以太網單片機教程 第九章 窗口看門狗(WWDG)

WIZnet W55MH32以太網單片機開發教程第十一章 通用定時器(下篇)

W55MH32高性能以太網單片機開發課件 第十四章 ADC(上篇)

WIZnet W55MH32以太網單片機開發教程 第十一章 通用定時器(上篇)

WIZnet W55MH32以太網單片機開發教程 第十一章 通用定時器(上篇)

評論