Inphi 是高速數據移動互連領域的領導者,致力于在全球范圍內、數據中心之間以及數據中心內部快速傳輸大數據。

我們在所有先進工藝節點項目中都采用了 Tempus ECO 和 Tempus Signoff。由于設計規模龐大,我們選擇運行扁平化靜態時序分析 (STA),并充分利用 Tempus 的DSTA和 CMMMC 功能。這使得我們的設計人員能夠更快地完成簽核,從而滿足產品上市時間的要求。由于高度的相關性,Tempus 解決方案還能與Innovus Implementation更快地收斂,并實現更好的 PPA(功耗、性能、面積)。我們的設計人員可以充滿信心地使用 Tempus ECO 和 Signoff 進行簽核。——工程副總裁WEIKAI SUN

挑戰

●需要在 500GB 內存的機器上進行全芯片扁平化簽核。

●在相同的機器上,STA 幾乎耗盡所有內存才能完成單個工藝角的分析。

●需要同時運行多種模式和多個工藝角,而非僅單個工藝角。

優勢

●將 Tempus ECO 集成到 Innovus Implementation 系統并結合 Quantus 寄生參數提取解決方案,減少了迭代次數。

●盡管大部分功耗優化是在 Genus Synthesis 綜合解決方案中完成的,但仍然實現了額外的 5% 功耗降低。

●使用 DSTA 在合理的時間內完成了 CMMMC 的扁平化處理。

CMMMC 具有大約 25 個用于建立時間和保持時間分析的視圖,這極大地提高了我們按計劃完成流片的效率。

與單工藝角 STA 相比,運行時間縮短了 50%(DSTA CMMMC 運行并生成報告耗時約 10 小時;單工藝角 STA 耗時超過 20 小時)。

●由于 Innovus、ECO 和 Signoff 共享簽核引擎,因此具有更好的相關性,從而可以最大程度地縮短設計收斂時間。

●由于具備頂層范圍,易于使用,因此能夠更快地修復頂層接口,并減少所需的許可證數量。

●在從設計周期開始到流片完成的整個過程中,Cadence 工程師都提供了卓越的支持。

設計

●7nm

●使用 SOCV

●使用 16CPU

-

cpu

+關注

關注

68文章

11040瀏覽量

216042 -

工藝

+關注

關注

4文章

672瀏覽量

29263 -

Cadence

+關注

關注

67文章

965瀏覽量

143860

原文標題:Inphi 通過 Tempus Timing Signoff 完成 7nm 全芯片扁平化設計流片,縮短了產品上市時間

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片如何設計

聯發科采用AI驅動Cadence工具加速2nm芯片設計

芯片流片的基礎知識

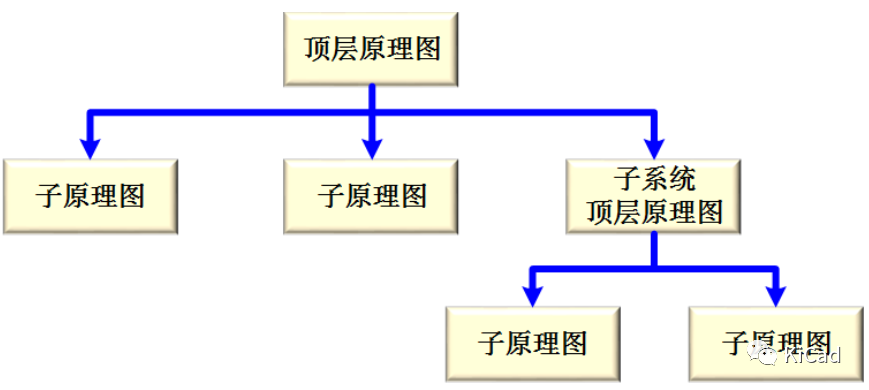

層次化或扁平化結構原理圖設計,哪個更適合我?

世芯電子成功流片2nm測試芯片

傳理想汽車智能駕駛SoC芯片年底前完成流片

所謂的7nm芯片上沒有一個圖形是7nm的

Inphi借助Cadence技術完成7nm全芯片扁平化設計流片

Inphi借助Cadence技術完成7nm全芯片扁平化設計流片

評論