最近網上因為光刻機的事情,網上又是一陣熱鬧。好多人又開始討論起28nm/7nm的事情了有意無意之間,我也看了不少網上關于國產自主7nm工藝的文章。不過這些文章里更多是抒情和遐想,卻很少有人針對技術本身做過深入解釋和探討當然,關于國產7nm工藝技術的具體來源細節,我其實了解也不多,也不方便公開討論。但至少我覺得有必要寫些文字給非半導體制造行業的人士講解一下,一般意義上所謂的7nm工藝到底是怎么回事

首先簡單明確一個事實:正如我文章標題所言,7nm工藝其實只是一個等效的說法,實際上7nm芯片上所有層的最小線寬都遠遠大于7nm

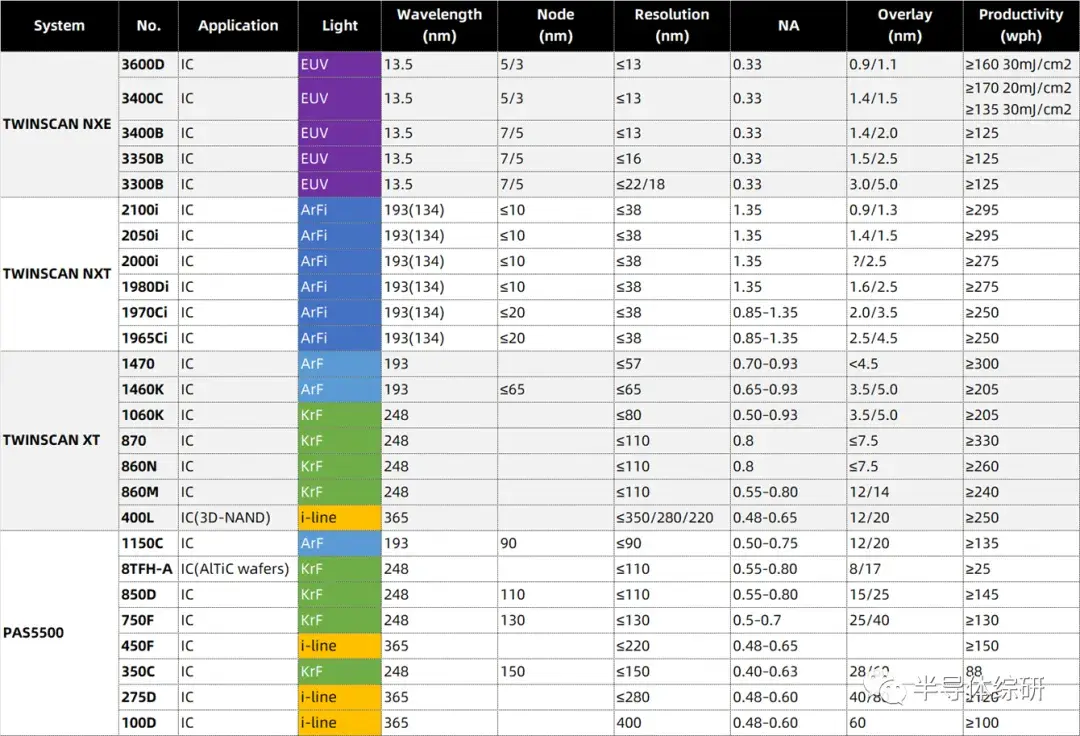

上圖是我整理的ASML目前在售的各類光刻機的型號及技術指標清單。從表中可見,最先進的DUV光刻機 TWINSACAN NXT 2100i的最高分辨率只有38nm;而EUV光刻機 3600D的分辨率也只有13nm在晶圓廠的實際生產過程中,無論是用DUV加多重曝光或者是EUV(在7nm~5nm工藝中,EUV都只是單次曝光)都無法達到7nm的分辨率/CD值(半間距)

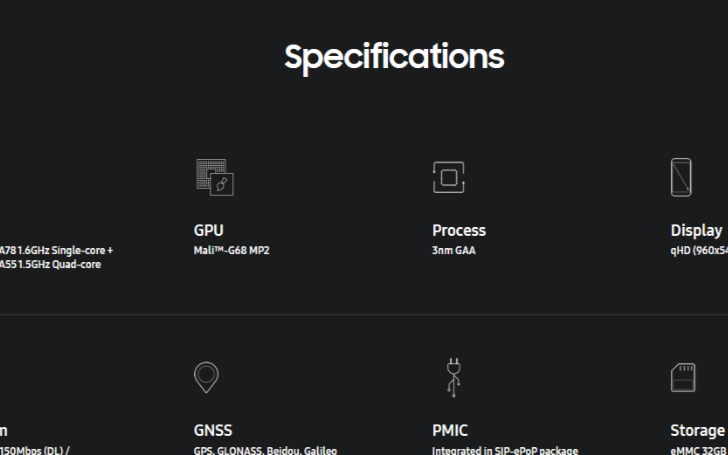

當初FinFET工藝被采用后,雖然實際上圖形的線寬/分辨率并沒有大幅度提高,但由于晶體管的結構發生重大變化以后,其整體尺寸是明顯微縮了。這就使得我們能夠在單位面積的晶圓上容納更多數量的晶體管。從效果的角度上,開發者將其對比原有平面晶體管的密度來換算出一個名義上的等效線寬:也就是我們一般所謂的14nm、7nm...從20nm開始,所有晶體管都開始采用FinFET工藝后(3nm開始有了GAA等新技術),這個線寬就都完全是等效出來的了

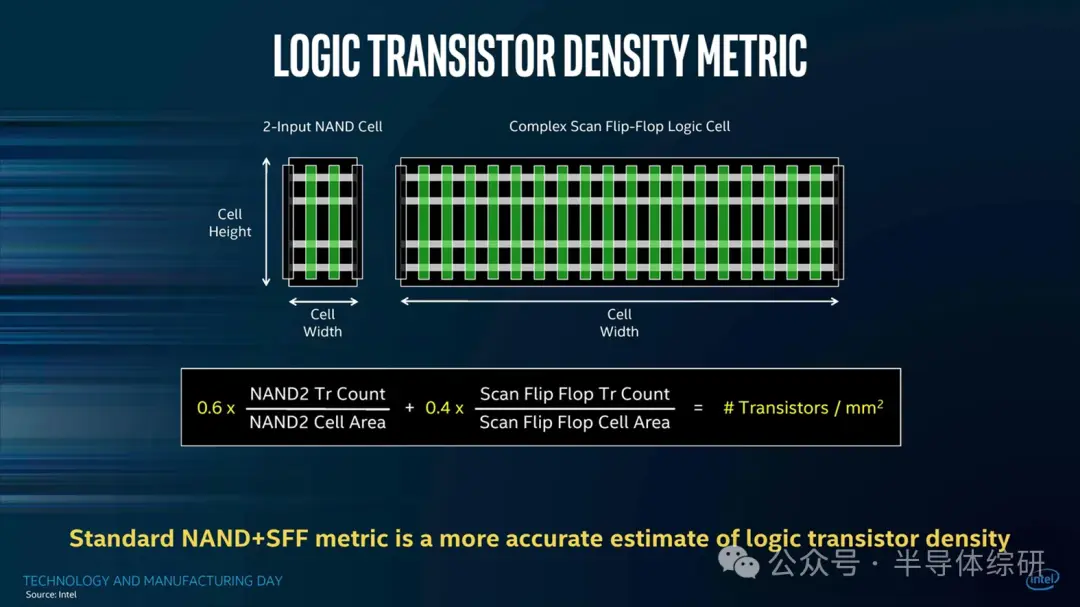

下圖是Intel官方資料里晶體管密度的標準算法。通過晶體管密度就可以等效換算工藝節點的nm數了

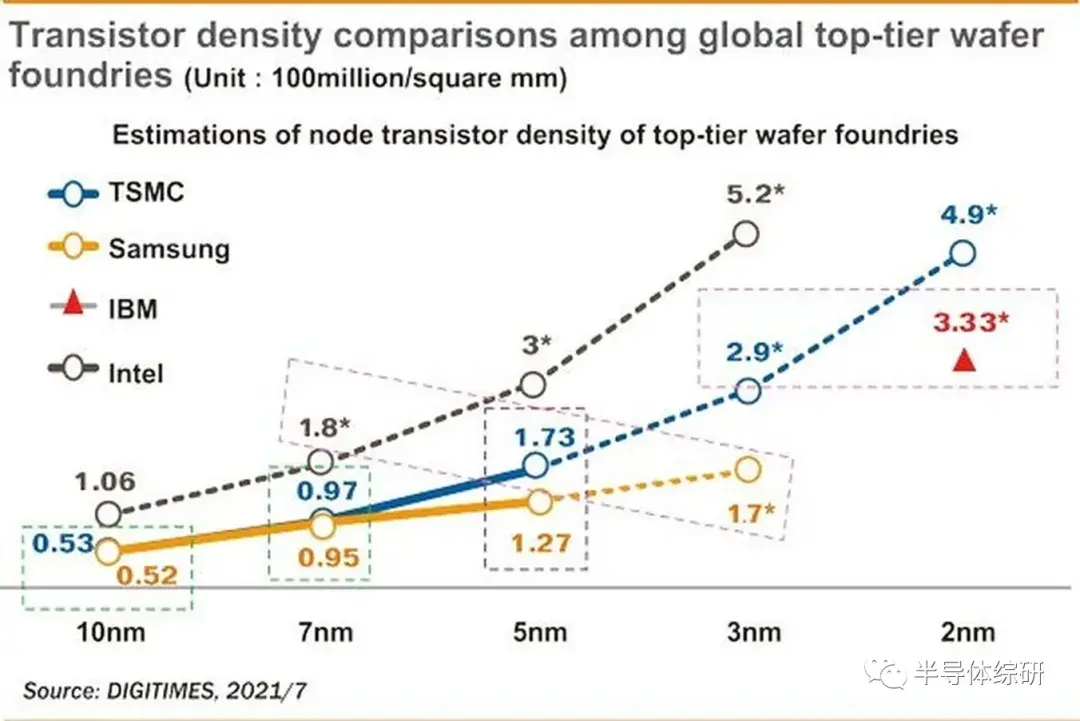

不過這個等效的計算方式各家也有不同依據,導致其中也有大量水分和貓膩。從下圖可見,不同廠家所謂的同一工藝節點上,實際晶體管密度都不一樣

以7nm為例,TSMC和三星的晶體管密度都分別只有每平方毫米0.97和0.95億個晶體管,而英特爾的7nm則達到1.8億個。所以不是晶圓制造領域的專業認識很容易被這些標稱線寬所迷惑

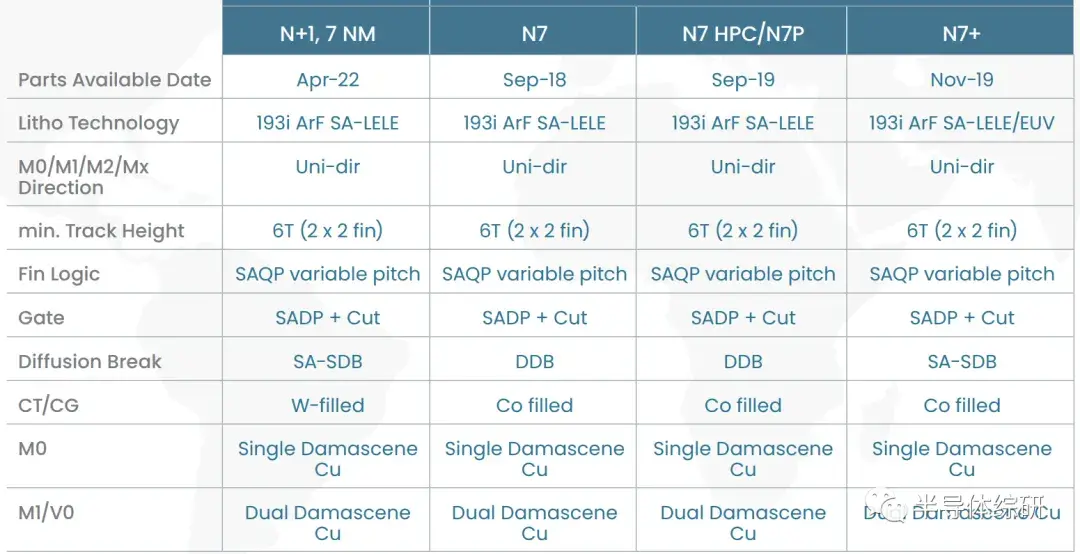

那行業內的人是用什么指標來具體衡量一個工藝的實際情況呢?大家不妨看看下圖中,Techinsight做的兩家晶圓廠7nm工藝技術的參數對比:

來源:半導體綜研

-

芯片

+關注

關注

459文章

52145瀏覽量

435981 -

晶體管

+關注

關注

77文章

9977瀏覽量

140628 -

7nm

+關注

關注

0文章

267瀏覽量

35631

發布評論請先 登錄

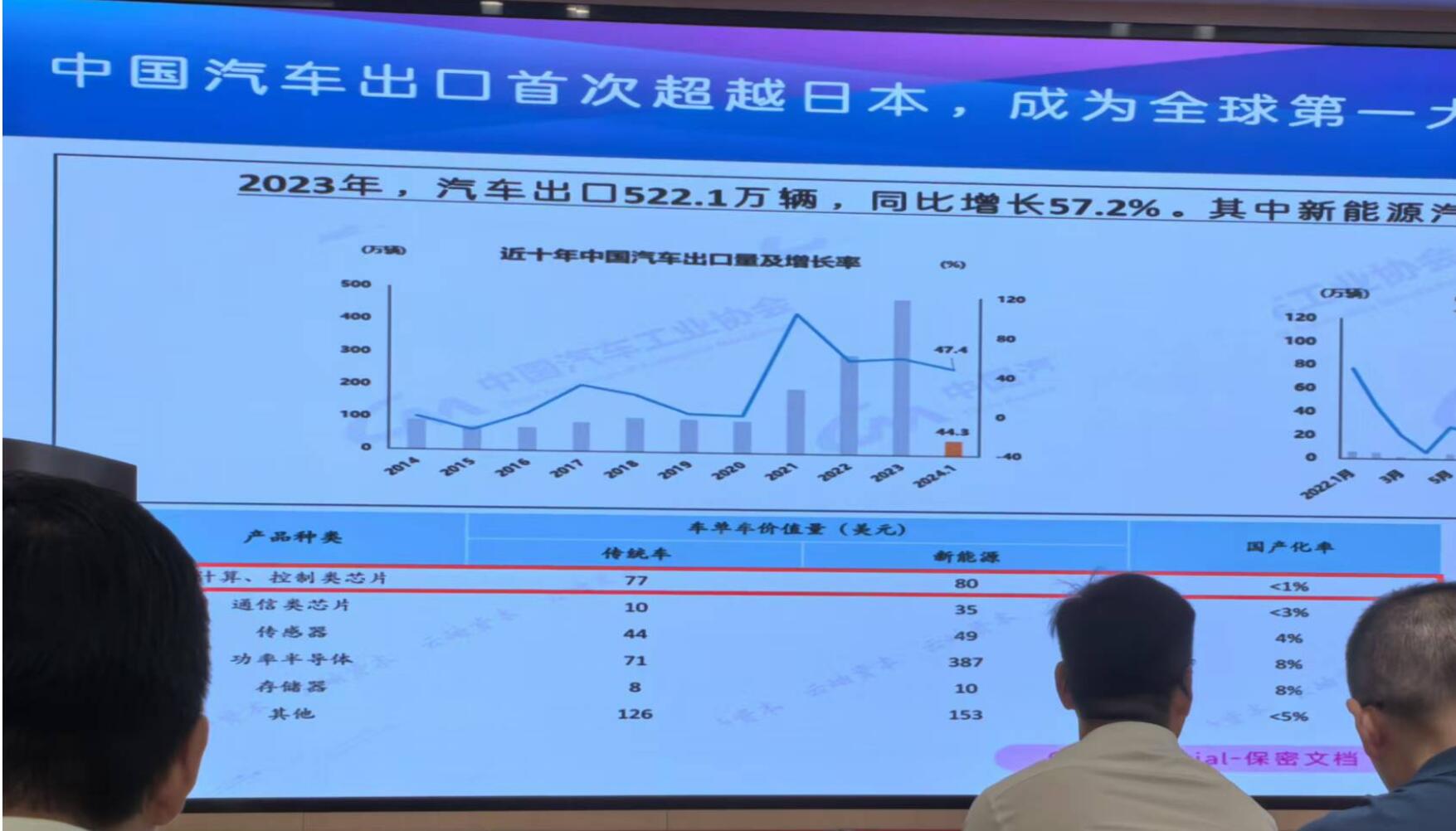

國產化率不足5%!國產7nm座艙芯片最新有哪些突破?

IBM Spectrum LSF如何助力半導體企業應對AI時代的高性能芯片需求

三星在4nm邏輯芯片上實現40%以上的測試良率

北京市最值得去的十家半導體芯片公司

DLP9500UV在355nm納秒激光器應用的損傷閾值是多少?

歐洲啟動1nm及光芯片試驗線

7納米工藝面臨的各種挑戰與解決方案

聯發科攜手臺積電、新思科技邁向2nm芯片時代

蘋果iPhone 17將首發搭載自研Wi-Fi 7芯片

今日看點丨 傳蘋果2025年采用自研Wi-Fi芯片 臺積電7nm制造;富士膠片開始銷售用于半導體EUV光刻的材料

4nm!小米 SoC芯片曝光!

臺積電產能分化:6/7nm降價應對低利用率,3/5nm漲價因供不應求

今日看點丨消息稱蔚來、小鵬等自研智駕芯片將流片;中國移動超級SIM芯片和MCU芯片采用PUF技術

張平安:中國AI發展核心在于行業應用的深度整合與全球大模型構建

可穿戴芯片進階至3nm!Exynos W1000用上了面板級封裝,集成度更高

所謂的7nm芯片上沒有一個圖形是7nm的

所謂的7nm芯片上沒有一個圖形是7nm的

評論