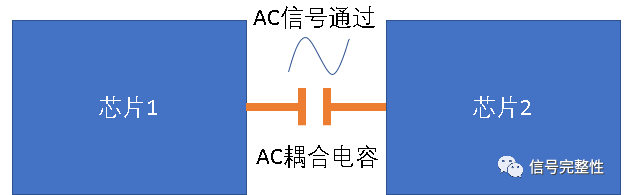

在很多高速串行信號(hào)中,都會(huì)使用到AC耦合電容,既然在設(shè)計(jì)高速串行電路時(shí),任何一個(gè)小小的不同都會(huì)引起信號(hào)完整性問(wèn)題,為什么要在串行鏈路中加入一個(gè)AC耦合電容呢?這個(gè)電容不僅會(huì)導(dǎo)致信號(hào)邊沿變得緩慢,還有可能會(huì)引起阻抗不連續(xù)。

當(dāng)我們連接有不同的供電電壓的兩個(gè)系統(tǒng)時(shí)或者是熱插拔時(shí),可能就會(huì)需要用到AC耦合電容了,首先我們要了解的是這里我們使用AC電容的目的是為了使兩級(jí)之間更好的通信,既然是串在了兩個(gè)系統(tǒng)之間,那通信的信號(hào)必然是交流的信號(hào)。AC耦合電容還可以提供直流偏壓和過(guò)流的保護(hù)。

在中間加個(gè)AC電容有什么好處呢?

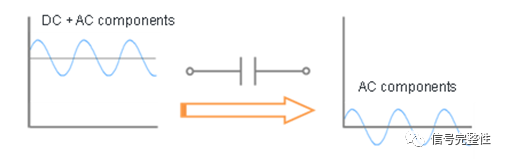

主要就是改善了噪聲容限。我們有時(shí)候可能在選擇電容時(shí)會(huì)選擇小電容,覺(jué)得這樣可能會(huì)將直流成分濾的更干凈,但是這樣會(huì)導(dǎo)致信號(hào)變形并且引起基線漂移。如果選擇較大的電容,電容端的電壓穩(wěn)定的時(shí)間需要的比較長(zhǎng),原來(lái)一個(gè)小小的電容要求有這么多,那我們應(yīng)該如何來(lái)選擇這個(gè)電容呢?首先要看電容的頻率、溫度等特性并且選擇低ESR/ESL的電容。對(duì)于電容值的選擇是要通過(guò)計(jì)算來(lái)選的,如下所示:

這里的F是截止頻率(定義電壓為輸入電壓的0.707倍時(shí)的頻率),R是傳輸線的阻抗,C是AC耦合電容。

當(dāng)然在選擇電容時(shí),其通帶的最小頻率要比傳輸信號(hào)的最小頻率要小才好,假設(shè)信號(hào)的最小頻率為Fmin,則頻率值為F:

F=Fmin/20

當(dāng)取值為F時(shí),99.88%的信號(hào)均會(huì)通過(guò)。

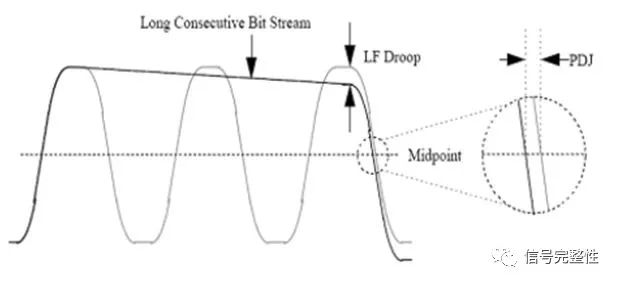

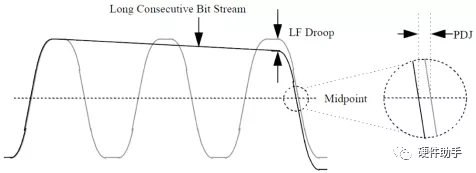

前面介紹了,雖然AC耦合電容有其好處,也會(huì)導(dǎo)致邊沿變緩慢,放置AC耦合電容時(shí),會(huì)引起阻抗的變化,就存在一個(gè)阻抗不連續(xù)點(diǎn)。同時(shí),也會(huì)引入碼型相關(guān)抖動(dòng),即當(dāng)電路傳輸?shù)男盘?hào)中出現(xiàn)連續(xù)的“1”或“0”時(shí),會(huì)出現(xiàn)下圖所示的直流電平壓降,這就會(huì)影響眼高。

如何才能減小這個(gè)直流壓降降低呢?

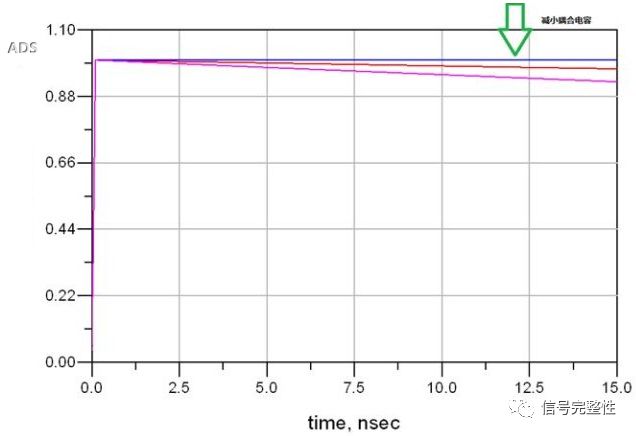

這和RC時(shí)間常數(shù)有關(guān),RC值越大(充電時(shí)間越長(zhǎng),單位時(shí)間電容充電少,分壓小),能通過(guò)的直流分量就越多直流壓降越小。由于鏈路中等效電阻是相對(duì)固定的,只能調(diào)節(jié)耦合電容值了。如下圖所示電容值越大,壓降越小。

曲線說(shuō)明:紫色的電容值最大,紅色的電容值次之,粉色的電容值最小。

那我們就把電容無(wú)限加大吧!

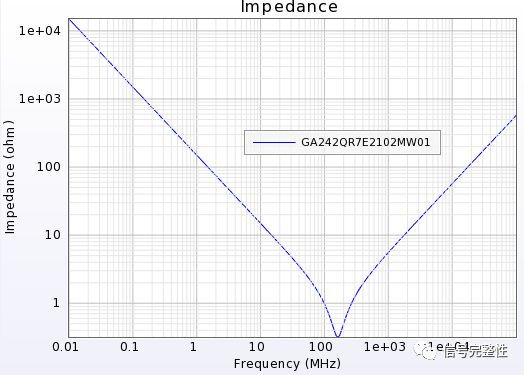

答案是:No,不行!因?yàn)椋瑢?shí)際安裝后的電容不是理想電容,除了ESR,ESL,還有安裝電感,所以就存在一個(gè)串聯(lián)諧振頻率。電容在串聯(lián)諧振頻率之前呈容性,之后呈感性。如下圖所示:

電容值越大,諧振頻率越小,電容在較低頻率就會(huì)呈現(xiàn)感性,這樣會(huì)造成信號(hào)高頻分量衰減增大,同樣會(huì)使眼高減小,上升沿變緩,jitter增加。

所以選擇AC耦合電容時(shí)要綜合以上兩點(diǎn)考量,一般業(yè)界都推薦0.01uF~0.2uF,最常見(jiàn)的就是0.1uF的電容。對(duì)于電容封裝的選擇不建議使用大于0603的封裝,最好是0402的,或者更小。

-

電容

+關(guān)注

關(guān)注

100文章

6228瀏覽量

153214 -

諧振頻率

+關(guān)注

關(guān)注

2文章

45瀏覽量

17167

原文標(biāo)題:關(guān)于高速電路中的AC耦合電容

文章出處:【微信號(hào):SI_PI_EMC,微信公眾號(hào):信號(hào)完整性】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

邏輯電平之AC耦合電容的應(yīng)用

AC耦合電容優(yōu)化(上)

AC耦合電容優(yōu)化(下)

在鏈路中加入一個(gè)AC耦合電容的原因是什么

AC耦合電容組裝結(jié)構(gòu)怎么優(yōu)化

別忽視!高速電路可能毀于未優(yōu)化的AC耦合電容

AC耦合電容的影響,你真的知道嗎?

AC耦合電容的選取

完成閉環(huán)設(shè)計(jì),基于仿真軟件的AC耦合電容阻抗優(yōu)化

ViaExpert仿真AC耦合電容阻抗優(yōu)化設(shè)計(jì)方案解析

為什么要在串行鏈路中加入一個(gè)AC耦合電容呢?

為什么要在串行鏈路中加入一個(gè)AC耦合電容呢?

評(píng)論