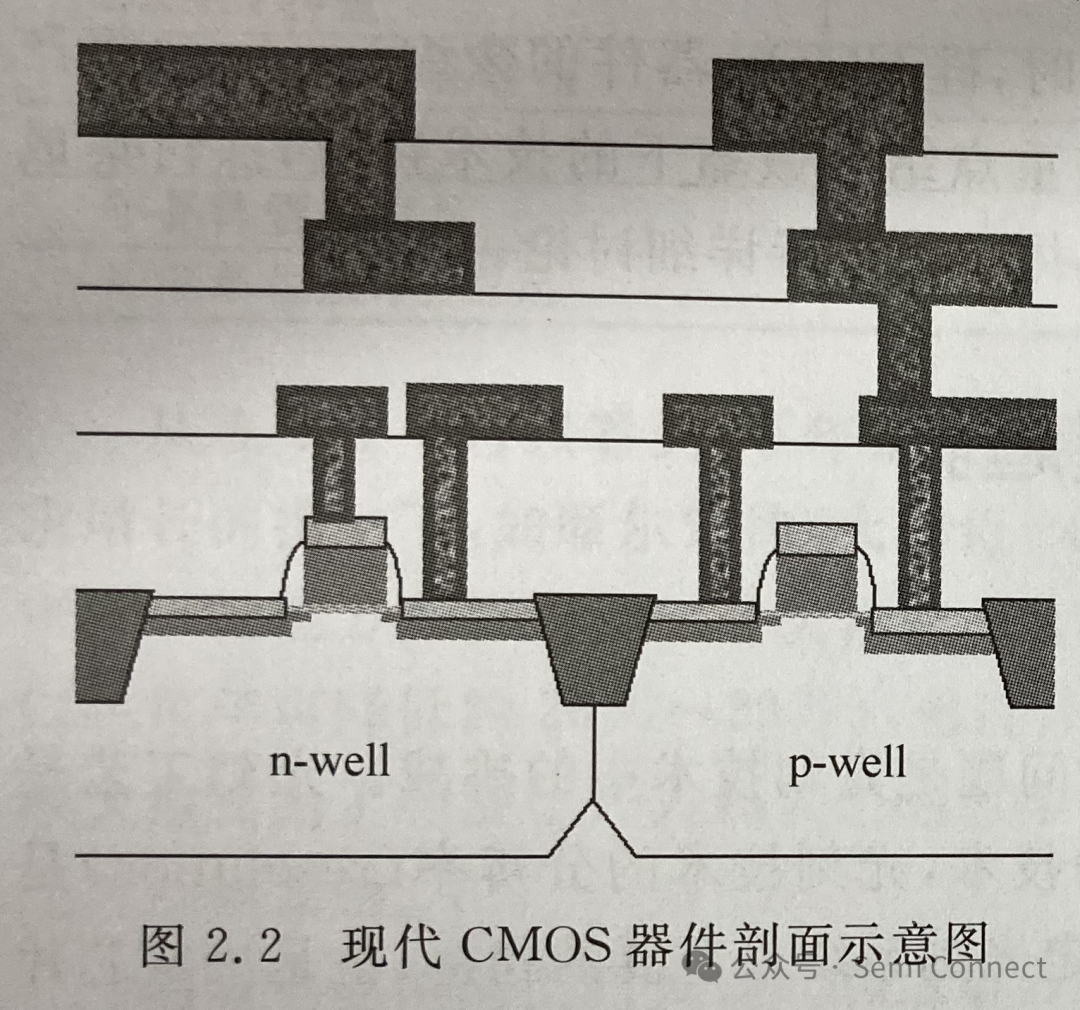

圖2.2是現(xiàn)代CMOS 器件剖面的示意圖。一般來說,水平方向的尺寸微縮幅度比垂直方向的幅度更大,這將導(dǎo)致溝槽(包含接觸孔)的深寬比(aspect ratio)也隨之提高,為避免溝槽填充過程中產(chǎn)生空穴(void),溝槽的填充工藝技術(shù)也不斷發(fā)展。從圖中可見,集成電路芯片的制造過程中包含很多種填充技術(shù)上的挑戰(zhàn),包括淺溝槽隔離、接觸孔和溝槽。根據(jù)填充材料的不同,填充工藝主要分為絕緣介質(zhì)的填充技術(shù)和導(dǎo)電材料的填充技術(shù)。

在大于0.8μm的間隙中填充絕緣介質(zhì)時(shí),普遍采用等離子體增強(qiáng)化學(xué)氣相沉積(Plasma Enhanced Chemical Vapor Deposition, PECVD);然而對于小于0.8μm 的間隙,用單步 PECVD 工藝填充間隙時(shí)會在其中部產(chǎn)生空穴。PECVD技術(shù)加上沉積-刻蝕-沉積工藝被用以填充0.5~0.8μm的間隙,也就是說,在初始沉積完成部分填孔尚未發(fā)生夾斷時(shí)緊跟著進(jìn)行刻蝕工藝以重新打開間隙入口,之后再次沉積以完成對整個(gè)間隙的填充。

高密度等離子(High Density Plasma, HDP)化學(xué)氣相沉積技術(shù)工藝在同一個(gè)反應(yīng)腔(chamber)中原位地進(jìn)行沉積和刻蝕的工藝,通過控制間隙的拐角處沉積刻蝕比(depositionetch ratio),使得凈沉積速率接近零,從而提高其填充能力。該技術(shù)能夠適應(yīng)深寬比在6:1左右的需求,并滿足 90nm 技術(shù)節(jié)點(diǎn)的需求。

當(dāng)集成電路發(fā)展到 65nm 技術(shù)節(jié)點(diǎn)時(shí),HDP工藝技術(shù)已經(jīng)不能滿足小尺寸溝槽的填充需求,因而發(fā)展出一種新的填充工藝技術(shù)即商深寬比工藝(High Aspect Ratio Process,HARP)。HARP 工藝采用 O3和 TEOS 的熱化學(xué)反應(yīng),沒有等離子體的輔助,同時(shí)需要溝槽具有特定的形貌,如特定角度的V 字形溝槽。該技術(shù)能夠適應(yīng)深寬比在7:1以上的需求。2008年,應(yīng)用材料公司又推出eHARP工藝技術(shù)以適應(yīng)32nm 工藝的需求。該技術(shù)在原有工藝引入水蒸氣,能夠提供無孔薄膜,用于填充小于30nm、深寬比大于12:1的空隙,從而滿足先進(jìn)存儲器件和邏輯器件的關(guān)鍵制造要求。

更進(jìn)一步地,在2010年8月,同樣是應(yīng)用材料公司推出第4代填充技術(shù),即流動(dòng)式化學(xué)氣相沉積(FCVD)技術(shù)。采用該技術(shù),沉積層材料可以在液體形態(tài)下自由流動(dòng)到需要填充的各種形狀的結(jié)構(gòu)中,填充形式為自底向上(bottom-up),而且填充結(jié)構(gòu)中不會產(chǎn)生空隙,能夠滿足的深寬比可超過30:1。這種獨(dú)特工藝能夠以致密且無碳的介電薄膜從底部填充所有這些區(qū)域,并且其成本相對低廉,僅是綜合旋轉(zhuǎn)方式的一半左右,后者需要更多的設(shè)備和很多額外的工藝步驟。

對于導(dǎo)電材料的填充技術(shù),早期的金屬沉積工藝采用物理氣相沉積(Physical VaporDeposition,PVD)工藝。但是,PVD技術(shù)的填充能力和臺階覆蓋能力都比較弱。為解決上述問題,化學(xué)氣相沉積(CVD)技術(shù)在接觸孔鎢栓填充上得到應(yīng)用。在工藝優(yōu)化后,CVD技術(shù)能夠提供保型沉積,這意味著比 PVD技術(shù)更為優(yōu)越的填充能力。當(dāng)集成電路工業(yè)引入銅互連技術(shù)后,不論 PVD還是CVD技術(shù)都不能滿足其填充能力的要求。研究發(fā)現(xiàn),電化學(xué)沉積(ECD)技術(shù)能夠提供更為優(yōu)越的填充技術(shù)以滿足銅互連技術(shù)中的挑戰(zhàn)。ECD 技術(shù)因其工藝具備自下而上(bottom-up)的特點(diǎn),因而具有更優(yōu)越的填充能力,對于高深寬比的間隙來說,這是一種理想的填充方式。在最近發(fā)展的替代柵工藝中,金屬沉積將面臨一些新的技術(shù)挑戰(zhàn)。

在接觸孔鎢栓填充、后端互連工藝銅填充以及后柵極工藝中的柵極填充中,一個(gè)共同的組成部分是阻擋層或晶籽層沉積或類阻擋層沉積,或可統(tǒng)一成為薄層金屬沉積。薄層金屬沉積需要良好的臺階覆蓋性(step coverage),傳統(tǒng)的 MOCVD或PVD工藝在阻擋層或晶籽層沉積上已經(jīng)沿用多年,隨著互連通孔尺寸的減小,臺階覆蓋等問題已經(jīng)成為限制其繼續(xù)應(yīng)用的瓶頸。原子層氣相沉積(Atomic Layer Deposition,ALD)技術(shù)正在逐步成為主流。

ALD過程是在經(jīng)過活性表面處理的襯底上進(jìn)行,首先將第一種反應(yīng)物引入反應(yīng)室使之發(fā)生化學(xué)吸附,直至襯底表面達(dá)到飽和;過剩的反應(yīng)物則被從系統(tǒng)中抽出清除,然后將第二種反應(yīng)物放入反應(yīng)室,使之和襯底上被吸附的物質(zhì)發(fā)生反應(yīng);剩余的反應(yīng)物和反應(yīng)副產(chǎn)品將再次通過泵抽或惰性氣體清除的方法清除干凈,這樣就可得到目標(biāo)化合物的單層飽和表面。這種ALD的循環(huán)可實(shí)現(xiàn)一層接一層的生長從而可以實(shí)現(xiàn)對沉積厚度的精確控制。ALD 技術(shù)在臺階覆蓋、側(cè)壁及底部覆蓋等方面都表現(xiàn)優(yōu)異,但是ALD沉積速率較低的劣勢也亟待改善。

ALD相比傳統(tǒng)的MOCVD和 PVD等沉積工藝具有先天的優(yōu)勢。它充分利用表面飽和反應(yīng)天生具備厚度控制能力及高度的穩(wěn)定性,對溫度和反應(yīng)物通量的變化不太敏感。這樣得到的薄膜既純度高、密度高、平整,又具有高度的保型性,即使對于縱寬比高達(dá)100:1的結(jié)構(gòu)也可實(shí)現(xiàn)良好的階梯覆蓋。ALD也順應(yīng)工業(yè)界向更低的熱預(yù)算發(fā)展的趨勢,多數(shù)工藝都可以在400°C以下進(jìn)行。由于 ALD是基于在交互反應(yīng)過程中的自約束性生長,此工藝必須經(jīng)過精細(xì)的調(diào)節(jié)來達(dá)到最合適的結(jié)果。

-

芯片

+關(guān)注

關(guān)注

459文章

52205瀏覽量

436457 -

集成電路

+關(guān)注

關(guān)注

5420文章

11956瀏覽量

367236 -

CMOS

+關(guān)注

關(guān)注

58文章

5995瀏覽量

238119 -

填充

+關(guān)注

關(guān)注

0文章

7瀏覽量

7248

原文標(biāo)題:溝槽填充技術(shù)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

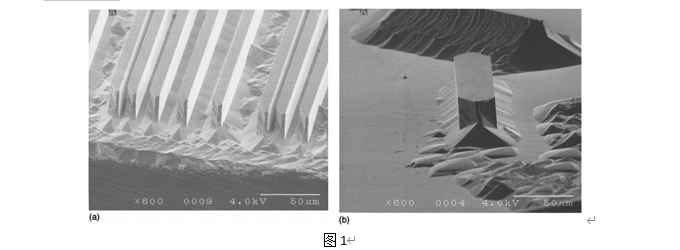

使用晶片處理技術(shù)在硅中產(chǎn)生溝槽結(jié)構(gòu)

溝槽結(jié)構(gòu)SiC-MOSFET與實(shí)際產(chǎn)品

CAD填充技巧之填充比例

CAD中怎么批量生成CAD填充邊界?

ASM啟用功新的PowerFill外延技術(shù)的電源設(shè)備

ASM啟用新的PowerFill外延技術(shù)的電源設(shè)備

cad填充圖案大全下載_cad填充圖案怎么安裝

PCB設(shè)計(jì)之填充過孔介紹

底部填充膠膠水如何填充芯片

SiC MOSFET:是平面柵還是溝槽柵?

填充寬度對于精確的焊盤填充過大的影響

填充膠是做什么用的?

拓荊科技:超高深寬比溝槽填充CVD產(chǎn)品首臺已通過客戶驗(yàn)證

溝槽結(jié)構(gòu)碳化硅的外延填充方法

溝槽填充技術(shù)介紹

溝槽填充技術(shù)介紹

評論