PCB 布線規(guī)則詳解

走線方向控制規(guī)則

相鄰布線層的走線方向應(yīng)采用正交結(jié)構(gòu),避免不同信號(hào)線在相鄰層沿同一方向走線,以此降低不必要的層間串?dāng)_。若因 PCB 板結(jié)構(gòu)限制(例如部分背板)難以避免該情況,特別是在信號(hào)速率較高時(shí),需利用地平面隔離各布線層,用地信號(hào)線隔離各信號(hào)線。

走線開環(huán)檢查規(guī)則

通常情況下,禁止出現(xiàn)一端浮空的布線(即 Dangling Line),這主要是為了防止“天線效應(yīng)”,減少不必要的干擾輻射與接收,否則可能引發(fā)難以預(yù)估的后果。

阻抗匹配檢查規(guī)則

同一網(wǎng)絡(luò)內(nèi)的布線寬度需保持一致,因?yàn)榫€寬變化會(huì)導(dǎo)致線路特性阻抗不均勻。當(dāng)信號(hào)傳輸速度較高時(shí),阻抗不均勻會(huì)產(chǎn)生反射現(xiàn)象,所以在設(shè)計(jì)過程中應(yīng)盡量避免這種情況。

走線長(zhǎng)度控制規(guī)則(短線規(guī)則)

設(shè)計(jì)時(shí),應(yīng)盡量縮短布線長(zhǎng)度,以減少因走線過長(zhǎng)帶來的干擾問題。對(duì)于一些關(guān)鍵信號(hào)線,如時(shí)鐘線,務(wù)必確保振蕩器與器件距離較近。

倒角規(guī)則

在 PCB 設(shè)計(jì)過程中,要避免出現(xiàn)銳角和直角走線。此類走線不僅會(huì)產(chǎn)生不必要的輻射,還會(huì)影響工藝性能。

器件去耦規(guī)則

在印制板上添加必要的去耦電容,能夠有效濾除電源上的干擾信號(hào),從而保證電源信號(hào)的穩(wěn)定性。

地線回路規(guī)則(環(huán)路最小規(guī)則)

信號(hào)線與其回路構(gòu)成的環(huán)面積應(yīng)盡可能小。環(huán)面積越小,對(duì)外輻射越少,同時(shí)接收外界干擾的能力也越弱。

電源與地線層的完整性規(guī)則

在導(dǎo)通孔密集的區(qū)域,要特別注意避免孔在電源層和地層挖空區(qū)域相互連接,以免形成對(duì)平面層的分割,破壞平面層的完整性,進(jìn)而導(dǎo)致信號(hào)線在地層的回路面積增大。

屏蔽保護(hù)規(guī)則

該規(guī)則與地線回路規(guī)則相呼應(yīng),旨在盡量減小信號(hào)的回路面積,常見于一些重要信號(hào),如時(shí)鐘信號(hào)、同步信號(hào)等。

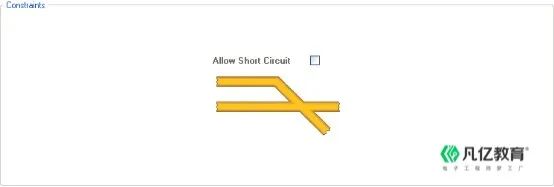

走線閉環(huán)檢查規(guī)則

要防止信號(hào)線在不同層間形成自環(huán)。在多層板設(shè)計(jì)中,這種情況較易發(fā)生,而自環(huán)會(huì)引發(fā)輻射干擾。

孤立銅區(qū)控制規(guī)則

孤立銅區(qū)的出現(xiàn)可能會(huì)引發(fā)一些不可預(yù)知的問題,因此應(yīng)將孤立銅區(qū)與其他信號(hào)連接,這有助于改善信號(hào)質(zhì)量。通常的做法是將孤立銅區(qū)接地或直接刪除。

審核編輯 黃宇

-

pcb

+關(guān)注

關(guān)注

4349文章

23403瀏覽量

406391 -

布線

+關(guān)注

關(guān)注

9文章

790瀏覽量

84867

發(fā)布評(píng)論請(qǐng)先 登錄

PCB布局與布線規(guī)則

時(shí)源芯微 EMC抗擾措施

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

Altium Designer中PCB設(shè)計(jì)規(guī)則設(shè)置

高速信號(hào)線走線規(guī)則有哪些

104條關(guān)于PCB布局布線的小技巧

時(shí)源芯微EMC前車燈案例

了解TI基于PCB布線規(guī)則的DDR時(shí)序規(guī)范

時(shí)源芯微 PCB 布線規(guī)則詳解

時(shí)源芯微 PCB 布線規(guī)則詳解

評(píng)論