溝道有效遷移率(μeff)是CMOS器件性能的關鍵參數。傳統測量方法在高k介質、漏電介質與高速應用中易出現誤差。本文介紹了UFSP(Ultra-Fast Single Pulse)技術如何準確提取遷移率,克服這些挑戰。

傳統移動性測量及其挑戰

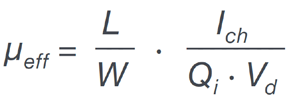

我們以柵極長度為L、寬度為W的p溝道器件為例。當溝道電荷在線性區域中從源極到漏極相當均勻時,溝道有效遷移率 (μeff) 可寫為

(1)

其中Vd是施加在器件漏極上的小偏壓,Qi是移動溝道電荷密度 (C/cm2),Ich是流經溝道的傳導電流。

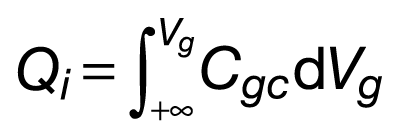

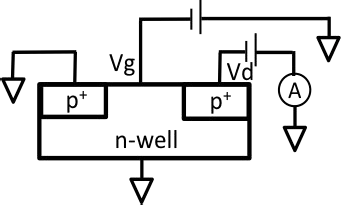

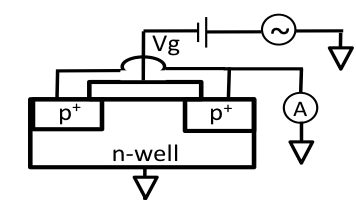

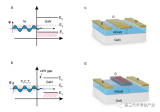

傳統上,Ich是在器件的漏極端子處測量的,其配置如圖1(a)所示。Qi是通過對測量的柵極 - 溝道電容 Cgc相對于Vg進行積分得出的,即

(2)

使用圖1(b)所示的連接配置。

圖1. (a) 傳導電流測量和 (b) 柵極至溝道電容Cgc測量的配置。

傳統遷移率測量的原理看似簡單,但這種測試存在許多挑戰和陷阱。過去,人們常常忽略一些誤差源。

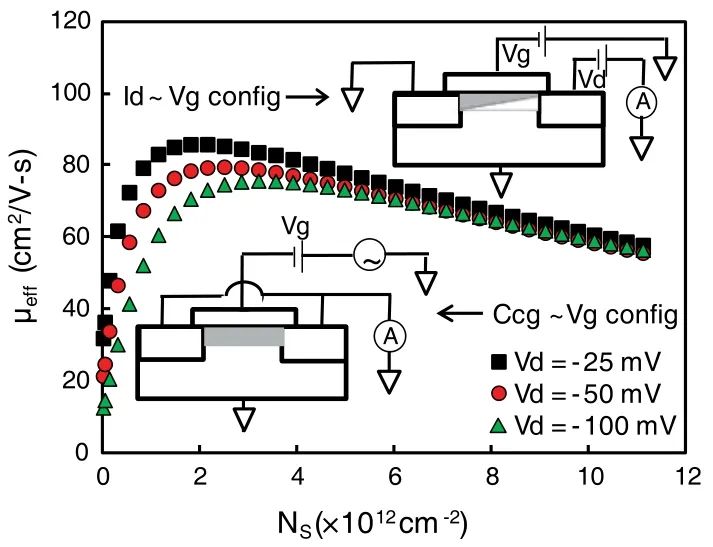

Vd依賴性:傳統技術對Ich測量應用不為0的Vd( 通常為50mV–100mV),但對Q測量應用零V。用于測量Ich的V之間的這種差異兩次測量可能導致在評估薄氧化物遷移率時出現嚴重錯誤,尤其是在低電場區域。圖2給出了一個例子,其中較高的 |Vd| 導致峰值附近的遷移率大幅降低。這是因為 |Vg– Vd| 在高 |Vd| 時會降低,因此Ich的實際電荷載流子密度小于在Vd= 0 時測得的Qi。

圖2. 通過傳統技術測量的有效溝道遷移率。Ich是在各種非零漏極偏壓VDS下測量的,但Qi是在 Vd= 0 下測量的。提取的遷移率隨著 |Vd| 的升高而明顯降低。插圖顯示了載流子分布在溝道。

電荷捕獲:傳統技術采用慢速測量,典型測量時間以秒為單位。快速電荷捕獲對于薄SiON和高k電介質都很重要。對于慢速測量,捕獲可以在測量過程中做出響應,并導致Cgc–Vg曲線的滯后和延伸,以及Ich。這導致對流動性的低估。

漏電介質:隨著柵極氧化物的縮小,高柵極漏電流成為遷移率提取的主要挑戰。它會影響Ich和Qi測量,進而影響遷移率。為了最大限度地減少其對Cgc測量的影響,已經使用了高達千兆赫的頻率,這需要具有RF結構的設備。RF結構需要更多的處理和芯片空間,而且并不總是可用的。

電纜切換:傳統技術涉及在Ich和Qi測量之間切換電纜。這會減慢測量速度,并可能導致被測設備發生故障。

超快速單脈沖技術(UFSP技術)

為了克服上述挑戰,我們開發了一種稱為超快速單脈沖技術 (UFSP) 的新技術,如下所述。

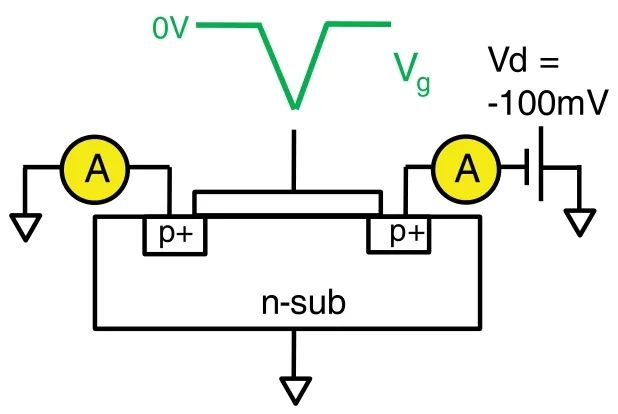

如圖3所示。n溝道器件的考慮因素類似。要進行UFSP測量,在器件的柵極端施加一個邊緣時間為幾微秒的單脈沖。柵極電壓在測量期間向負方向掃描脈沖下降沿并打開器件。瞬態電流記錄在器件的源極和漏極端子處。然后在柵極電壓向正方向掃描的后續上升沿期間關閉器件。相應的瞬態電流也將被記錄。可以從在幾個測量周期內測量的這四個瞬態電流中提取溝道有效遷移率微秒。

圖3. UFSP技術工作原理圖。

圖4. 瞬態測量過程中電流流動的示意圖。

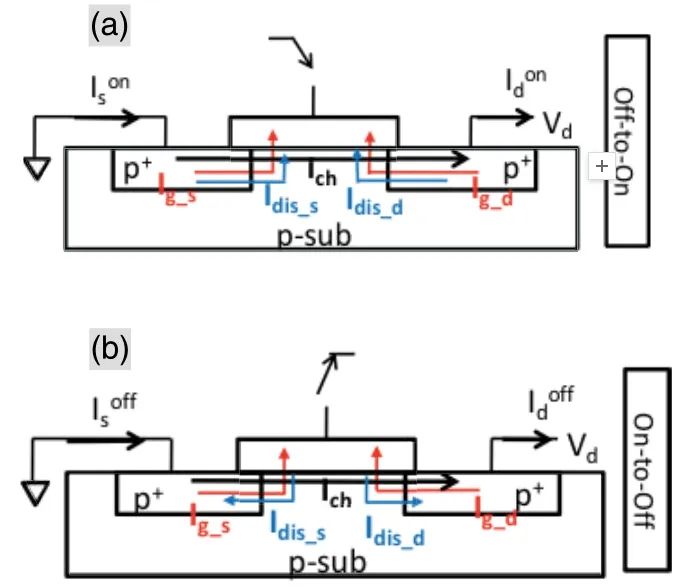

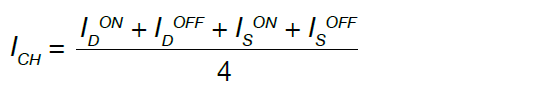

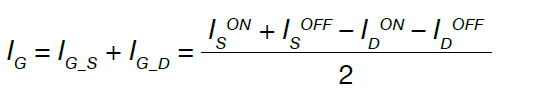

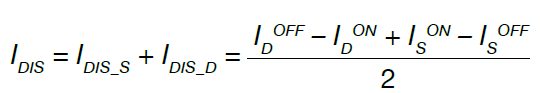

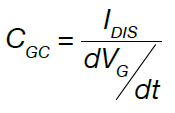

為了便于分析,我們將器件開啟和關閉時在漏極和源

極端子處測得的電流定義為 Idon、Ison、Idoff和Isoff。瞬態測量過程中溝道中的電流如圖4(a)和(b)所示。存在三種類型的電流:溝道傳導電流Ich、柵極與源極/漏極之間的位移電流Idis_s和Idis_d以及柵極與源極 /漏極之間的漏電流 Ig_s和Ig_d。當器件從關閉切換到開啟時,Idis_s和Idis_d的方向朝向溝道中心; Idis_s與源極處的Ich方向相同,但Idis_d與漏極處的Ich方向相反。當器件從開啟切換到關閉時,Idis_s和Idis_d會發生變化方向,但Ich則不然。Ig_s和Ig_d與Vg掃描無關g下始終從源極和漏極流向柵極。基于上述分析,溝道電流Ich、柵極電流Ig和位移電流Idis可利用公式(2)- (4) 分離。Cgc可利用公式 (5) 計算。

(1)

(2)

(3)

(4)

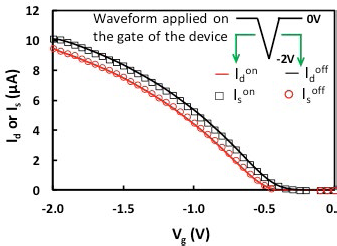

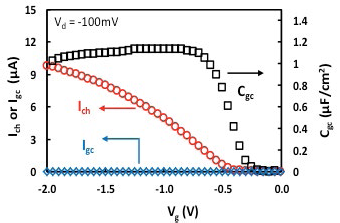

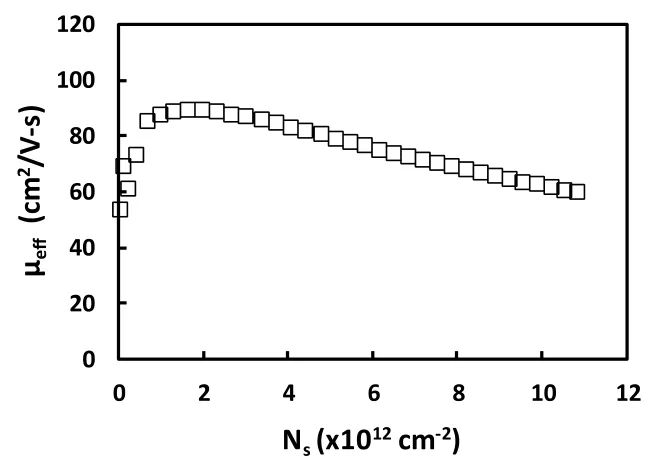

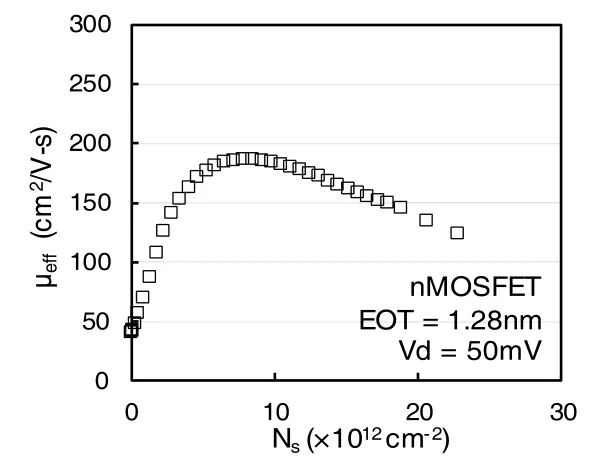

為了校準UFSP技術,使用具有厚氧化物的p溝道MOSFET,其 IG電流可忽略不計。測量時間(=邊緣時間)設置為3μs。圖5顯示了測量的四個電流。Ich、 克和使用公式(2)至(5)提取的Cgc顯示在圖6(a).準確評估Cgc和Ich后,即可通過對Cgc和Vg進行積分來獲得Qi,并通過公式 (1) 計算出溝道有效遷移率μeff,如圖6(b)所示。

圖5. 對應于關斷至開和開至關Vg掃描的源極和漏極測量的四個電流。插圖中顯示了Vg波形示意圖。

圖6.(a). 利用公式(2)-(5)從圖5中的電流中同時提取Ich、Ig和Cgc。(b) 從Ich提取的通道有效遷移率,從(a)中提取的Cgc。

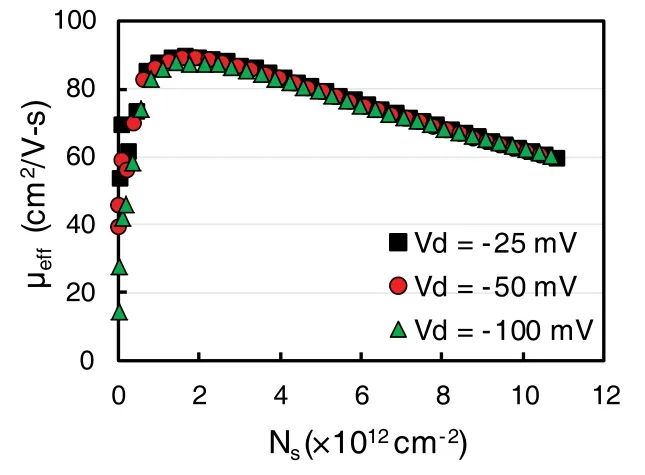

由于UFSP在相同的Vd下測量了Ich和Cgc,μeff應與Vd無關。圖7比較了在三種不同的Vd偏置下評估的μeff。結果一致,證實使用傳統技術可以消除Vd引起的誤差已刪除。

圖7. 用UFSP技術在三種不同Vd下提取的有效溝道遷移率μeff。

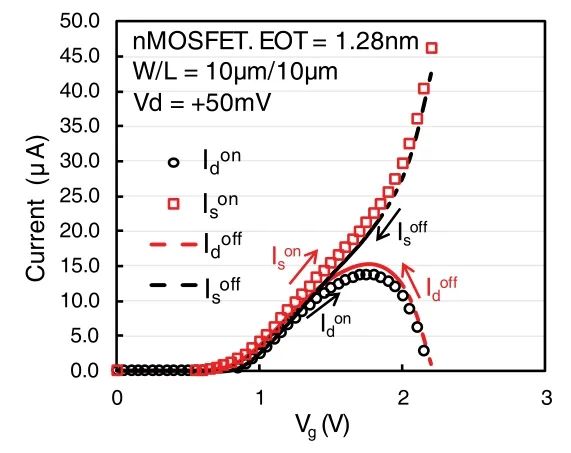

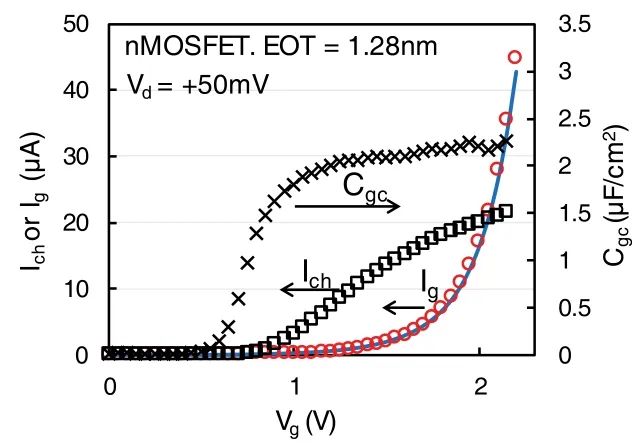

UFSP在標準結構的漏電柵介質上也能很好地工作。當將其應用于一個EOT為1.28nm的“漏電”n溝道MOSFET時,從源極和漏極端子測量的四個電流對應于圖8(a)顯示了關斷到開和開到關的VG掃描。利用公式 (2)-(5),Ich('n'), Ig('o') and Cgc('x') 提取并繪制在圖8(b)中。圖8(b)還繪制了直流測量的Ig以供比較。結果一致。圖8(c)表明,對于Ig高達 45A/cm2的漏電器件,可以可靠地測量電子遷移率。由于UFSP 可以容忍高柵極漏電,因此不需要使用用于移動性評估的特殊RF結構。

圖8.(a) 從source和drain測量的四個電流,對應于在EOT為1.28nm的nMOSFET上通過UFSP技術進行的off-on-on和on-off Vg掃描。

(b) Ich('n'), Ig('o') 和Cgc('x')由公式(2) - (5)從(a)中的電流中提取。藍線是通過直流測量獲得的泄漏電流。

(c) 通道有效遷移率μeff是通過使用提取的Ich和Cgc與 Eqn(1)來計算的。

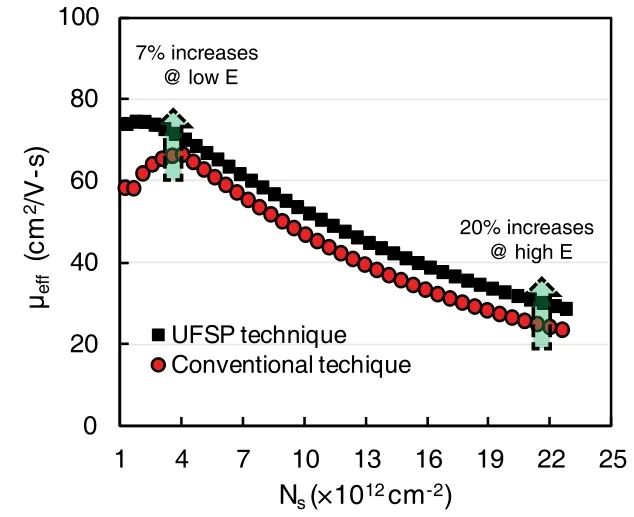

為了證明UFSP對具有顯著電荷捕獲的器件的適用性,我們使用了一個具有HfO2/SiO2堆棧的 pMOSFET。大量陷阱位于此介電堆棧中 Si/SiO2界面附近,它們可以快速與基板交換電荷。傳統技術需要幾秒鐘,因此無法將它們與溝道移動電荷區分開來。

因此,反轉電荷 將要電荷捕獲效應會被高估,反過來,溝道有效遷移率會被低估。UFSP技術只需要幾微秒的時間,最大限度地減少了電荷捕獲效應。圖9比較了這兩種技術提取的遷移率。很明顯,在抑制電荷捕獲后,UFSP提取的遷移率比傳統技術高得多技術。

圖9. 通過UFSP和常規技術提取的具有相當快速捕獲的HfO2/SiON電介質器件的遷移率比較。

UFSP測量所需的硬件

選擇合適的測量設備對于成功實施超快速單脈沖方法至關重要。需要以下硬件:

■一臺4200A-SCS型參數分析儀

■ 兩個超快IV模塊(4225-PMU)

■四個遠程放大器/開關(4225-RPM)

■ 4 高性能三軸電纜套件(4210-MMPC-C)

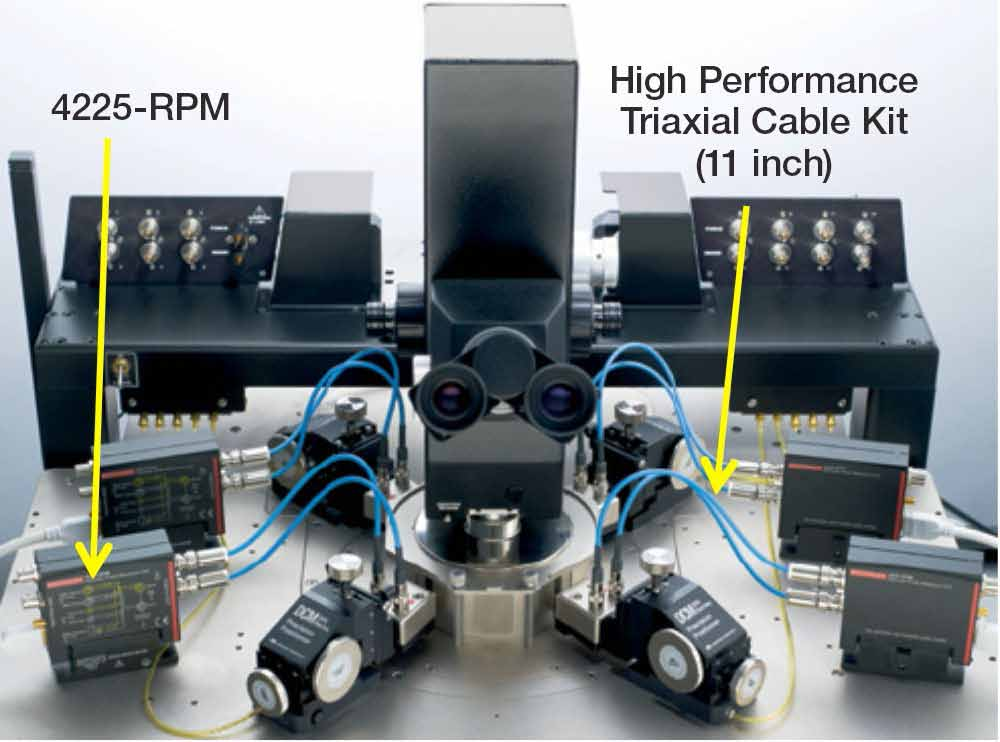

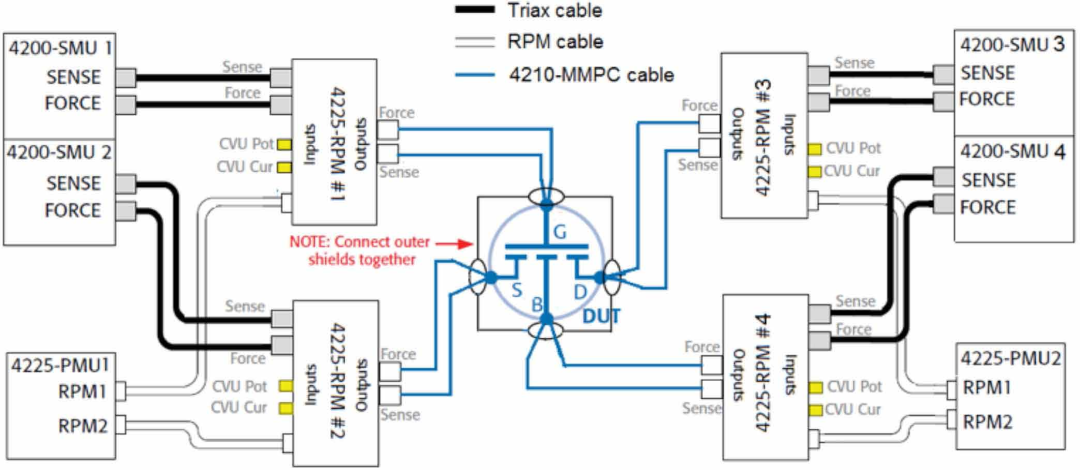

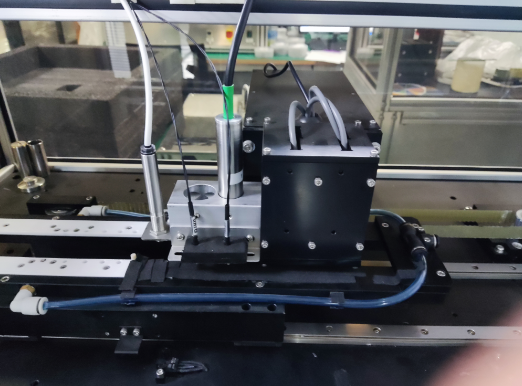

圖10顯示了測試的布線配置照片。4225-PMU是4200A-SCS參數分析儀的儀器選項范圍不斷擴大。該模塊集成了超快速電壓波形生成和信號觀察功能且融入了4200A-SCS已經很強大的測試環境,提供前所未有的IV測試性能。它使超快速IV源和測量變得與使用傳統高分辨率源測量單元(SMU)儀器進行直流測量一樣簡單。每個插入式4225-PMU模塊提供兩個集成源和測量溝道測量。每個渠道的這4225-PMU結合高速電壓輸出(脈沖寬度范圍從60ns到DC),同時測量電流和電壓。4225-RPM遠程放大器/開關通過提供超低電流測量(低于100nA)和降低電纜電容,進一步擴展了4225-PMU的功能 效果。

圖10.UFSP技術硬件設置

設備連接

如圖11所示。設備的每個端子都使用兩根11英寸三軸電纜(電纜套件4210-MMPC-C中提供)連接到一個 4225-RPM。 然后,每個4225-RPM都使用兩根三軸電纜連接到PMU的一個溝道。所有測量均由Clarius 控制軟件。

圖11. 超快速單脈沖 (UFSP) 技術的實驗連接。兩個Keithley雙溝道4225-PMU用于執行瞬態測量。四個Keithley 4225-RPM用于降低電纜電容效應并實現低于100nA的精確測量。

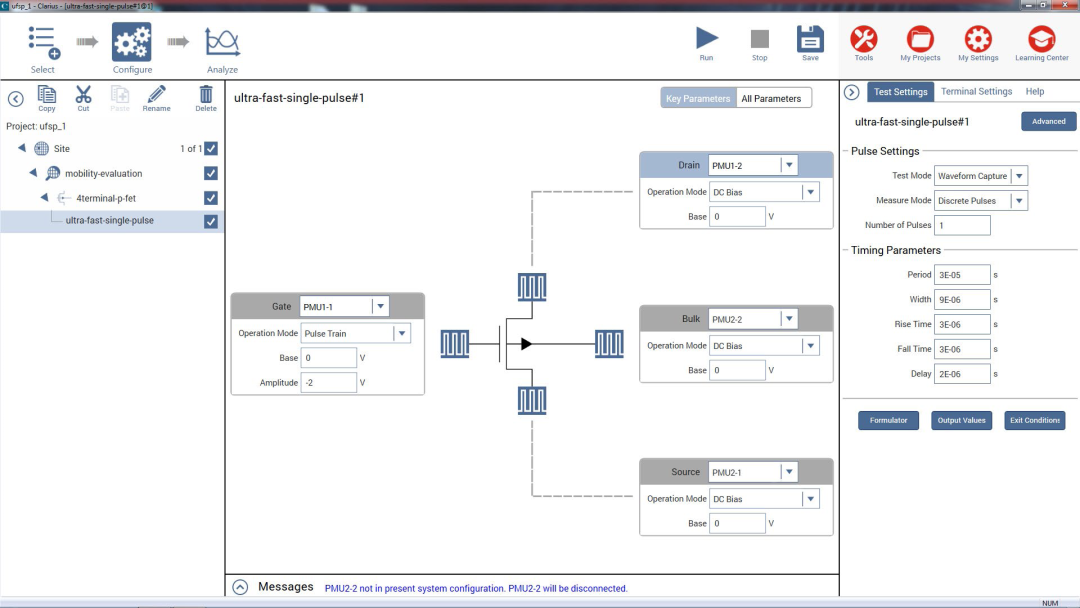

圖12. Clarius軟件中用于UFSP測量的示例項目。該設備的四個端子分別連接到PMU的一個溝道。

使用Clarius軟件進行UFSP測量

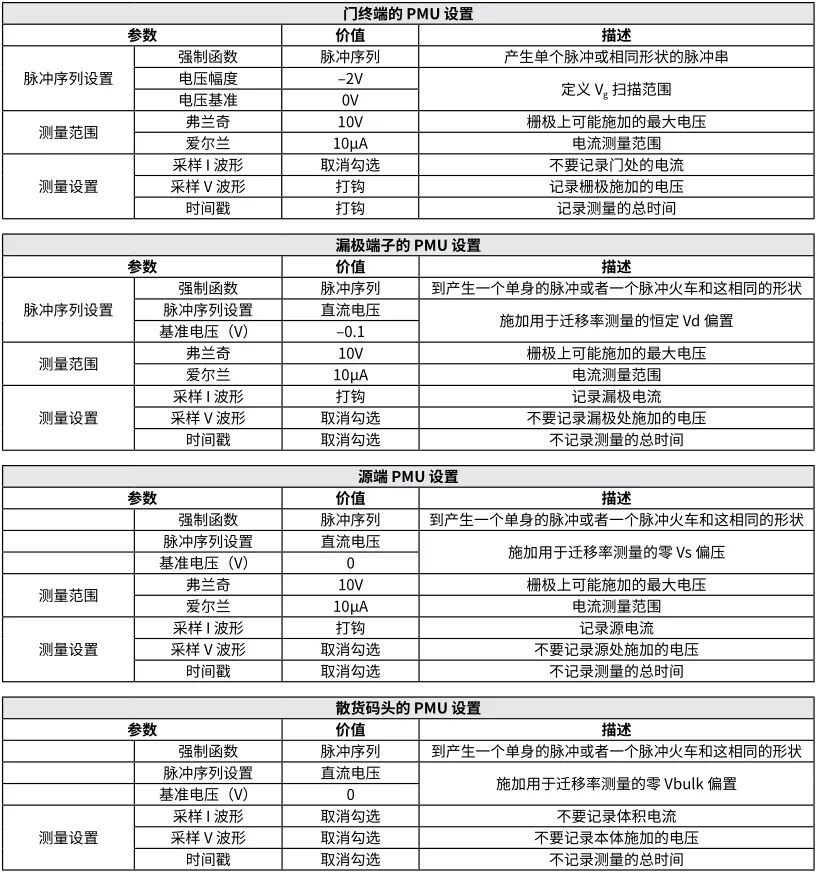

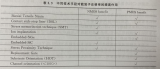

使用4200A-SCS系統執行UFSP進行溝道有效遷移率測量非常簡單。系統附帶一個示例項目。如圖12所示,設備的每個端子連接到一個溝道PMU。用戶可以在定義選項卡中修改每個PMU溝道的參數。表1列出了一組p溝道MOSFET的用戶定義參數。

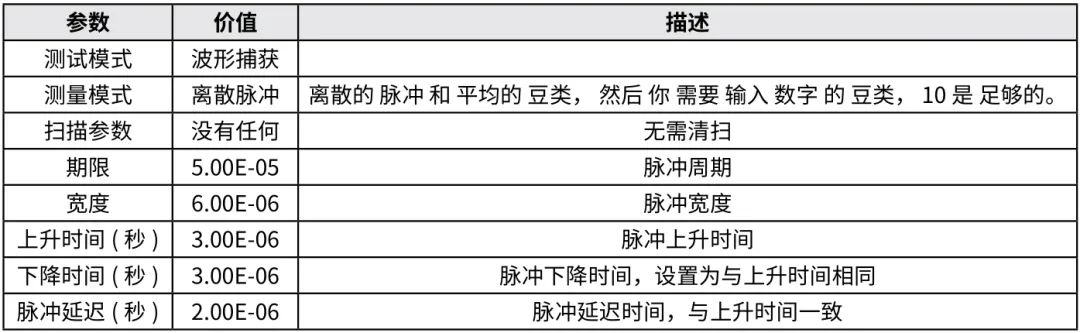

在Test Setings面板中,用戶可以輸入想要的測量速度,也就是脈沖的邊沿時間,推薦值如表2所示。

表1. PMU 各個溝道定義選項卡中的推薦設置。

表2. 時間選項卡中的推薦設置。

執行測試后,源極和漏極端子打開和關閉期間的瞬態電流將被記錄并存儲在工作表中,并可保存為.xls文件。這些電流也可以繪制在圖形選項卡上。從這些電流中,可以根據公式(2)提取溝道有效遷移率(5)。

結論

UFSP技術通過創新的脈沖測量方法,在微秒級內實現精確遷移率提取。特別適用于CMOS工藝開發、材料評估與器件建模,是現代半導體測試的重要利器。

-

CMOS

+關注

關注

58文章

5994瀏覽量

238117 -

MOSFET

+關注

關注

150文章

8276瀏覽量

218597 -

半導體

+關注

關注

335文章

28613瀏覽量

232803 -

源極

+關注

關注

1文章

54瀏覽量

8349 -

單脈沖

+關注

關注

0文章

28瀏覽量

12864

原文標題:從慢測到快取:如何精準提取MOSFET溝道遷移率?

文章出處:【微信號:泰克科技,微信公眾號:泰克科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

N溝道和P溝道MOSFET的區別是什么

載流子遷移率測量方法總結

載流子輸運現象之散射率、遷移率、電阻率、砷化鎵

MXene范德華接觸在氮化鎵高電子遷移率晶體管中的應用

8.2.10.3 4H-SiC反型層遷移率的實驗結果∈《碳化硅技術基本原理——生長、表征、器件和應用》

8.2.10.1 影響反型層遷移率的機理∈《碳化硅技術基本原理——生長、表征、器件和應用》

8.2.10.2 反型層遷移率的器件相關定義∈《碳化硅技術基本原理——生長、表征、器件和應用》

如何通過霍爾效應測量半導體中電子和空穴的遷移率?

高電子遷移率晶體管介紹

如何精準提取MOSFET溝道遷移率

如何精準提取MOSFET溝道遷移率

評論