定制化SoC陣列設(shè)計(jì)融合了多核異構(gòu)集成與分布式計(jì)算架構(gòu),其核心在于根據(jù)不同應(yīng)用場(chǎng)景的需求,通過(guò)硬件模塊化設(shè)計(jì)和軟件定義能力實(shí)現(xiàn)算力密度與能效比的突破。以下是關(guān)鍵設(shè)計(jì)要素與技術(shù)特征:

一、架構(gòu)設(shè)計(jì)原則

異構(gòu)集成架構(gòu)?

采用CPU+GPU+NPU+專(zhuān)用加速器的組合模式,支持動(dòng)態(tài)資源分配與硬件虛擬化技術(shù),例如芯原平臺(tái)支持多處理器協(xié)同工作并可選配ASIL D級(jí)功能安全島

模塊化擴(kuò)展性?

通過(guò)PCIe 5.0/CXL 2.0高速互連協(xié)議構(gòu)建彈性集群,單節(jié)點(diǎn)支持3D封裝集成內(nèi)存與計(jì)算核心,實(shí)現(xiàn)TB/s級(jí)帶寬擴(kuò)展

二、核心技術(shù)實(shí)現(xiàn)

先進(jìn)工藝優(yōu)化?

針對(duì)5nm/7nm車(chē)規(guī)工藝進(jìn)行PPA(功耗/性能/面積)優(yōu)化,結(jié)合Chiplet技術(shù)實(shí)現(xiàn)不同制程芯片的異構(gòu)集成

高速互連系統(tǒng)?

采用光互連總線(xiàn)探索量子-經(jīng)典計(jì)算混合架構(gòu),通過(guò)低延時(shí)通信網(wǎng)絡(luò)支持AI推理、邊緣計(jì)算等混合負(fù)載

三、功能安全特性

基于ISO 26262認(rèn)證的設(shè)計(jì)流程,集成硬件級(jí)安全隔離引擎,實(shí)現(xiàn)多租戶(hù)場(chǎng)景下的數(shù)據(jù)安全防護(hù)

在自動(dòng)駕駛決策系統(tǒng)中,通過(guò)冗余計(jì)算單元和實(shí)時(shí)監(jiān)控機(jī)制保障功能安全完整性等級(jí)(ASIL)達(dá)D級(jí)

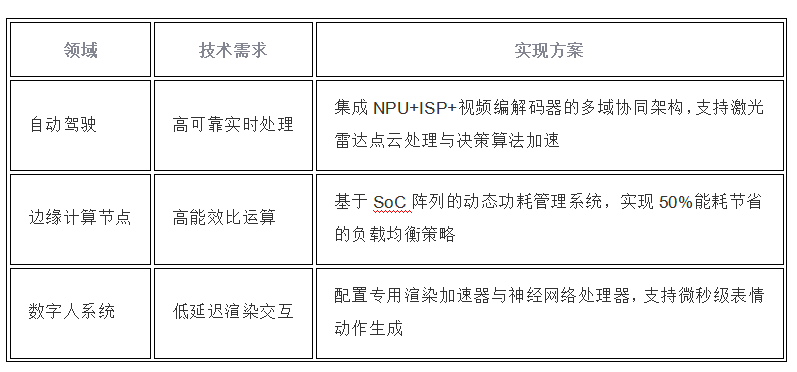

四、典型應(yīng)用場(chǎng)景

五、設(shè)計(jì)流程創(chuàng)新

平臺(tái)即服務(wù)(SiPaaS)模式?:提供從芯片架構(gòu)設(shè)計(jì)、驗(yàn)證到車(chē)規(guī)認(rèn)證的全流程服務(wù),包含安全需求分析、失效模式驗(yàn)證等20余項(xiàng)認(rèn)證支持

自動(dòng)化設(shè)計(jì)工具鏈?:支持RISC-V與ARM指令集混合編排,實(shí)現(xiàn)IP核的靈活調(diào)用與驗(yàn)證覆蓋率優(yōu)化

這種設(shè)計(jì)范式已成功應(yīng)用于智能座艙域控芯片,例如高通驍龍8775通過(guò)座艙域與智駕域的深度協(xié)同,實(shí)現(xiàn)4K導(dǎo)航渲染與HUD預(yù)警聯(lián)動(dòng)的實(shí)時(shí)響應(yīng)能力。未來(lái)發(fā)展趨勢(shì)聚焦于Chiplet互聯(lián)標(biāo)準(zhǔn)化與光子計(jì)算集成,預(yù)計(jì)可將陣列服務(wù)器能效比再提升3-5倍。

審核編輯 黃宇

-

soc

+關(guān)注

關(guān)注

38文章

4335瀏覽量

221649 -

陣列

+關(guān)注

關(guān)注

0文章

65瀏覽量

17004

發(fā)布評(píng)論請(qǐng)先 登錄

高通SoC陣列服務(wù)器

集成Docker,解鎖 HMI/網(wǎng)關(guān)的定制化應(yīng)用

SoC集群服務(wù)器 與 ARM架構(gòu)陣列服務(wù)器 關(guān)系

基于RK芯片的主板定制化:挑戰(zhàn)、機(jī)遇與發(fā)展趨勢(shì)

RAKsmart美國(guó)裸機(jī)云服務(wù)器DeepSeek的高級(jí)定制化部署方案

FRED案例:矩形微透鏡陣列

電子位移監(jiān)測(cè)技術(shù)綜述:測(cè)斜儀、陣列式與節(jié)段式的區(qū)別及選型指南

微透鏡陣列后光傳播的研究

通過(guò)微透鏡陣列的傳播

SG EVO:量身定制的射頻測(cè)試系統(tǒng)

通過(guò)微透鏡陣列的傳播

資料保存1:工業(yè)定制化儀器設(shè)計(jì)方案

詳談7麥陣列

氣密性檢測(cè)儀定制:滿(mǎn)足個(gè)性化需求

定制化SoC陣列設(shè)計(jì)

定制化SoC陣列設(shè)計(jì)

評(píng)論