文章來源:半導體與物理

原文作者:jjfly686

本文主要講述芯片制造中鎢栓塞與銅互連。

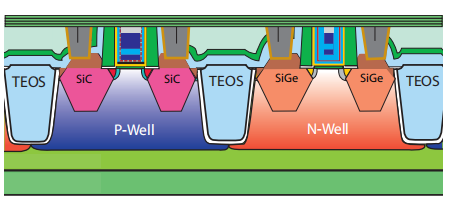

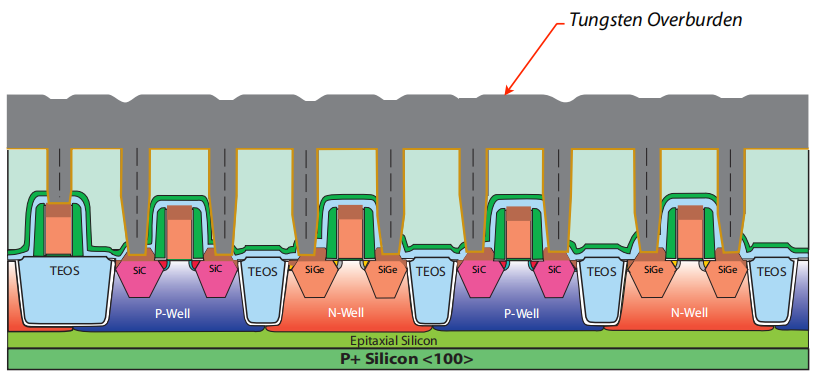

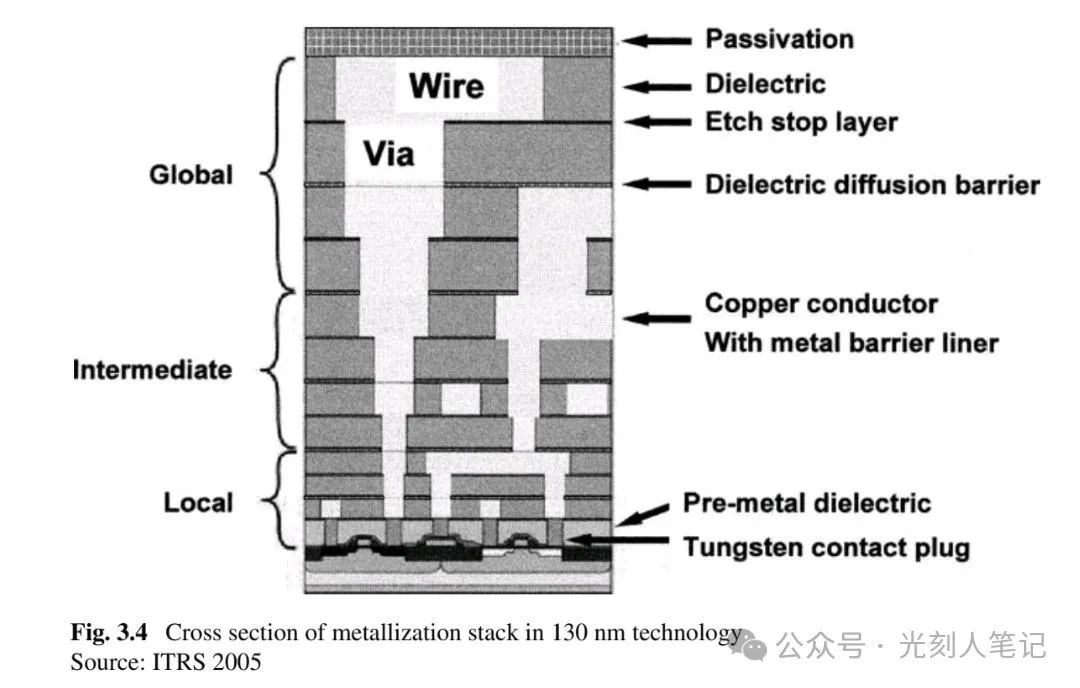

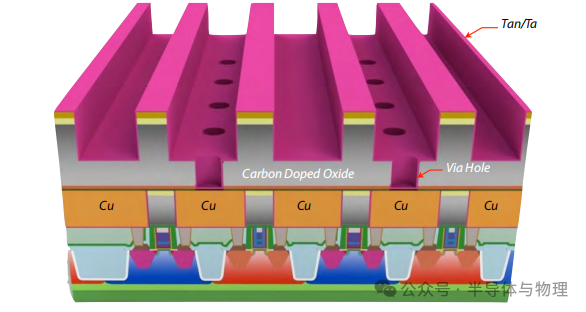

在指甲蓋大小的芯片上,數(shù)十億晶體管需要通過比頭發(fā)絲細千倍的金屬線連接。隨著制程進入納米級,一個看似微小的細節(jié)——連接晶體管與金屬線的"接觸孔",卻成為影響芯片性能的關(guān)鍵戰(zhàn)場。

納米接觸孔的電阻飆升

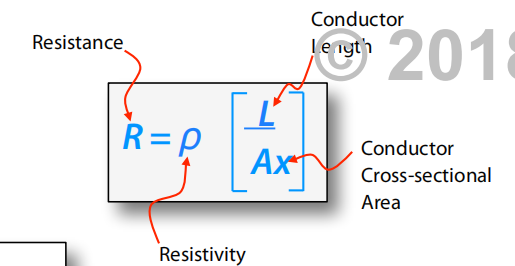

當芯片制程進入20 nm節(jié)點時,接觸孔直徑縮小到20 nm時,金屬接觸電阻會突然暴增3倍。這是因為接觸電阻與導體截面積成反比,當直徑從100 nm縮小到20 nm,截面積減少了25倍!

傳統(tǒng)鎢栓塞的困境:金屬鎢的電阻率比銅高,在納米級接觸孔中更顯劣勢;接觸孔深度若保持500 nm,其電阻相當于在納米尺度上"拖著一根細長的金屬絲";在28 nm芯片中,接觸電阻已占總互連電阻的40%,嚴重影響芯片速度與功耗。

鎢栓塞的絕地反擊:從"柱子"到"溝槽"

為了解決這一難題,工程師開發(fā)出兩項關(guān)鍵技術(shù):

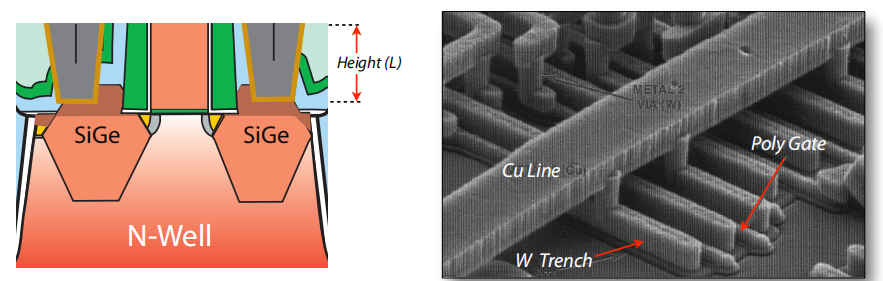

栓塞拋光(Plug Polish Back)在32 nm節(jié)點首次實現(xiàn)將鎢栓塞拋光至與柵極平齊,將接觸孔深度從500 nm壓縮到100 nm。由于電阻與長度成正比,深度縮短使接觸電阻降低80%。

鎢溝槽(Tungsten Trenches)將垂直的栓塞改為橫向溝槽,接觸面積擴大5-10倍。

抬升源漏

與鎢栓塞技術(shù)同步發(fā)展的,是抬升源漏(Raised Source/Drain)技術(shù):通過外延生長在晶體管源漏區(qū)形成凸起的硅鍺(SiGe)或硅碳(SiC)層;將接觸孔深度從硅襯底內(nèi)部轉(zhuǎn)移到抬升層,避免損傷敏感的有源區(qū);

-

半導體

+關(guān)注

關(guān)注

335文章

28778瀏覽量

235215 -

晶體管

+關(guān)注

關(guān)注

77文章

10004瀏覽量

141169 -

芯片制造

+關(guān)注

關(guān)注

10文章

681瀏覽量

29629

原文標題:芯片制造中的鎢栓塞與銅互連

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產(chǎn)工藝

集成電路片內(nèi)銅互連技術(shù)的發(fā)展

銅重量在PCB制造中的作用

微球強度測定 栓塞剛性測定資料

銅互連,還能撐多久?

提高銅互連優(yōu)勢的方法

PCB制造中銅厚度的重要性

具有銅互連的IC芯片設(shè)計

銅在半導體領(lǐng)域的應用

什么是銅互連?為什么銅互連非要用雙大馬士革工藝?

銅互連,尚能飯否?

芯片制造中的鎢栓塞與銅互連

芯片制造中的鎢栓塞與銅互連

評論