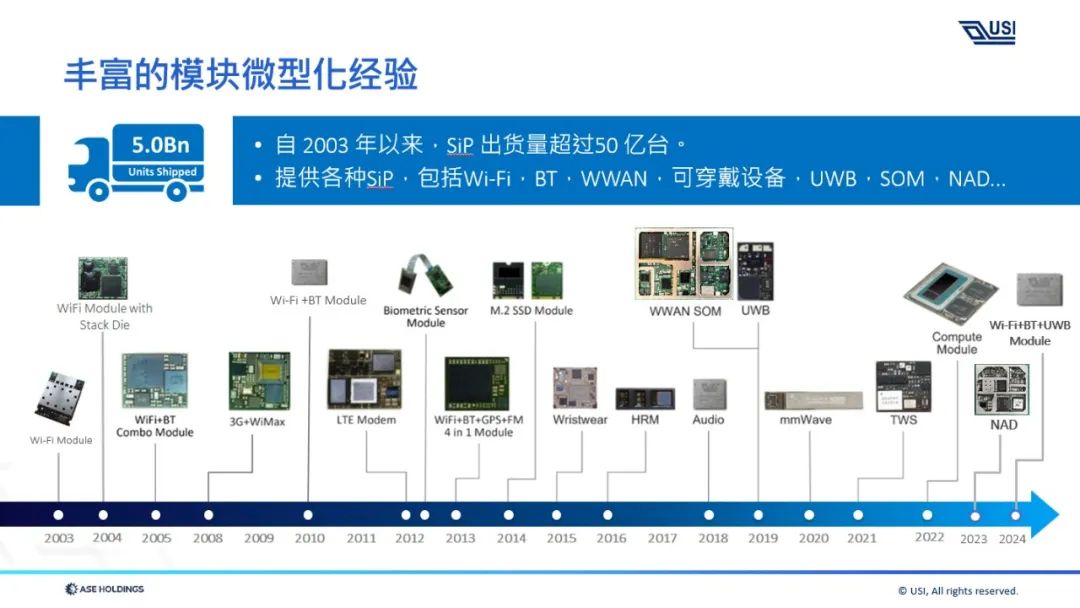

多年來,USI環旭電子始終致力于創新制程技術的研發,為穿戴式電子設備中的系統級封裝(SiP)實現高集成度及高性能的解決方案。其中,電磁屏蔽性能的持續優化與提升,可謂是 SiP 技術發展的關鍵所在。

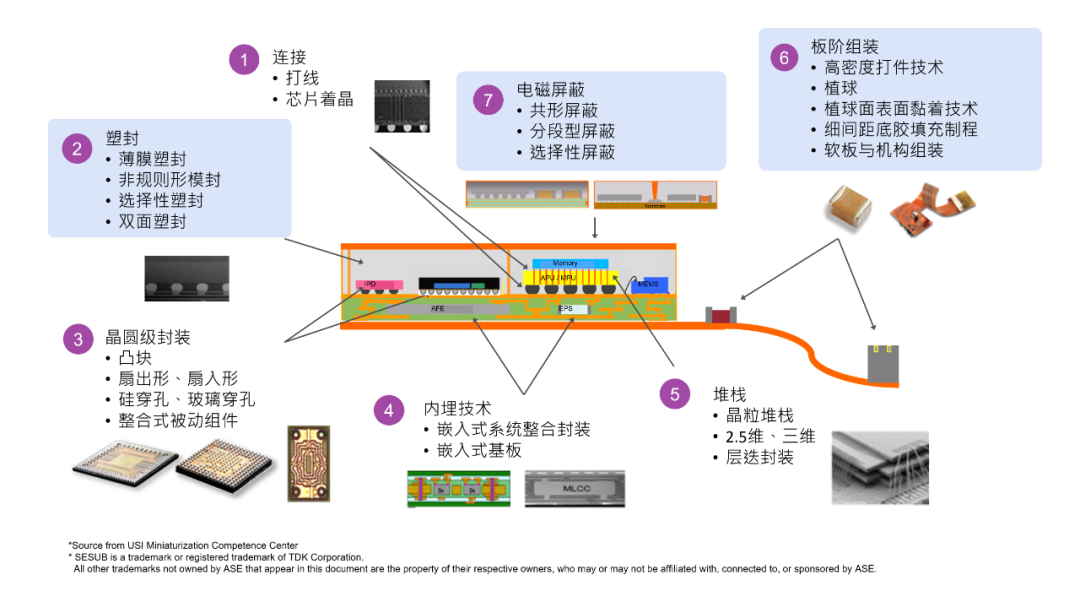

延伸前幾篇「系統級封裝」制程文章,本文中,我們將切入屏蔽技術 (Shielding) 兩大領域:共形屏蔽(Conformal Shielding)和分段型屏蔽(Compartment Shielding),并進一步探討其中制程之優劣,綜觀一覽微小化技術中的「屏蔽」制程。

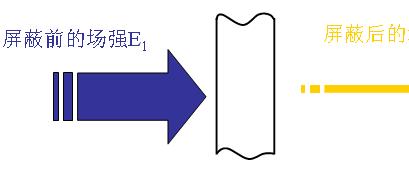

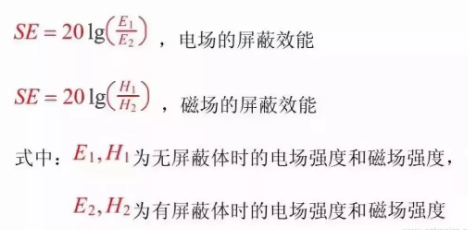

「電磁屏蔽技術」之必要性

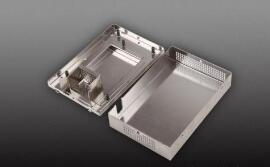

系統級封裝模組整合數百、千顆元件于一身,因此,勢必要避免模組內和外各項元件之間的相互干擾,這項屏障即為業界所稱的共形屏蔽(Conformal Shielding)和分段型屏蔽(Compartment Shielding)。過去在PCB組裝制程中,以金屬屏蔽柵欄作為隔間屏蔽已超過 20 年;在微小化模組產品中,雷射溝槽加導電膠填充技術則已使用超過 10 年。

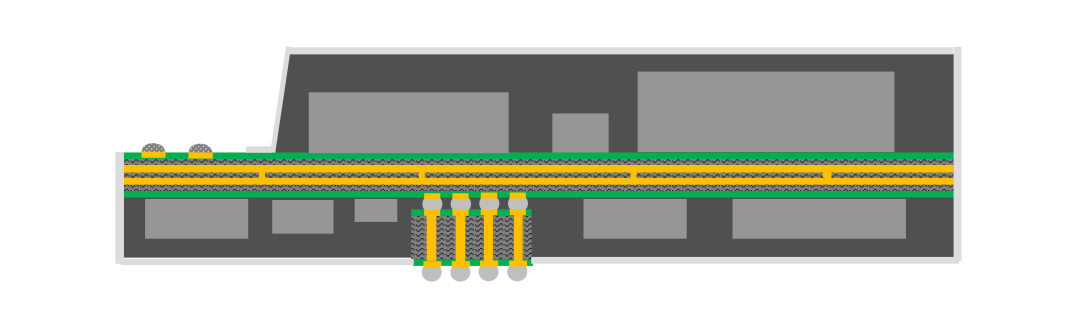

基于屏蔽效能與微小化的目的,金屬屏蔽柵欄已逐漸被淘汰。近年來,USI研發團隊成功開發出應用于間隔屏蔽的金屬屏蔽技術,節省大量成本的同時,也解決了長期以來存在的中頻與高頻問題,為SiP屏蔽技術提供新的解決方案。業界普遍常見的金屬屏蔽罩,每一段均需要保留約1mm寬度的焊盤與排除區域 (Keep-Out Zone),環旭電子的共形及分段型屏蔽僅需10%的寬度。以一個多頻4G模組為例,可為其他元件騰出超過17%的空間,并可屏蔽40-50 dB的電磁干擾。

共形屏蔽:滿足多樣化產品設計需求

環旭電子在共型屏蔽技術(Conformal Shielding)上持續創新與研發,可以實現選擇性屏蔽,雙面屏蔽等技術以滿足不同的產品設計需求,并且成功開發了噴涂(Spray Coating)制程,進一步降低了產品成本。

選擇性共型屏蔽是通過在濺射(sputtering)前用遮蔽帶(tape)覆蓋不需要屏蔽的區域,在濺射后去除遮蔽帶,實現了選擇性屏蔽,同時滿足共型屏蔽要求和實現裸露I/O焊點,還可實現雙面塑封產品I/O的要求。雙面共型屏蔽技術則通過兩次濺射實現雙面選擇性屏蔽,進一步提升了產品設計的靈活性,降低了設計難度。

噴涂則是在產品表面與側壁噴涂導電膠取代濺射,實現共型屏蔽。這一項制程的成功開發為共型屏蔽提供了更多實現方案,并顯著降低了機臺成本和產品成本。

雙面選擇性屏蔽

USI環旭電子在電磁屏蔽技術上的突破,不僅為SiP模組帶來了更高的集成度和性能,更為客戶創造了多方面的價值。 首先,透過精準的屏蔽設計,有效降低了元件間的相互干擾,提升了產品的穩定性與可靠性。其次,我們獨立開發的屏蔽技術大幅縮減了占用面積,為客戶在有限的空間內實現更多功能提供了可能。此外,選擇性屏蔽與雙面屏蔽等創新技術,滿足了客戶日益多元化的產品設計需求,更推升了我們在微小化模組中的生產競爭力。

在下一篇文章中,我們將深入探討「分段式屏蔽技術」,揭示其在SiP模組中的關鍵作用與優勢。 分段式屏蔽技術是如何實現更精細化的電磁控制?它又為SiP模組帶來了哪些新的應用場景?敬請期待!

-

系統級封裝

+關注

關注

0文章

39瀏覽量

9228 -

電磁屏蔽

+關注

關注

11文章

139瀏覽量

26869 -

環旭電子

+關注

關注

0文章

57瀏覽量

3743

原文標題:系統級封裝(SiP)電磁屏蔽技術:共形屏蔽&分段型屏蔽

文章出處:【微信號:環旭電子 USI,微信公眾號:環旭電子 USI】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電磁屏蔽房介紹

電磁屏蔽技術的方法有哪些_電磁屏蔽技術的方法盤點

系統級封裝電磁屏蔽技術介紹

系統級封裝電磁屏蔽技術介紹

評論