前 言

本文主要介紹TLT536-EVM評估板硬件接口資源以及設計注意事項等內容。

T536MX-CXX/T536MX-CEN2處理器的IO電平標準一般為1.8V、3.3V,上拉電源一般不超過3.3V或1.8V,當外接信號電平與IO電平不匹配時,中間需增加電平轉換芯片或信號隔離芯片。按鍵或接口需考慮ESD設計,ESD器件選型時需注意結電容是否偏大,否則可能會影響到信號通信。

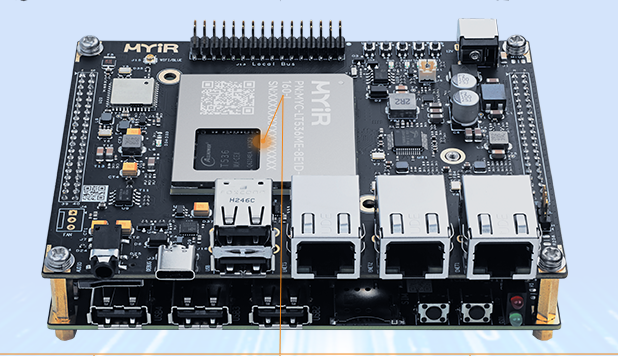

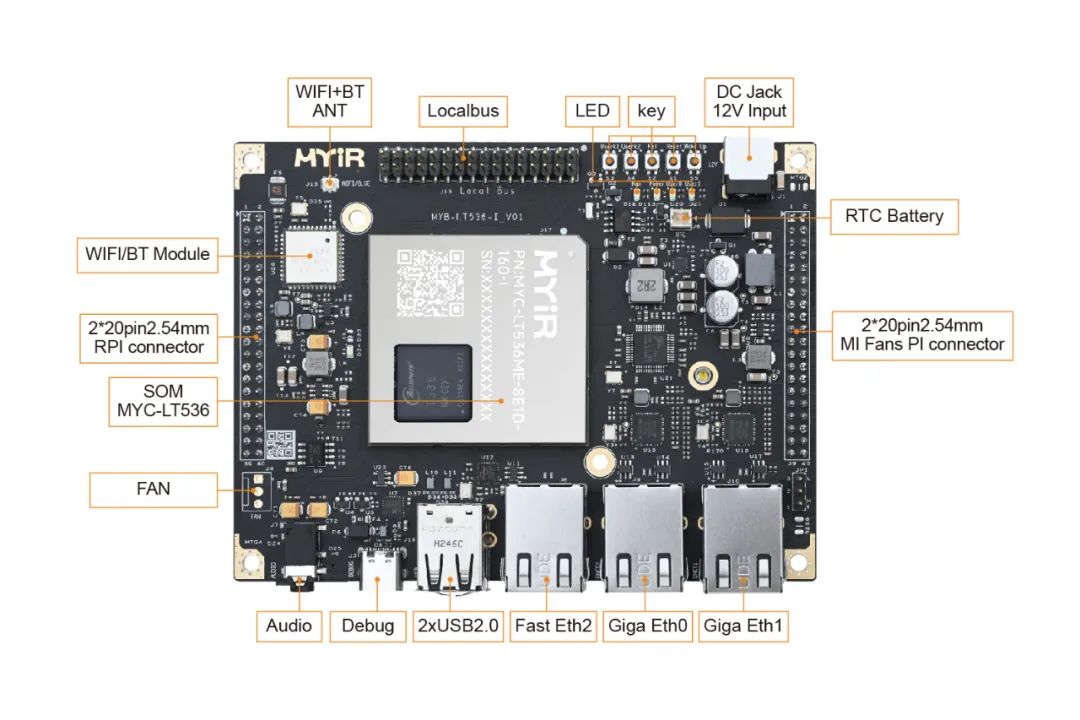

圖 1 評估板硬件資源圖解1

圖 2 評估板硬件資源圖解2

圖 3 評估板硬件資源圖解3

為便于閱讀,如下對文檔出現的部分術語進行解釋;對于廣泛認同釋義的術語,本頁不做注釋。

硬件參考資料目錄如下表所示:

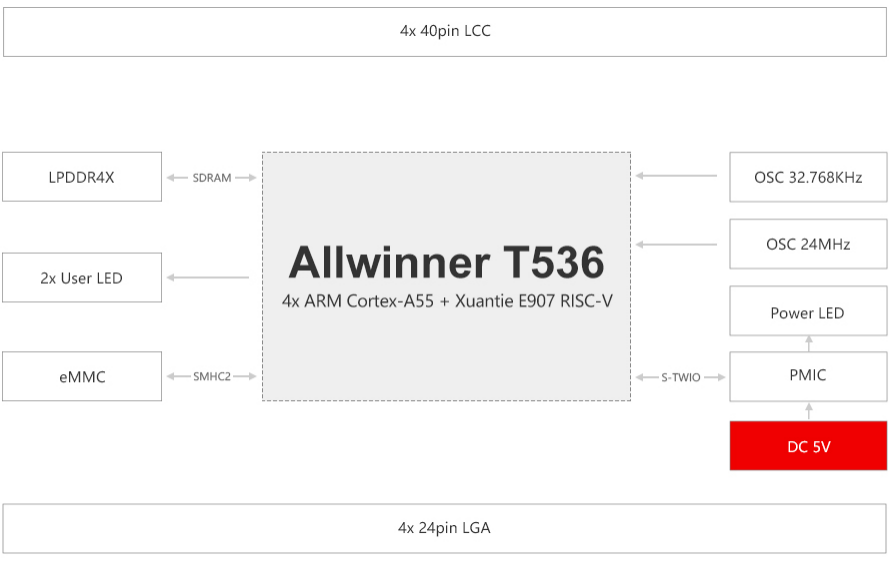

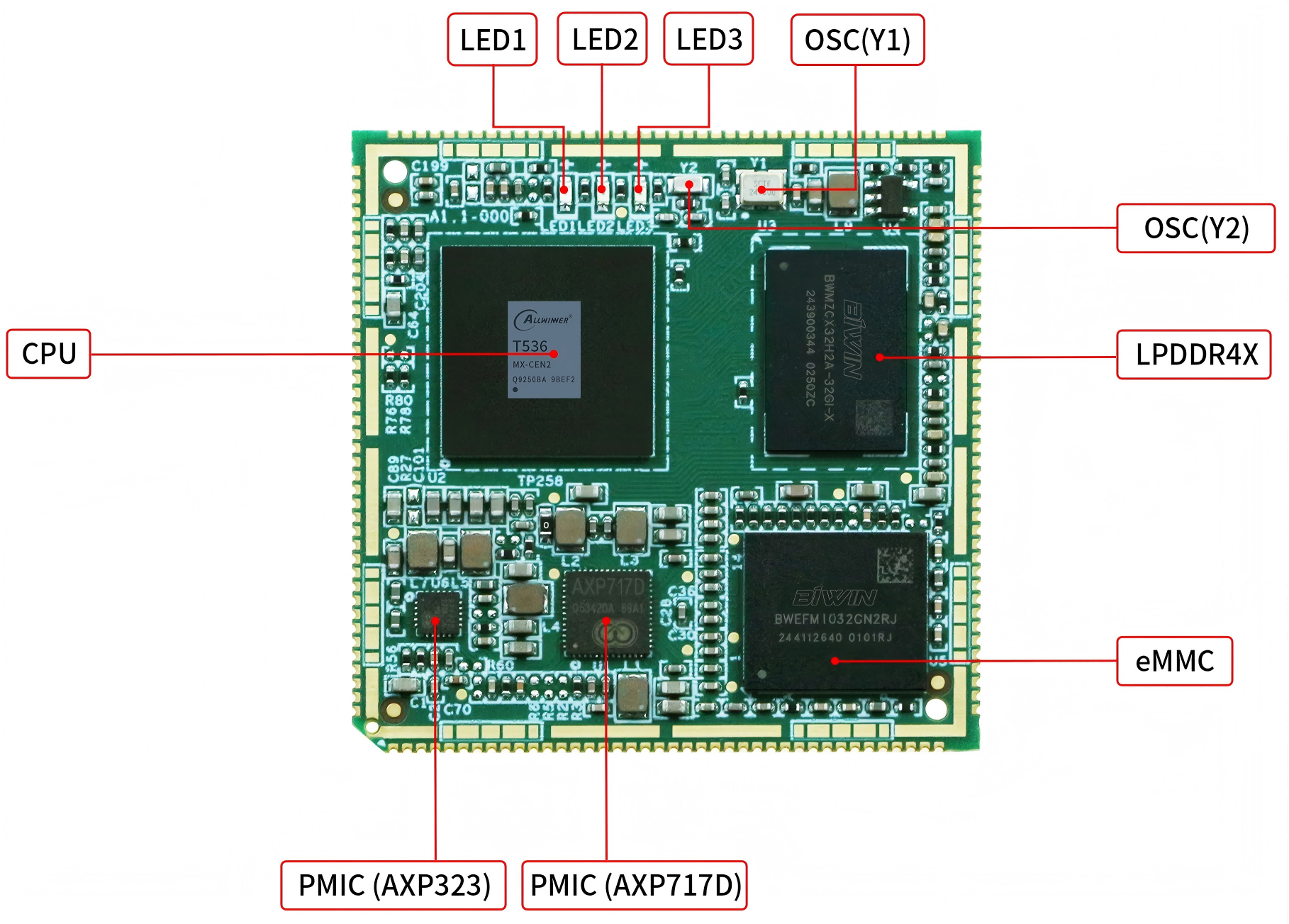

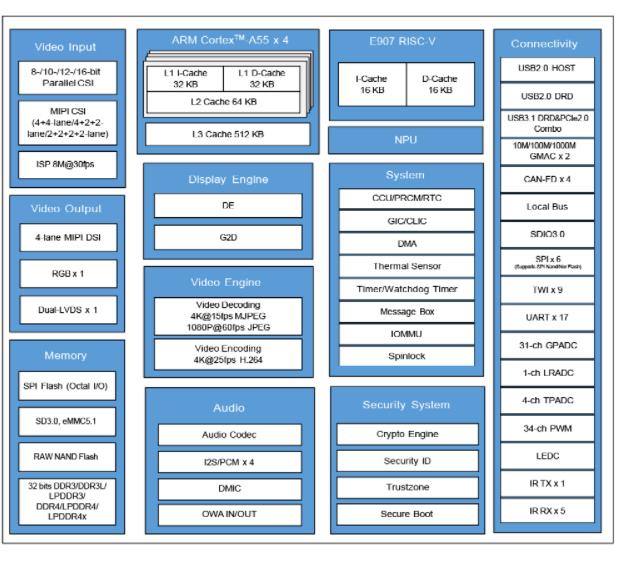

SOM-TLT536核心板

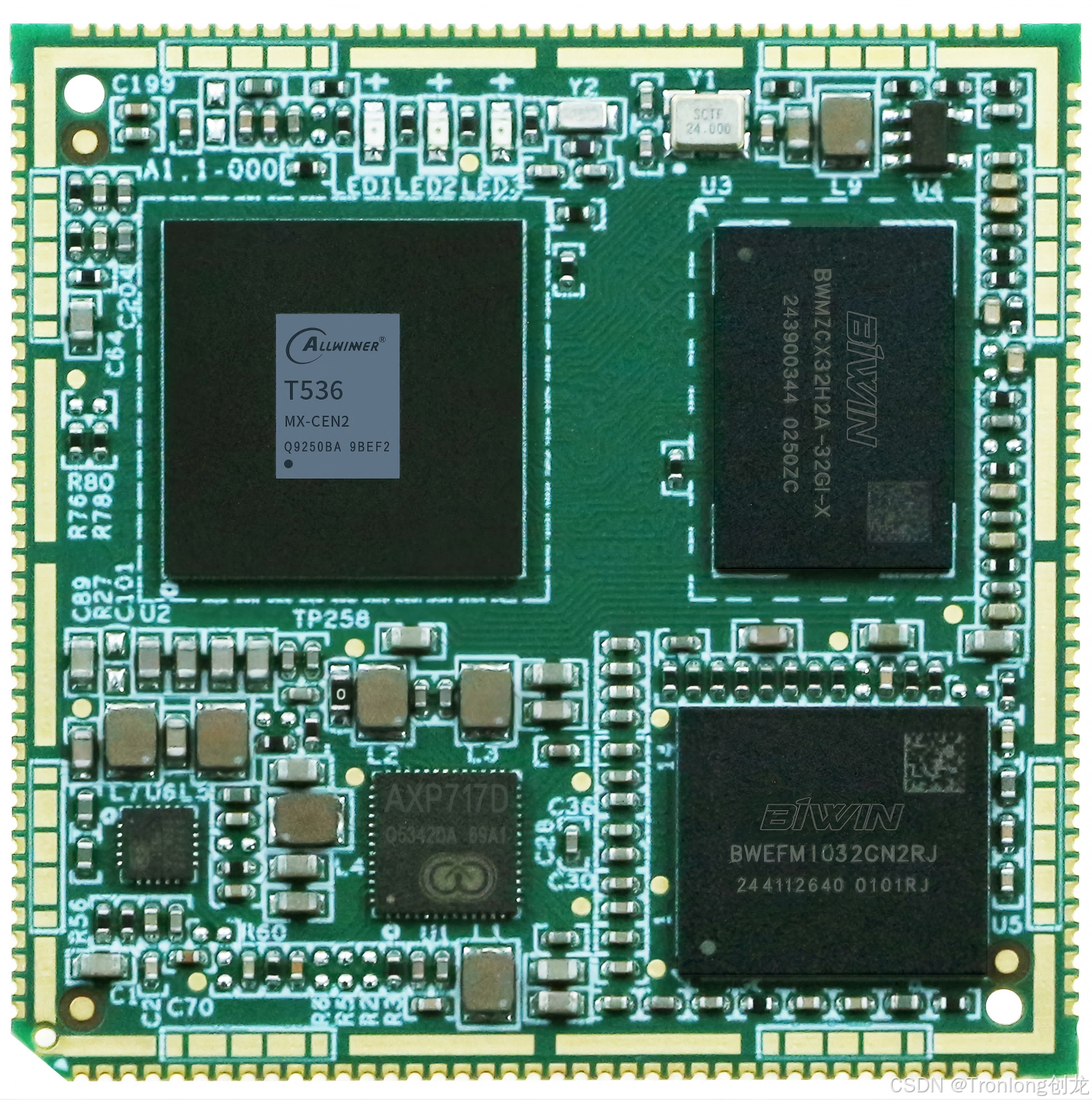

SOM-TLT536核心板板載CPU、ROM、RAM、晶振、電源、LED等硬件資源,并通過工業級B2B連接器方式引出IO。核心板硬件資源、引腳說明、電氣特性、機械尺寸、底板設計注意事項等詳細內容,請查閱《SOM-TLT536工業核心板硬件說明書》。

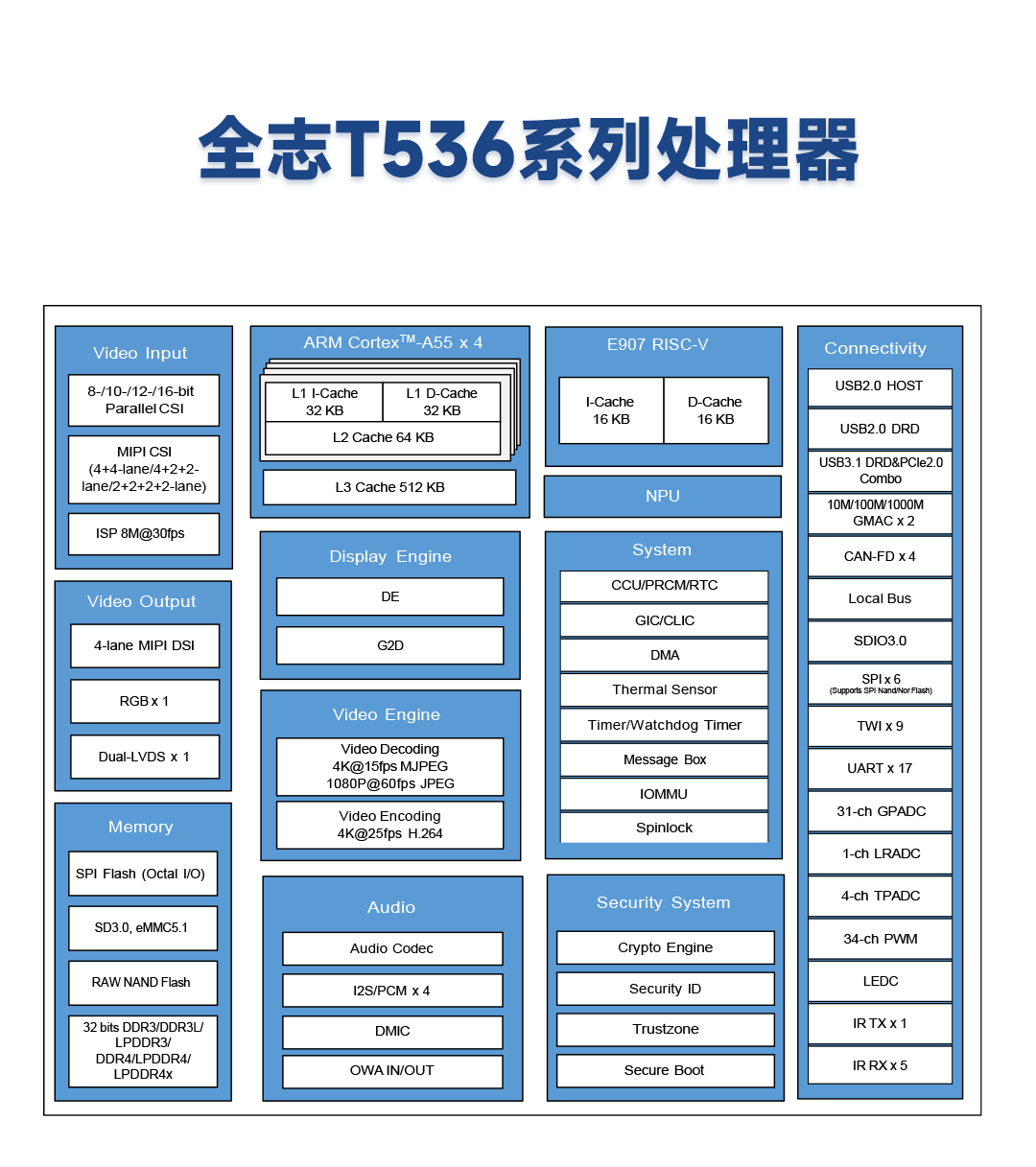

圖 4 核心板硬件框圖

圖 5 核心板正面實物圖

圖 6 核心板背面實物圖

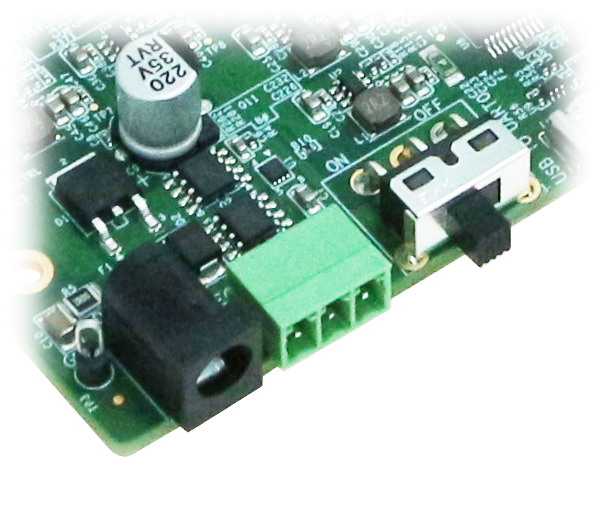

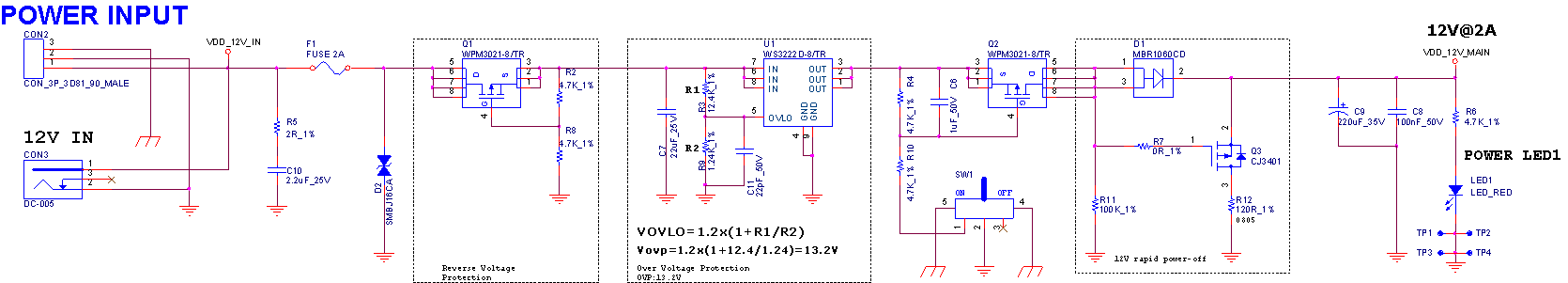

電源

評估板由12V直流電源供電,CON2和CON3為電源輸入連接器。CON2為3pin規格的綠色連接器,間距為3.81mm。CON3為DC-005電源接口,可接外徑5.5mm、內徑2.1mm的電源插頭。SW1為電源撥動開關,使用時請根據附近的ON/OFF絲印進行選擇。

圖 7 電源接口實物圖

電源輸入端提供過流保護、過壓保護、防反插及快速掉電等電路保護功能。

圖 8 輸入級電源保護電路

VDD_12V_MAIN通過不同電源芯片轉為核心板及評估底板外設的供電。核心板提供底板輔助電源信號VDD_3V3_SOM_OUT,用于控制評估底板各路電源上電時序。

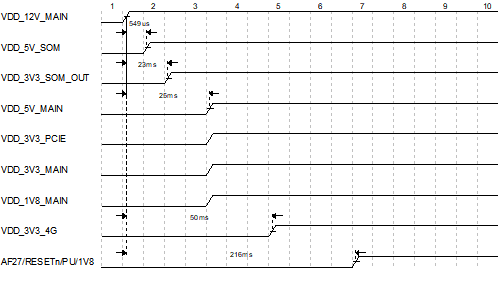

評估板推薦的上電時序:12V DC供電(VDD_12V_MAIN) -> 核心板供電(VDD_5V_SOM) -> 核心板配置底板輔助電源(VDD_3V3_SOM_OUT) -> 底板外設供電 -> 系統復位(AF27/RESETn/PU/1V8),如下圖所示。

圖 9 評估底板推薦上電時序

核心板電源

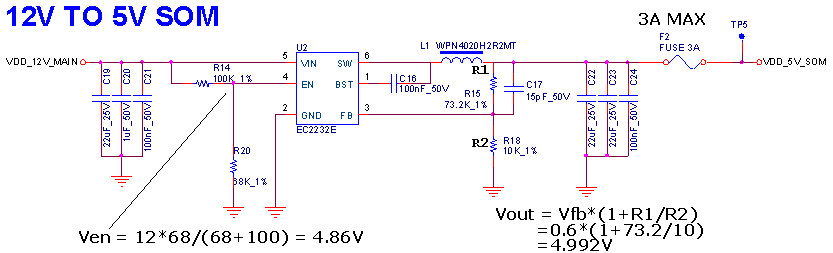

VDD_12V_MAIN通過芯強微電子(Ecranic)的EC2232E DCDC電源芯片產生一路5V電源,用于SOM-TLT536核心板的供電,該電源網絡名為VDD_5V_SOM,最大電流供給能力為3A。

該電源使能由輸入電壓VDD_12V_MAIN分壓提供,實現上電即使能的時序控制。為保護核心板及方便測量電壓電流,電源路徑中已串接保險絲F2。

圖 10VDD_5V_SOM電源設計

為保證核心板長期穩定可靠工作,請按我司提供的工作電壓典型值(5.0V)要求為核心板供電。

評估底板外設電源

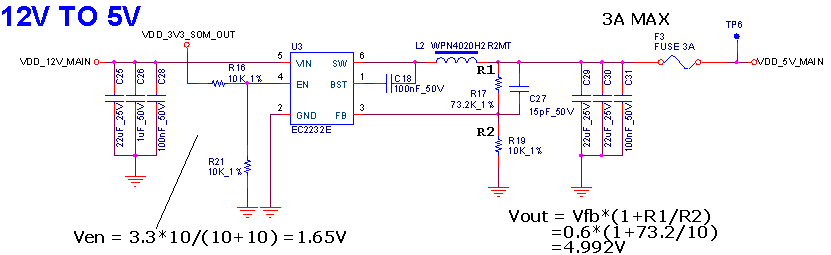

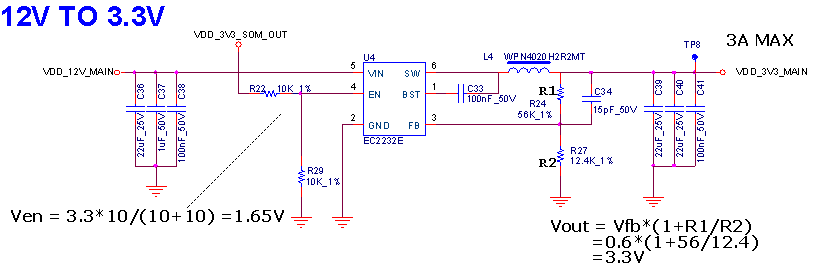

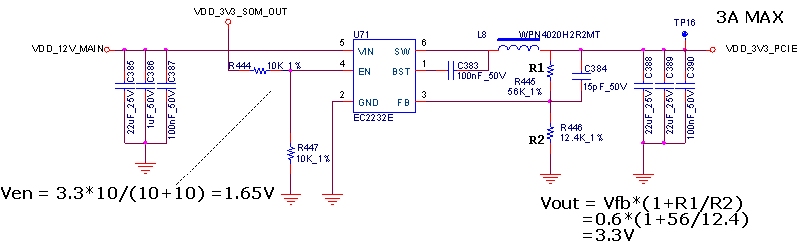

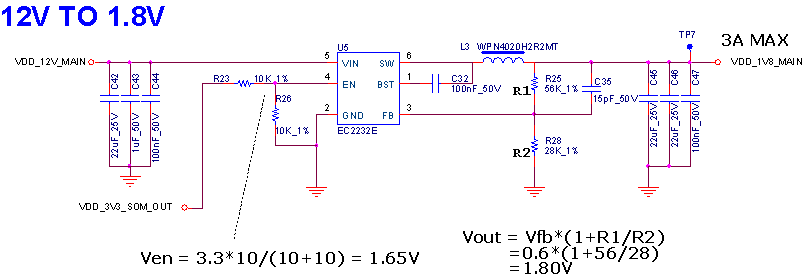

VDD_12V_MAIN通過4個芯強微電子(Ecranic)的EC2232E DCDC電源芯片產生4路評估底板外設電源,網絡名分別為:VDD_5V_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIE、VDD_1V8_MAIN,最大電流供給能力為3A。

4路電源使能統一由核心板VDD_3V3_SOM_OUT信號提供,實現核心板電源上電早于外設電源上電的時序控制。

圖 11 VDD_5V_MAIN電源設計

圖 12 VDD_3V3_MAIN電源設計

圖 13 VDD_3V3_PCIE電源設計

圖 14 VDD_1V8_MAIN電源設計

設計注意事項:

(1) 核心板提供的VDD_3V3_SOM_OUT電源輸出,供電能力≤500mA,主要用于控制評估底板各路電源的上電時序,以及核心板配置相關電路的供電(如BOOT SET、Micro SD、看門狗等電路),請勿用于其他外設的供電。

隔離電源

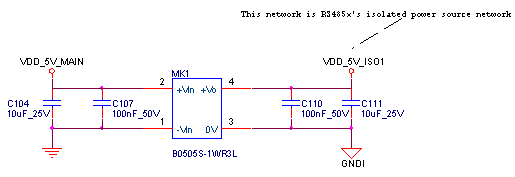

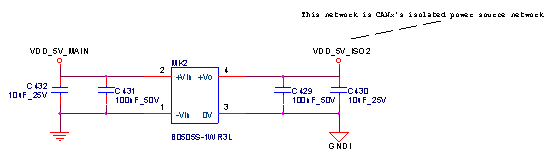

VDD_5V_MAIN通過金升陽科技(MORNSUN)的B0505S-1WR3L隔離電源模塊產生一路5V DC隔離電源,用于評估底板隔離電路的供電,網絡名為VDD_5V_ISO1和VDD_5V_ISO2,最大電流供給能力為200mA,可提供3000V DC的直流隔離能力。

圖 15 VDD_5V_ISO1電源設計

圖 16 VDD_5V_ISO2電源設計

設計注意事項:

(1) 底板設計時,若無需輸入級保護電路的部分或全部功能,可適當裁剪。

(2) 底板電源設計可根據實際電路設計進行增減,建議參考我司上電時序進行底板電源的使能控制。

(3) 核心板供電請參考我司評估底板電源電路設計,注意核心板供電為5.0V。

(4) VDD_5V_SOM在核心板內部未預留總電源輸入的儲能大電容。底板設計時,請在靠近郵票孔焊盤位置放置總容值為50uF左右的儲能電容。

(5) 為使VDD_5V_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIE和VDD_1V8_MAIN滿足系統上電、掉電時序要求,需使用核心板輸出VDD_3V3_SOM_OUT來控制VDD_5V_MAIN、VDD_3V3_MAIN、VDD_3V3_PCIE和VDD_1V8_MAIN的電源使能,使評估底板VDD_5V_MAIN、VDD_3V3_MAIN、VDD_3V3_PEIE和VDD_1V8_MAIN電源在VDD_3V3_SOM_OUT之后、在AF27/RESETn/PU/1V8復位信號之前上電(詳情見評估底板推薦上電時序)。

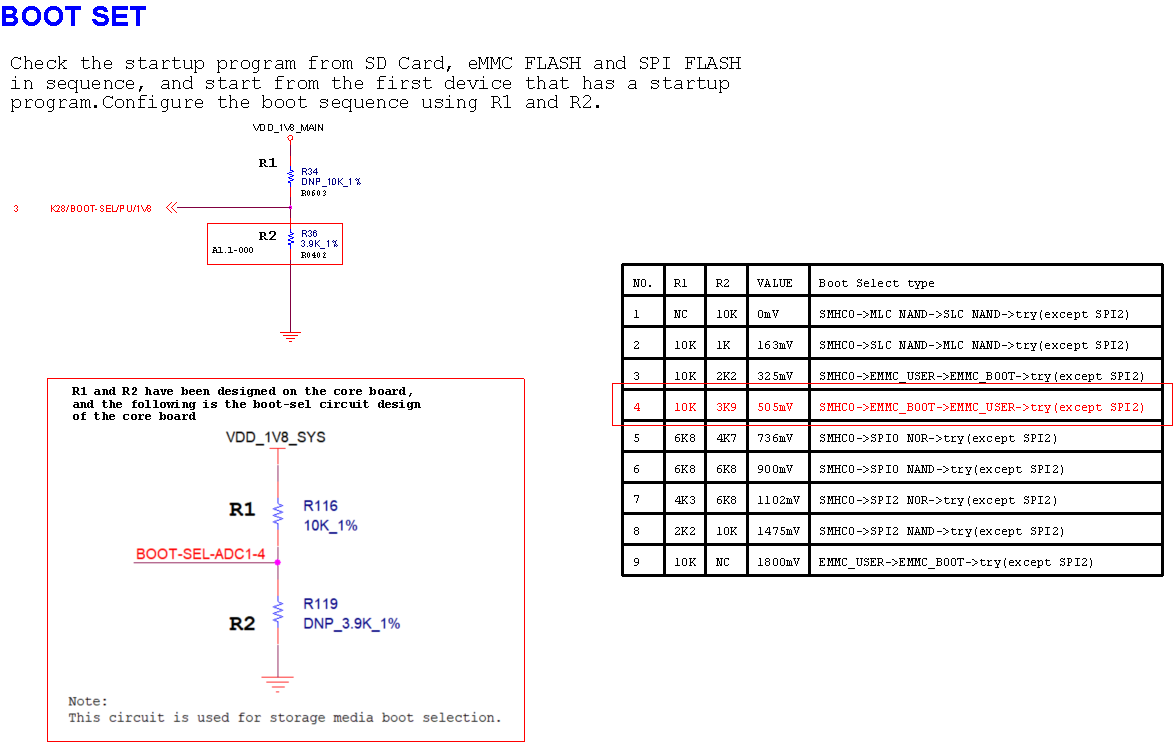

系統啟動說明

系統上電后,由CPU內部BootRom的引導代碼依次從SD卡、eMMC FLASH檢測SPL啟動程序,從第一個包含SPL啟動程序的設備開始啟動。SPL啟動后,將優先從SD系統卡(非常規SD卡)引導U-Boot鏡像,否則,將從原啟動設備引導U-Boot鏡像。

圖 17 評估底板BOOT SET設計

設計注意事項:

(1) K28/BOOT-SEL/PU/1V8為啟動配置引腳,在核心板板已接10K電阻上拉至1.8V電源,在評估底板已接3.9K電阻下拉到地,啟動方式默認順序為SD卡、eMMC FLASH。

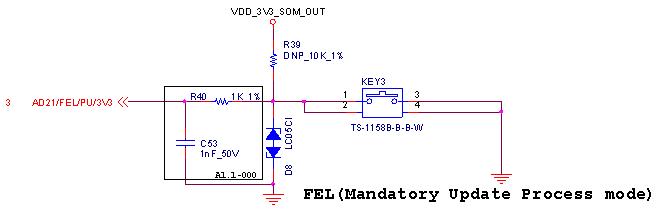

(2) 當KEY3按鍵按下,并將評估板重新上電,此時AD21/FEL/PU/3V3引腳輸入為低電平,CPU將進入Mandatory Update Process模式,可通過USB2.0 DRD接口進行固件升級。

LED

評估底板提供電源指示燈,用戶可編程指示燈及模塊狀態指示燈,分別為LED1~LED4,采用插件封裝。

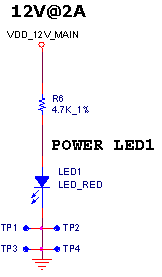

電源指示燈

LED1為電源指示燈,顏色為紅色,上電默認點亮。

圖 18 電源指示燈實物圖

圖 19 評估板電源指示燈電路設計

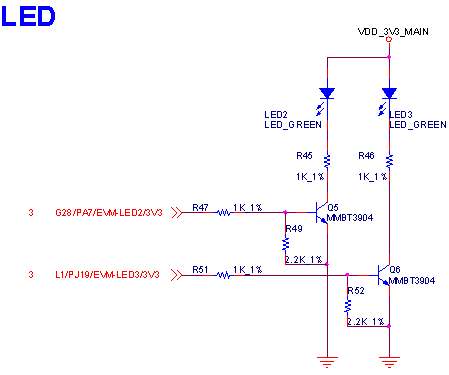

用戶可編程指示燈

評估底板提供2個用戶可編程指示燈LED2和LED3,高電平點亮,顏色為綠色,通過CPU的PA7、PJ19引腳控制。

圖 20 用戶可編程指示燈實物圖

圖 21 用戶可編程指示燈電路設計

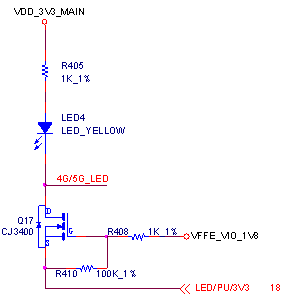

模塊狀態指示燈

圖 22 4G/5G模塊狀態指示燈實物圖

圖 23 4G/5G模塊狀態指示燈電路設計

KEY

評估底板包含1個系統復位按鍵RESETn(KEY1),1個PMIC開關機按鍵PWRON(KEY2),1個FEL按鍵FEL(KEY3)、2個用戶輸入按鍵USER1(KEY4)、USER2(KEY5)。

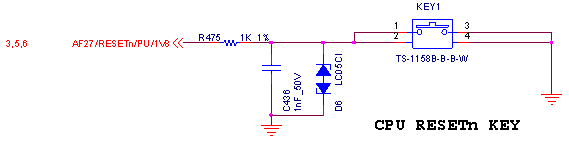

RESETn復位按鍵

KEY1為評估板RESETn復位按鍵,控制CPU和PMIC的復位引腳。

圖 24 RESETn按鍵實物圖

圖 25RESETn按鍵電路設計

設計注意事項:

(1) AF27/RESETn/PU/1V8為核心板的復位輸入引腳,核心板內部已上拉10K電阻,默認情況請懸空處理,以避免影響上電時序。

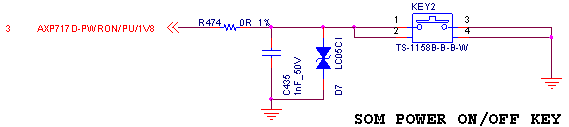

PWRON按鍵

KEY2為PMIC開關機按鍵,按鍵狀態通過PWRON引腳輸入至PMIC。

圖 26 PWRON按鍵實物圖

圖 27 PWRON按鍵電路設計

設計注意事項:

(1) PWRON為PMIC的開關機控制引腳,在PMIC內部已上拉,默認情況請懸空處理。

FEL按鍵

KEY3為FEL按鍵,系統重新上電時,若檢測到AD21/FEL/PU/3V3信號為低電平,CPU將進入Mandatory Update Process模式,可通過USB2.0 DRD接口進行固件升級。

圖 28 FEL按鍵實物圖

圖 29FEL按鍵電路設計

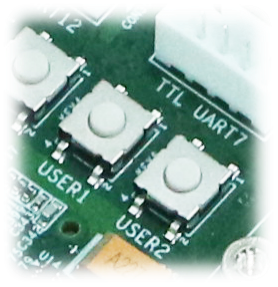

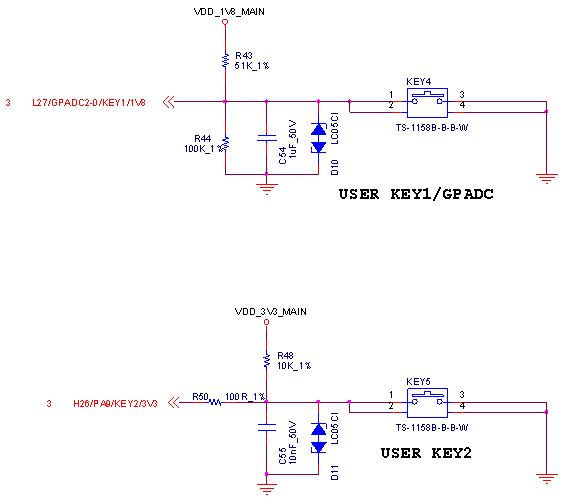

用戶輸入按鍵

KEY4(USER1),KEY5(USER2)為用戶輸入按鍵,KEY4按鍵狀態通過GPADC2_0引腳輸入至CPU,KEY5按鍵狀態通過PA9引腳輸入至CPU。

圖 30 用戶輸入按鍵實物圖

圖 31 用戶輸入按鍵電路設計

設計注意事項:

(1) L27/GPADC2-0/KEY1/1V8的電壓輸入范圍為0~1.8V,評估底板可通過分壓電阻將輸入電壓控制在0~1.8V之間。由于L27/GPADC2-0/KEY1/1V8信號在核心板內部未預留上拉電阻,因此默認情況下請為該信號提供10K上拉電阻。

串口

評估底板板載13路串口,CON5為USBTO UART0調試串口,CON9為RS232 S-UART1串口,CON10為RS232 UART6串口,J20含有RS485 UART1、RS485 UART2、RS485 UART3、RS485 UART4、RS485 UART9和RS485 UART11串口。CON29為TTL S-UART0串口并與WiFi/BT模塊復用,CON28為TTL UART5串口,CON30為TTL UART12串口并與EXPORT1復用,CON31為TTL UART7串口并與EXPORT1復用。

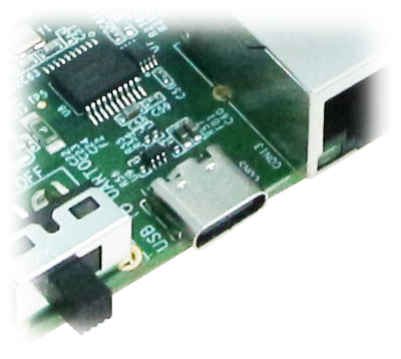

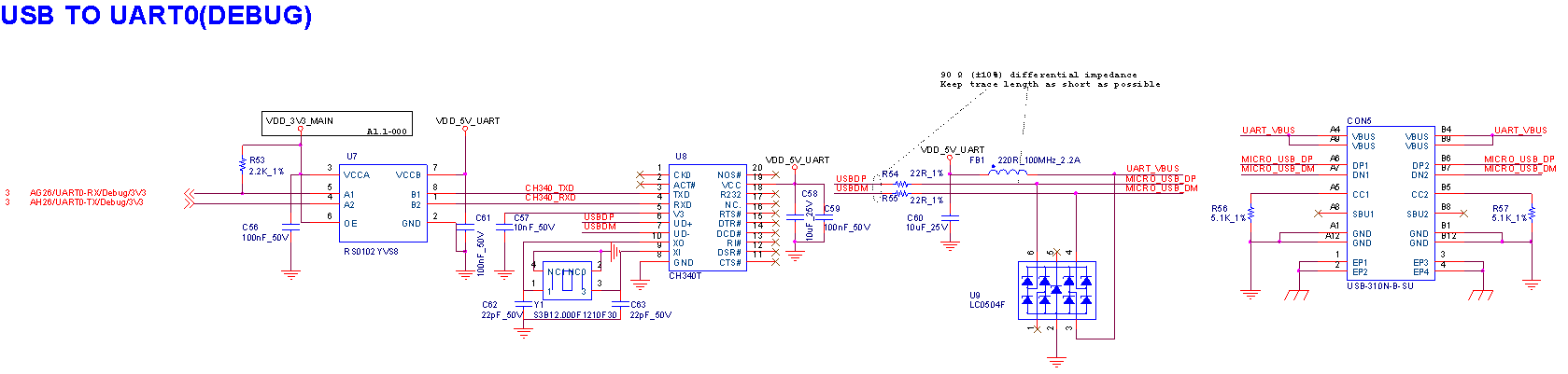

USB TO UART0串口

評估底板通過沁恒微電子(WCH)的CH340T芯片將UART0轉換為Type-C連接器(CON5)引出,作為系統調試串口使用。CH340T使用來自Type-C數據線的5V(網絡名為UART_VBUS)外部供電。

圖 32 USBTO UART0實物圖

圖 33 USBTO UART0電路設計

設計注意事項:

(1) 底板設計時,建議采用RS0102YVS8(U7)電平轉換隔離方案,以避免調試串口RX端在底板上電前提前帶電,向核心板引腳灌輸電流,導致系統無法啟動。

(2) CPU引腳UART0-TX、UART0-RX電平皆為3.3V,請勿使用5V電平接口的調試工具直接連接,否則將導致CPU損壞。

(3) 注意USB信號需做90ohm差分阻抗匹配。

(4) ESD器件需靠近連接器Type-C接口布局,走線經過ESD后連接至CH340T。

(5) 底板設計時,建議在AG26/UART0-RX/Debug/3V3網絡添加2.2K電阻上拉至VDD_3V3_MAIN,以避免調試串口RX端在底板上電時電平不穩定,誤入U-Boot模式。

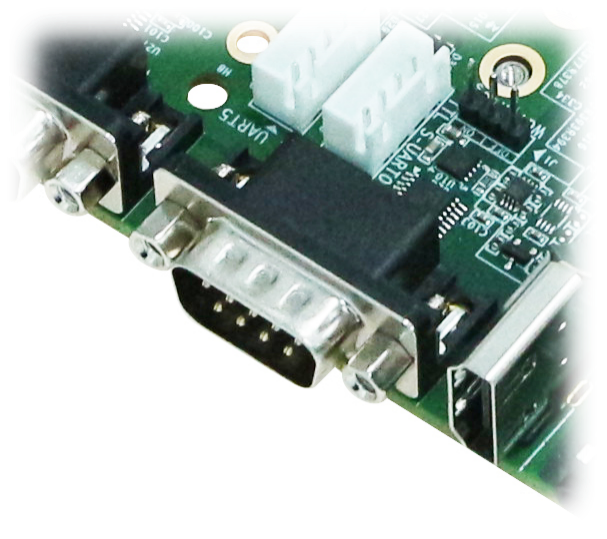

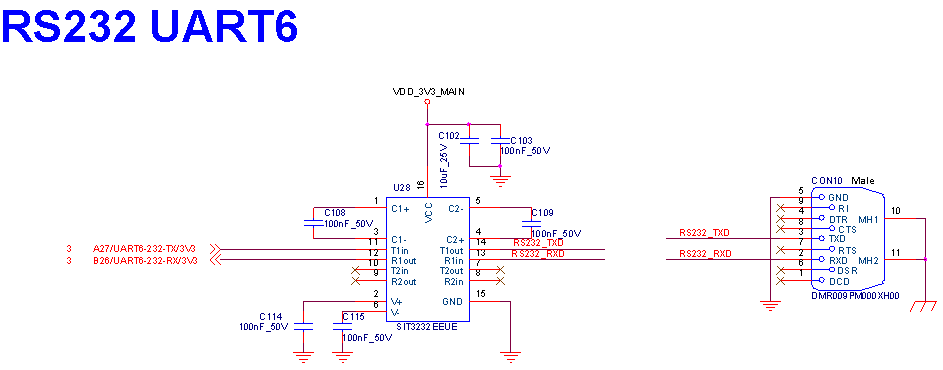

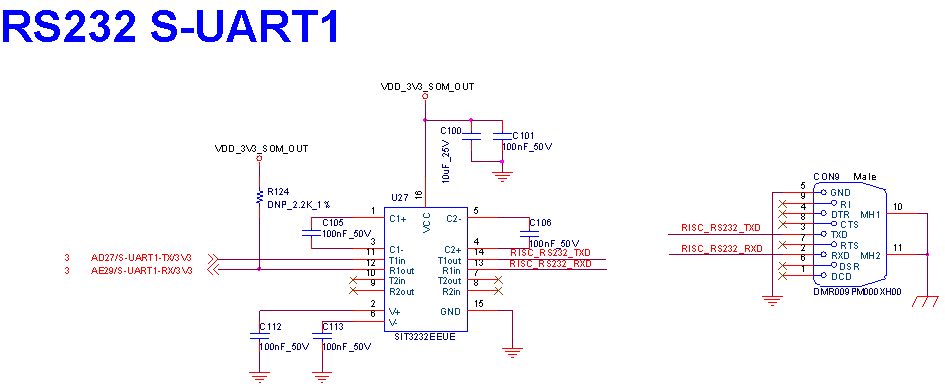

RS232 UART6/S-UART1串口

評估底板采用芯力特電子(SIT)的單電源雙通道RS232收發器SIT3232EEUE方案,通過UART6和S-UART1各引出一路RS232串口,使用DB9連接器(CON9和CON10)。

SIT3232EEUE符合TIA/EIA-232標準,速率可高達到120Kbps。

圖 34 RS232 UART6實物圖

圖 35 RS232 UART6串口電路設計

圖 36 RS232 S-UART1實物圖

圖 37 RS232 S-UART1串口電路設計

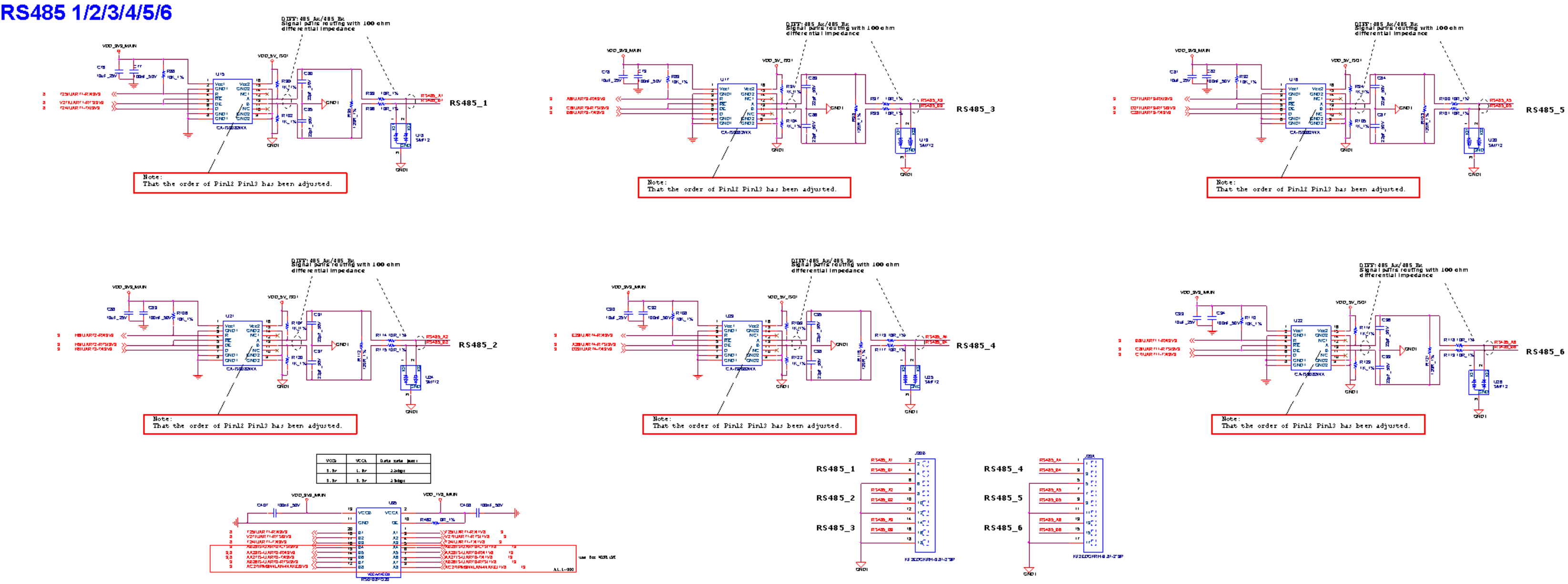

RS485 UART1/UART2/UART3/UART4/UART9/UART11串口

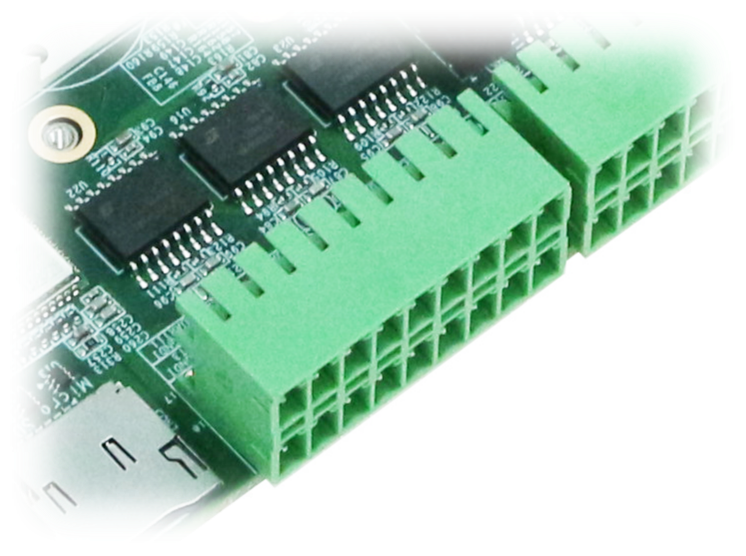

評估底板采用川土微電子(CHIPANALOG)的隔離式半雙工RS485收發器CA-IS3082WX方案,通過UART1、UART2、UART3、UART4、UART9和UART11引出六路RS485串口。六路RS485串口使用2x 9pin規格綠色連接器(J20),間距為3.81mm。

CA-IS3082WX符合TIA/EIA-485-A標準,支持5kVrms絕緣耐受電壓,總線共模工作范圍:-7V~+12V,并提供高達0.5Mbps的通信速率。

圖 38 RS485串口實物圖

圖 39 RS485串口電路設計

設計注意事項:

(1) CA-IS3082WX是隔離RS485收發器;其中Vcc1(pin1)和GND1(pin2/7/8)為邏輯側端口的供電,Vcc2(pin16)和GND2(pin9/10/15)是總線側端口的供電。Vcc1對Vcc2應電氣隔離,GND1和GND2不共地,且器件布局及走線上注意做隔離設計,否則無法達到隔離接口的設計目的。建議參考我司評估底板原理圖設計,使用隔離電源給Vcc2供電。

(2) Vcc1提供2.375V~5.5V的寬IO供電范圍,總線側電源Vcc2提供3.0V~5.5V的RS485總線供電范圍。

(3) RS485收發器的管腳A/B(pin12/13)連接至綠色端子連接器之間的走線,需按差分信號進行走線。

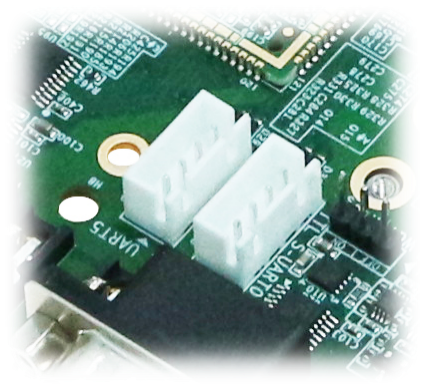

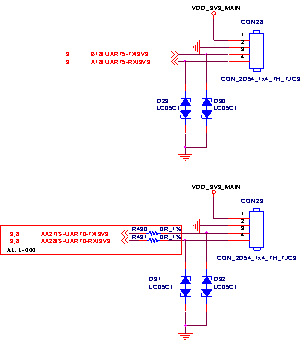

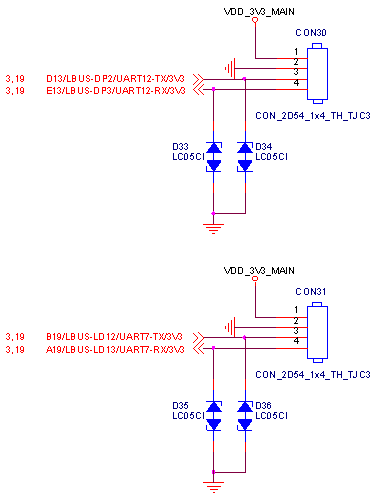

TTL UART5/S-UART0/UART7/UART12串口

UART5、S-UART0、UART7和UART12分別通過4pin規格、2.54mm間距白色排針端子,直接引出TTL電平測試引腳。

備注:

(1) TTL S-UART0與WiFi/BT模塊(U56)存在復用,兩個功能不可同時使用,如需使用WiFi藍牙功能時,CON29的第3和第4針腳不能用跳線帽連接或引出連接到其他串口設備。

(2) TTL UART7和TTL UART12與EXPORT1接口的Local Bus總線存在復用,如需使用Local Bus總線功能時,CON30和CON31的第3和第4針腳不能用跳線帽連接或引出連接到其他串口設備。

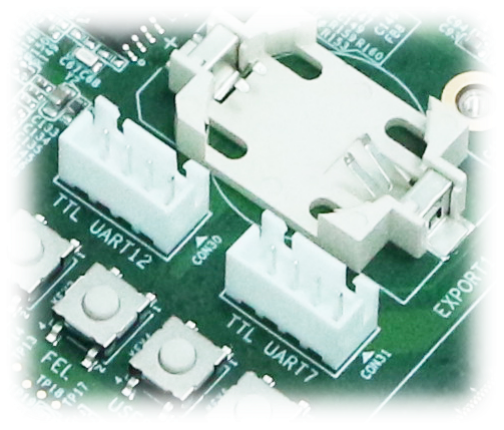

圖 40 TTL UART5/S-UART0實物圖

圖 41 TTL UART5/S-UART0串口電路設計

圖 42 TTL UART7/UART12實物圖

圖 43 TTL UART7/UART12串口電路設計

由于篇幅過長等原因,部分引腳內容及板卡硬件內容均不逐一展示,如需獲取完整版詳細資料,請關注創龍科技,或者評論區留言,感謝您的支持!

審核編輯 黃宇

-

ARM

+關注

關注

134文章

9352瀏覽量

377543 -

uart

+關注

關注

22文章

1276瀏覽量

103950 -

開發板

+關注

關注

25文章

5682瀏覽量

104746 -

RISC

+關注

關注

6文章

482瀏覽量

84992

發布評論請先 登錄

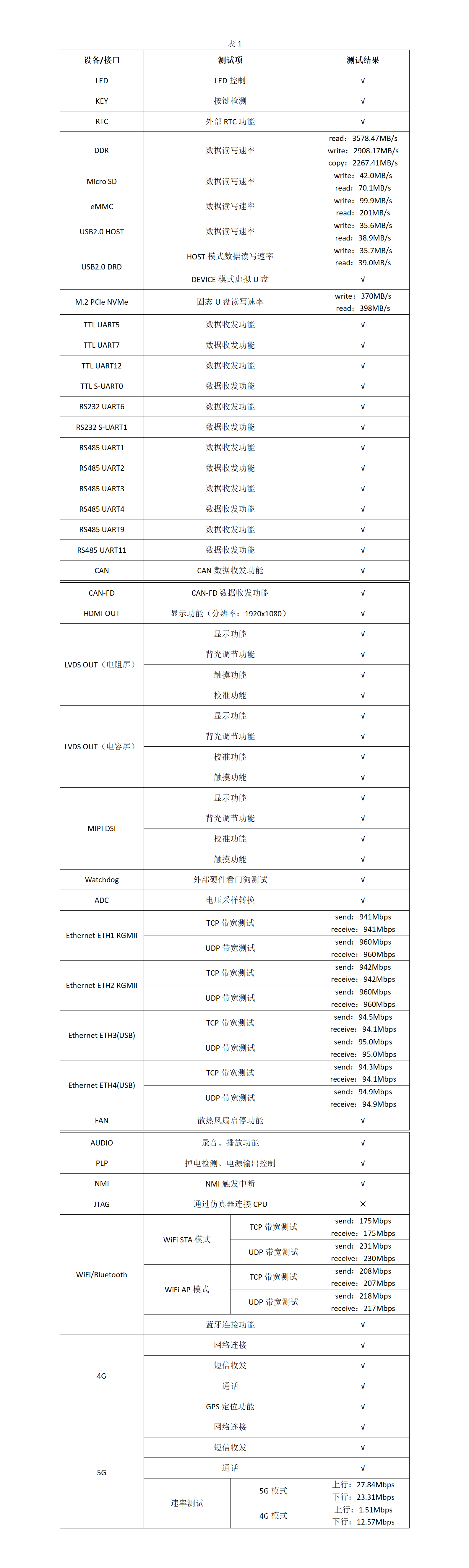

全志T536 4核A55 ARM+RISC-V+NPU 17路UART 工業開發板—評估板測試手冊

全志T536系列處理器特性概述 集成RISC-V E907協處理器

米爾全志T536核心板國產首發!17串口4CAN口、四核A55

首發!17串口4CAN口、四核A55,米爾發布全志T536核心板

創龍全志T536全國產(4核A55 ARM+RISC-V+NPU 17路UART)工業開發板硬件說明書

創龍全志T536全國產(4核A55 ARM+RISC-V+NPU 17路UART)工業開發板硬件說明書

評論