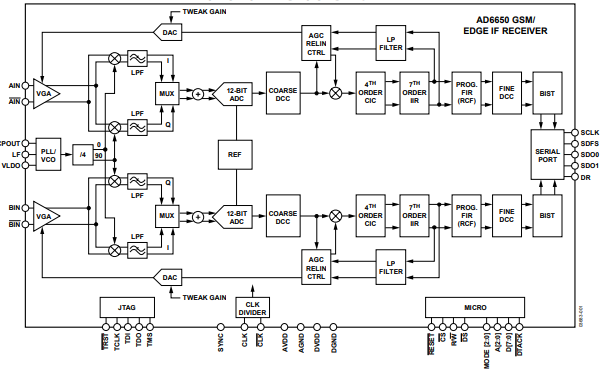

概述

AD6650是一款分集中頻至基帶接收機,適用于GSM/EDGE。這款窄帶接收機由一個集成DVGA、中頻至基帶I/Q解調器、低通濾波和一個雙通道寬帶ADC組成。該芯片可處理70 MHz至260 MHz的中頻輸入。接收機架構經過特別設計,整個接收信號路徑只需要一個用于主信號的外部表面聲波(SAW)濾波器和一個用于分集信號的濾波器,便可達到GSM/EDGE阻塞要求。

片內數字抽取與濾波電路可消除目標通道之外的干擾信號和噪聲。利用可編程RAM系數濾波器,只需一個經濟高效的濾波器,便可實現抗混疊、匹配濾波和靜態均衡三種功能。通道濾波器的輸出通過串行輸出I/Q數據流提供給用戶。

數據表:*附件:AD6650分集中頻至基帶GSM EDGE窄帶接收機技術手冊.pdf

應用

特性

- 動態范圍:116 dB

- 數字VGA

- I/Q解調器

- 有源低通濾波器

- 雙通道寬帶ADC

- 可編程抽取和通道濾波器

- VCO和鎖相環電路

- 串行數據輸出端口

框圖

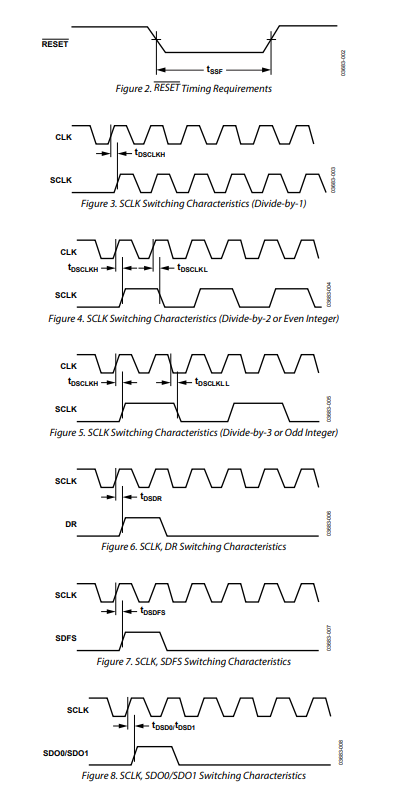

時序圖

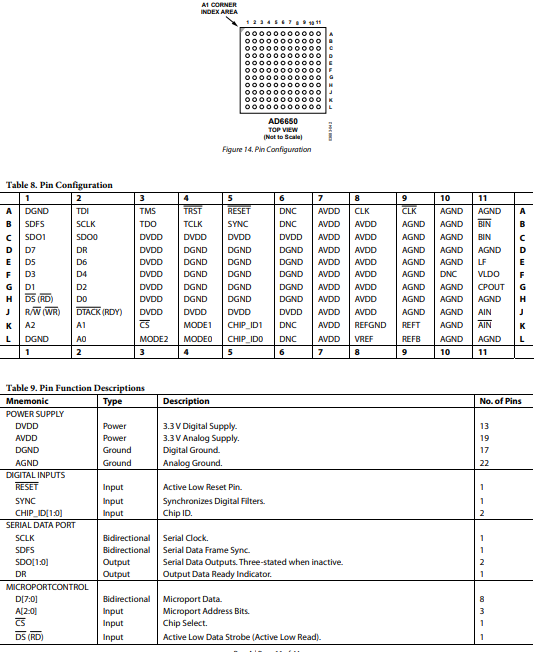

引腳配置描述

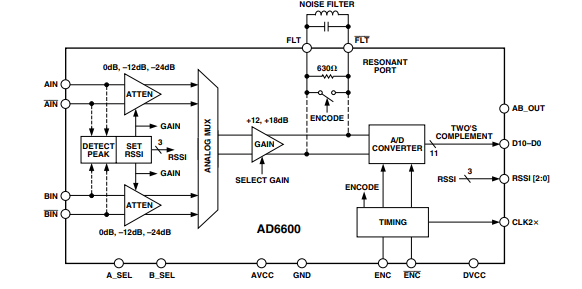

模擬前端

AD6650是一款混合信號前端(MxFE)組件,適用于需要高動態范圍的直接中頻采樣無線電設備。它針對GSM和EDGE標準的性能要求進行了優化。

AD6650包含五個信號處理階段:數字可變增益放大器(VGA)、同相/正交(I/Q)解調器、七階低通濾波器、雙ADC以及數字濾波。其編程和控制通過微處理器接口實現。

數字可變增益放大器(DVGA)

一個增益可變的數字VGA用于擴展ADC的動態范圍,并最大程度減少ADC輸入處的信號削波。VGA的最大增益為36 dB,標稱步長為0.094 dB。放大器級作為AD6650的輸入級,標稱輸入阻抗為200 Ω,輸入功率為4 dBm。

I/Q解調器

頻率轉換通過I/Q解調器實現。進入此級的實數據通過同相(I)和正交(Q)解調器分離。該級將輸入信號從70 MHz至260 MHz的中頻(IF)轉換為2.59 MHz的基帶頻率。

低通濾波器

每個I/Q信號路徑中都有一個七階低通有源濾波器,帶寬為3.5 MHz,具備自動阻容校準功能,校準精度為±4%。此濾波器通常能提供大于70 dB的2.59 MHz以上頻率的混疊抑制。

雙ADC

AD6650有兩個ADC,每個ADC都采用AD9238內核,前面有雙路跟蹤保持電路,分別以26 MSPS的速率對I和Q信號進行多路復用。滿量程輸入功率為4 dBm。

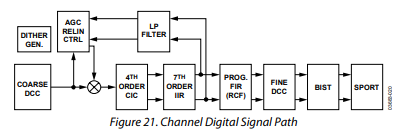

數字后端

12位ADC數據通過粗直流校正模塊,該模塊對I和Q路徑中的直流失調進行一次性校準。此模塊的輸出驅動自動增益控制(AGC)回路,該回路調節模擬路徑中數字控制的VGA。AGC調整輸入感興趣信號的幅度,達到可編程水平,防止ADC削波。VGA的增益從重新線性化模塊中減去。例如,如果外部AD6650的增益在20 dB至30 dB之間,由于信號功率從20 dB降至 - 20 dB,VGA必須增加30 dB的增益,以保持AD6650的總響應不變。

然后,AGC模塊的19位輸出通過CICA濾波器進行抽取和濾波,再經過IIR濾波器以及可編程隨機存取存儲器系數濾波器(RCF)。16位或24位數據通過串行端口輸出。

憑借36 dB的VGA增益、12位ADC性能以及高達21 dB的處理增益,AD6650能夠提供約116 dB的動態范圍或19位性能。出于這個原因,使用24位串行輸出,以確保動態范圍不會損失。數字信號路徑的框圖如圖21所示。

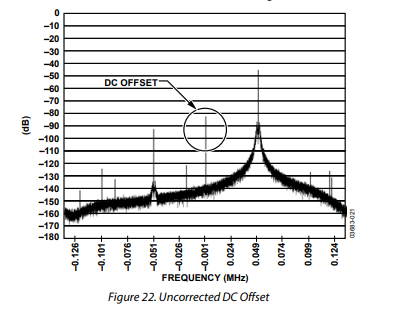

直流校正

AD6650模擬路徑中的直流失調源自三個方面:模擬基帶濾波器、ADC以及混頻器的本振(LO)泄漏。模擬濾波器和ADC的直流失調會導致LO泄漏產生直流偏移。I和Q路徑的直流失調不同,因為它們使用不同的模擬路徑,且每條路徑都獨立校正。

未校正的直流失調相對于ADC的滿量程(dBFS)通常在 - 32 dB至 - 35 dB之間。考慮到AGC范圍后,直流失調實際上會因增益設置而降低,當AD6650處于最大增益時,約為 - 68 dBFS至 - 71 dBFS或更小。

-

接收機

+關注

關注

8文章

1218瀏覽量

54219 -

GSM

+關注

關注

9文章

837瀏覽量

123952 -

EDGE

+關注

關注

0文章

188瀏覽量

43198

發布評論請先 登錄

AD6650 分集中頻至基帶GSM/EDGE窄帶接收機

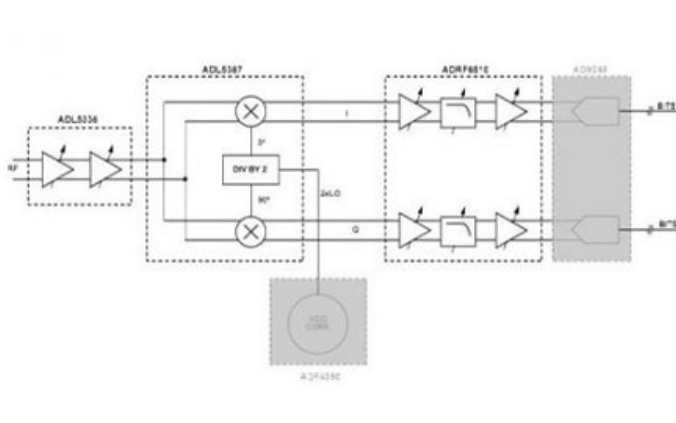

CN0320:基于IQ解調器,具有中頻和基帶可變增益以及可編程基帶濾波功能的中頻至基帶接收機

AD6650分集中頻至基帶GSM/EDGE窄帶接收機技術手冊

AD6650分集中頻至基帶GSM/EDGE窄帶接收機技術手冊

評論