概述

LTC6915 是一款精準的可編程增益放大器。 可通過一個并行或串行接口將增益設置為 0、1、2、4、8、16、32、64、128、256、512、1024、2048 或 4096。 在采用單 5V 電源以及任何設定增益的條件下,CMRR 通常為 125dB。 電壓失調低于 10uV,且溫度漂移小于 50nV/℃。

LTC6915 采用充電平衡采樣數據技術將一個差分輸入電壓轉換成一個單端信號,隨后再由一個零漂移運算放大器對該單端信號進行放大。

差分輸入的工作范圍為軌至軌,而單端輸出在軌至軌之間擺動。 LTC6915 既可在低至 2.7V 的單電源應用中使用,也可在采用雙 ±5V 電源的應用中使用。 LTC6915 采用 16 引線 SSOP 封裝和 12 引線 DFN 表面貼封裝。

數據表:*附件:LTC6915具有數字可編程增益的零漂移、精準儀表放大器技術手冊.pdf

應用

- 熱電偶放大器

- 電子衡器

- 醫療儀器

- 應變儀放大器

- 高分辨率數據采集

特性

- 14 級可編程的增益

- 與增益無關的 125dB CMRR

- 增益準確度:0.1% (典型值)

- 最大失調電壓:10uV

- 最大失調電壓漂移:50nV/℃

- 軌至軌輸入和輸出

- 用于增益設置的并行和串行 (SPI) 接口

- 工作電源:2.7V 至 ±5.5V

- 典型噪聲:2.5uV

P-P(0.01Hz 至 10Hz) - 采用 16 引線 SSOP 和 12 引線 DFN 封裝

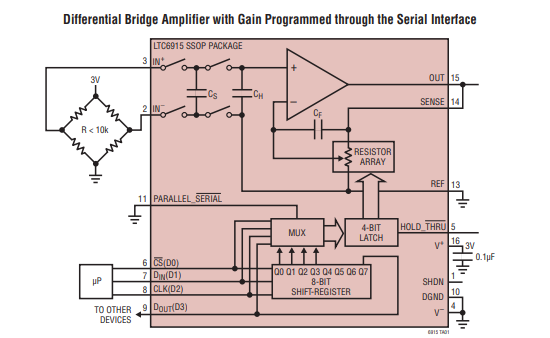

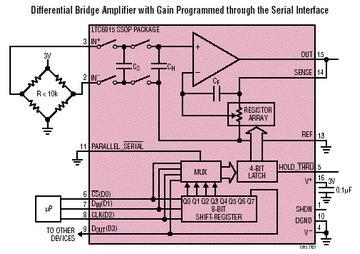

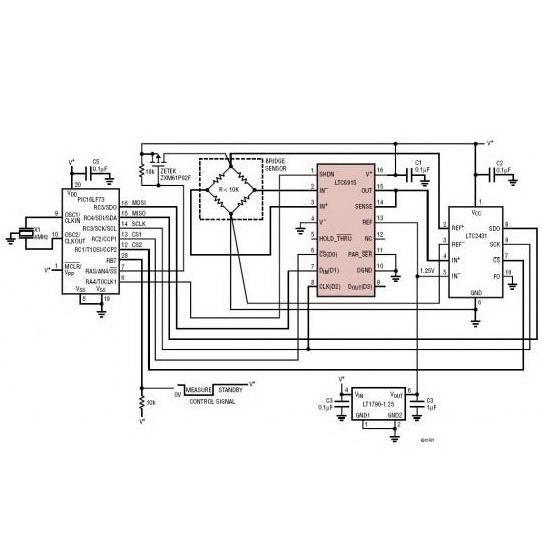

典型應用

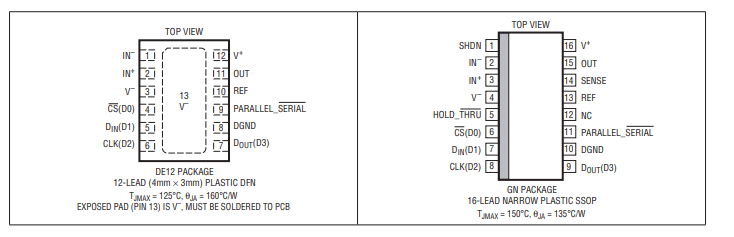

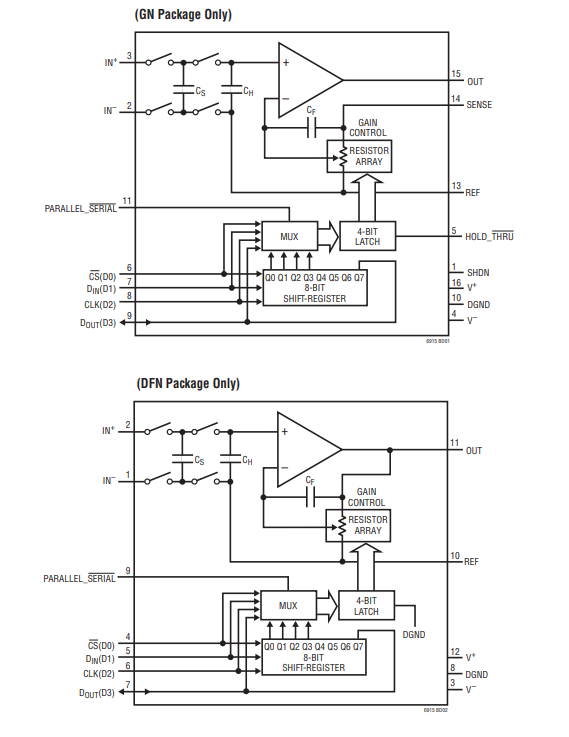

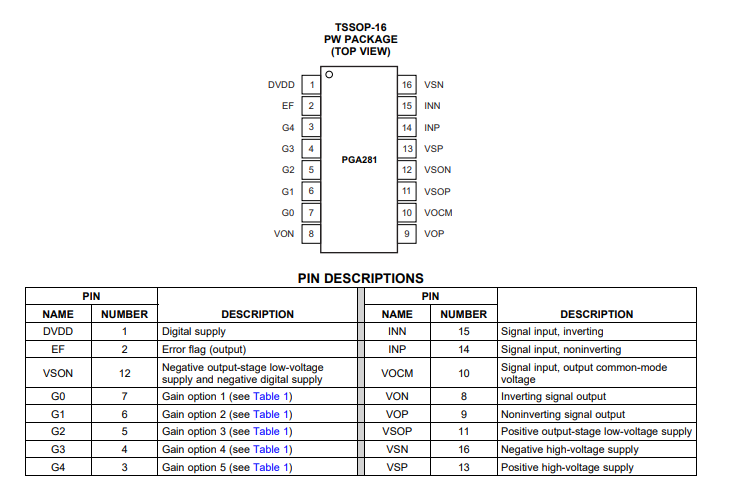

引腳配置描述

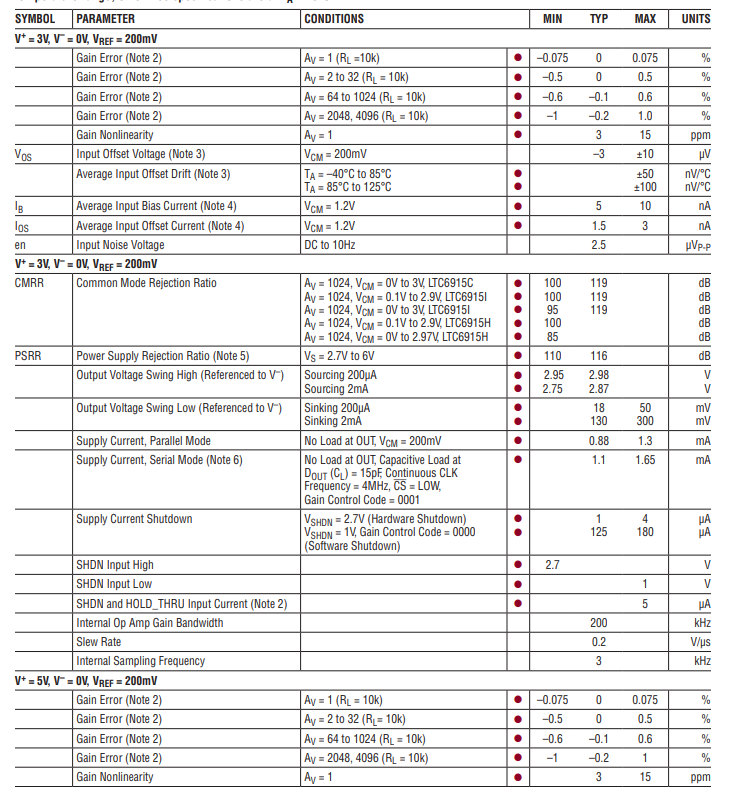

電特性

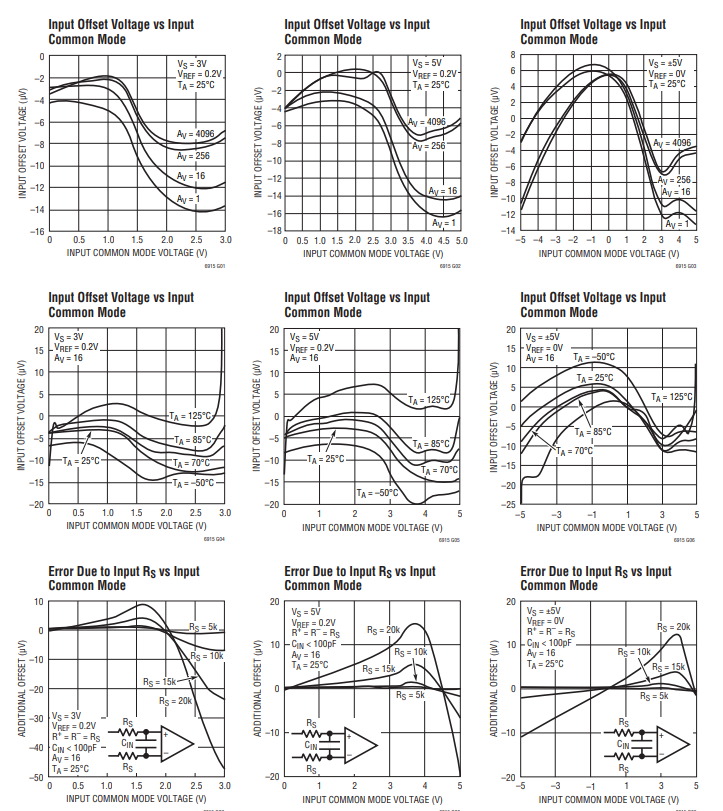

典型性能特征

引腳描述

引腳功能(DFN/GN封裝)

- IN?(引腳1/引腳2) :反相模擬輸入。

- SHDN(僅GN封裝的引腳1) :關斷引腳。當SHDN連接到V?時,芯片進入關斷狀態。當該引腳懸空時,內部電流源會將其拉至V? 。

- IN?(引腳2/引腳3) :同相模擬輸入。

- V?(引腳3/引腳4) :負電源。

- overline{CS}(D0)(引腳4/引腳6) :TTL電平輸入。在串行控制模式下,此引腳為片選輸入(低電平有效);在并行控制模式下,此引腳是并行增益控制碼的最低有效位(LSB)。

- D_{IN}(D1)(引腳5/引腳7) :TTL電平輸入。在串行控制模式下,此引腳為串行輸入數據;在并行控制模式下,此引腳是并行增益控制碼的次低有效位(第二LSB)。

- HOLD_THRU(僅GN封裝的引腳5) :用于并行控制模式的TTL電平輸入。當HOLD_THRU為高電平時,并行數據被鎖存。在內部D鎖存器中。

- CLK(D2)(引腳6/引腳8) :TTL電平輸入。在串行控制模式下,此引腳為串行接口的時鐘;在并行控制模式下,此引腳是并行增益控制碼的第三低有效位(第三LSB)。

- D_{OUT}(D3)(引腳7/引腳9) :TTL電平輸入。在串行控制模式下,此引腳為串行數據輸出;在并行模式下,此引腳是4位并行增益控制碼的最高有效位(MSB)。在并行模式操作中,如果D_{OUT}(引腳9)的數據來自電壓源且高于V?(引腳12),則需在電壓源和**D_{OUT}**之間連接一個電阻,將流入引腳9的電流限制在5mA或更低。

- DGND(引腳8/引腳10) :數字地。

- PARALLEL_SERIAL(引腳9/引腳11) :接口選擇輸入。當連接到V?時,為并行模式,即可編程增益放大器(PGA)的增益由并行碼(D3 - D0)定義,即overline{CS}(D0)、DATA(D1)、CLK(D2)、D_{OUT}(D3) ;當PARALLEL_SERIAL引腳連接到V?時,PGA增益由串行接口設置。

- REF(引腳10/引腳13) :PGA輸出的電壓基準。

- OUT(引腳11/引腳15) :放大器輸出。OUT引腳的典型灌電流/拉電流為1mA。對于最小增益誤差,負載電阻應為1 kΩ或更大(參考“典型性能特征”中的“輸出電壓擺幅與輸出電流”以及“增益誤差與負載電阻” )。

- V?(引腳12/引腳16) :正電源。

- SENSE(僅GN封裝的引腳14) :檢測引腳。當PGA驅動低電阻負載且OUT引腳與負載之間的互連電阻不可忽略時,將SENSE引腳盡可能靠近負載連接,可提高增益精度。

框圖

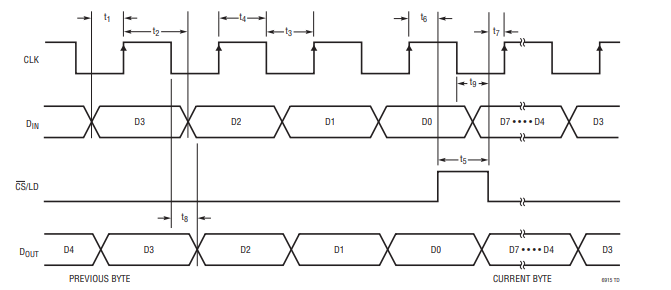

時序圖

-

放大器

+關注

關注

145文章

14096瀏覽量

216231 -

增益放大器

+關注

關注

2文章

152瀏覽量

29467 -

LTC6915

+關注

關注

0文章

2瀏覽量

6486

發布評論請先 登錄

具有數字可編程增益的零漂移、精準儀表放大器

LTC6915 具有數字可編程增益的零漂移、精準儀表放大器

LTC2053/LTC2053-SYNC:精密、軌對軌、零漂移、電阻式可編程儀表放大器數據表

UG-1443:評估ADA4254零漂移、高電壓、低功耗、可編程增益儀表放大器

LTC6915具有數字可編程增益的零漂移、精準儀表放大器技術手冊

LTC6915具有數字可編程增益的零漂移、精準儀表放大器技術手冊

評論