概述

AD8331/AD8332/AD8334分別為單通道、雙通道和四通道超低頻噪聲可變增益放大器(VGA)。它們針對線性度進行了優化,在高達120 MHz的頻率下可用作低噪聲可變增益元件。

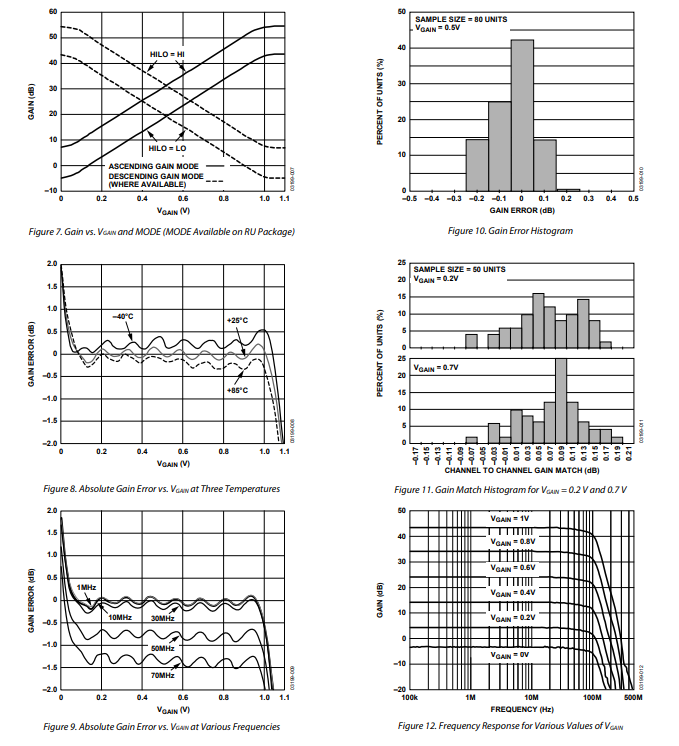

48 dB的增益范圍使這些器件適用于各種應用。卓越的寬帶平坦度在整個增益范圍內都能保持。90 dB/V的增益控制斜率可實現線性的dB標度增益控制,電壓范圍為40 mV至1 V。工廠微調可確保出色的部分對部分以及通道對通道的增益匹配。

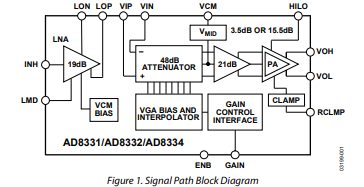

各通道內置一個超低噪聲前置放大器(LNA)、一個48 dB增益范圍的X-AMP? VGA以及一個具有可調輸出限制功能的可選增益后置放大器。LNA增益為19 dB,具有單端輸入和差分輸出。LNA輸入阻抗可以利用一個電阻來調節,以便與信號源相匹配,且不影響噪聲性能。

VGA的48 dB增益范圍使這些器件適合各種不同的應用。帶寬在整個增益范圍內可保持出色的一致性。對于40 mV至1 V范圍內的控制電壓,增益控制接口可提供精確的50 dB/V線性dB調整。通過工廠調整可確保器件間及通道間具有出色的增益匹配特性。差分信號路徑提供出色的二次和三次失真性能及低串擾。

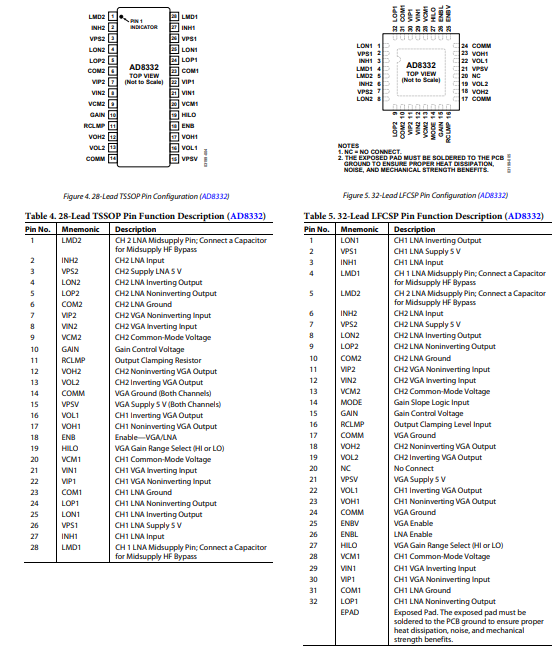

AD8332的工作溫度范圍為-40℃至+85℃,采用28引腳TSSOP和32引腳LFCSP兩種封裝。

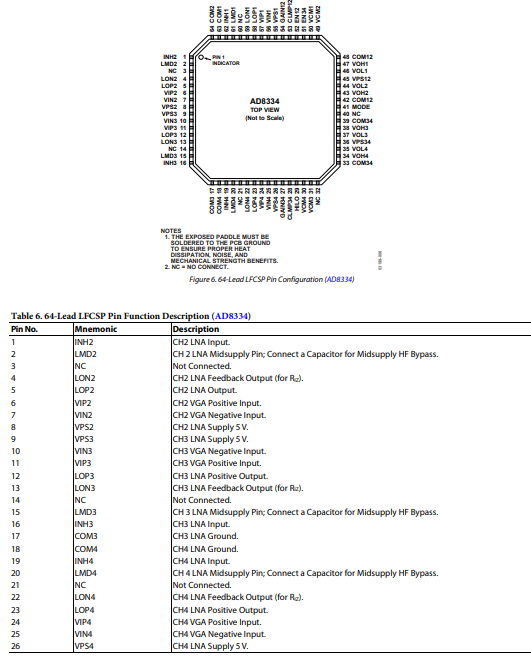

AD8332為雙通道版本,AD8331為單通道版本,AD8334為四通道版本。

數據表:*附件:AD8331 AD8332 AD8334內置超低噪聲前置放大器和可編程輸入阻抗(RIN)的雙通道VGA技術手冊.pdf

應用

特性

- 超低噪聲前置放大器

電壓噪聲 = 0.74 nV/√Hz

電流噪聲 = 2.5 pA/√Hz - 3 dB帶寬: 100 MHz

- 低功耗: 每通道145 mW

- 寬增益范圍,內置可編程后置放大器

-4.5 dB至+43.5 dB

+7.5 dB至+55.5 dB - 低輸出參考噪聲

48 nV/√Hz典型值 - 有源輸入阻抗匹配

- 針對10位/12位ADC優化

- 可選的輸出箝位電平

- 采用5 V單電源供電

- 采用引腳架構芯片級封裝

功能框圖

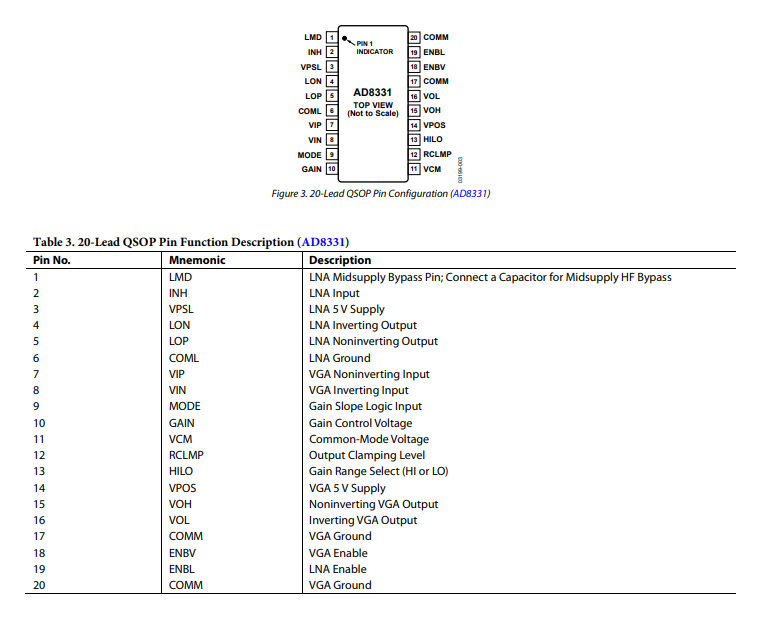

引腳配置描述

典型性能特征

應用信息

低噪聲放大器(LNA)——外部組件

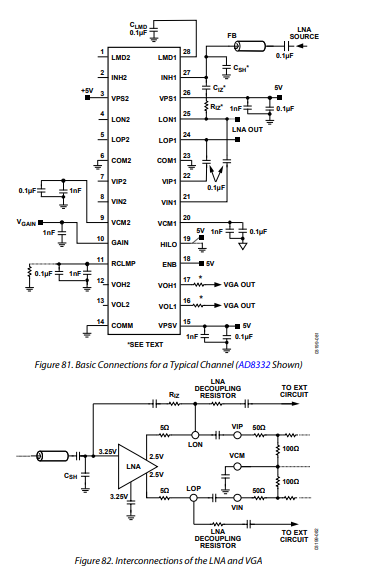

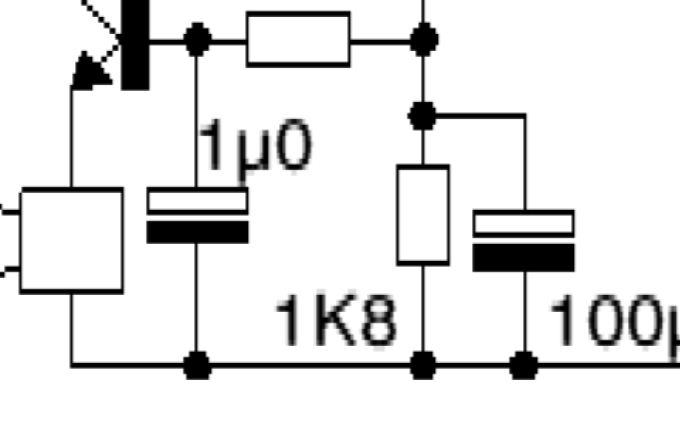

LMD引腳(連接到偏置電路)必須通過接地進行旁路,并且信號源應通過電容耦合到LNA引腳,該電容值在0.1μF至2.2μF之間(見圖81)。

LNA的未端接輸入阻抗為6 kΩ。用戶可以根據公式6合成50Ω至6 kΩ之間的任何LNA輸入電阻,或者從表7中選擇。

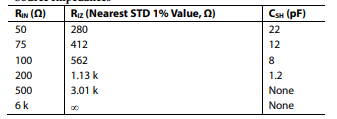

表7. 常見源阻抗的LNA外部組件值

當使用有源輸入端接時,需要一個去耦電容(C_{ST})來隔離LNA的輸入和輸出偏置電壓。

并聯輸入電容**C_{ST}**會在較高頻率下降低增益峰值,此時增益滾降是由于LNA在高頻下的增益滾降造成的。**C_{ST}的值在R_{EQ}**增加到500Ω時減小,在該點不需要電容。對于50Ω≤R_{IN}≤200Ω,**C_{ST}**的建議值見表7。

當無法避免LNA引腳INH的長走線時,或者如果兩個LNA輸出都驅動外部電路,在引腳INH的信號線上串聯一個小型鐵氧體磁珠(FB)會很有用,它可以抑制噪聲。該磁珠在100 MHz時為75Ω(村田BLM21或等效產品)。圖82顯示了LNA輸出的互連細節。

LNA輸出與VGA輸入之間需要電容耦合。由于5Ω的輸出電阻,需要考慮LNA輸出和VGA輸入之間的直流電平差異以及電容值的影響。建議電容值為0.1μF。LNA輸出端與VGA輸入端之間存在0.4 dB的損耗。在LNP和LNN輸出端增加額外負載會影響LNA增益。

LNA的兩個輸出均可用于驅動外部電路。當需要單端LNA輸出時,應使用引腳LOP。用戶應注意LNA輸出的雜散電容負載,特別是LON。LNA可以在10 pF的并聯電容下驅動100Ω負載。如果LNA輸出連接到遠程印刷電路板,添加一個4.99Ω的串聯電阻或在100 MHz時為75Ω的鐵氧體磁珠可以防止振蕩。

增益輸入

AD8332的兩個通道共用GAIN引腳。其輸入阻抗標稱值為1 MΩ,建議使用100 pF至1 nF的旁路電容。

并聯設備可由一個公共電壓源或DAC驅動。考慮到驅動波形的帶寬要求,需利用總分布電容進行解耦。

在LO增益模式下,增益控制噪聲成為一個因素,主要是≤15 nV/√Hz。在GAIN引腳內部,噪聲增益約為15 nV/√Hz。在HI增益模式下,增益控制噪聲可忽略不計。

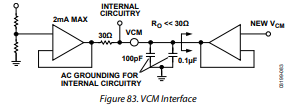

共模電壓輸入(VCM)

VCM引腳、VOL引腳和VOH引腳的共模電壓默認值為2.5 V直流。在交流耦合應用中,VCM引腳未端接,但仍需在靠近差分電路的位置進行交流接地旁路。VGA輸出可為ADC提供直流接地,這樣ADC的共模輸出電壓可通過在VCM引腳施加1.5 V至3.5 V來設置。在直流耦合操作中,當VCM引腳由單獨的電源供電時,不建議這樣做。

VCM引腳上的電壓由一個具有30 Ω輸出阻抗和±2 mA默認輸出電流的片內緩沖器提供(見圖83)。如果VCM引腳由外部電源供電,其輸出阻抗應遠小于30 Ω,且其電流驅動能力應大于2 mA。如果多個設備并聯連接,外部緩沖器應能夠共同吸收總輸出電流。當使用2.5 V以外的共模電壓時,需要一個限壓電阻**R_{LIMIT}**來防止過壓。

邏輯輸入——使能(ENB)、模式(MODE)和高低增益選擇(HILO)

所有使能引腳的輸入阻抗標稱值為25 kΩ,可上拉至5 V(推薦使用上拉電阻),也可由3 V或5 V邏輯電平驅動。使能引腳在電源斷電時為低電平,VGA輸出電壓接近地電位。多個設備可由一個公共源驅動。有關功能控制的更多信息,請參考表3、表4、表5和表6。

HILO引腳可與3 V或5 V CMOS邏輯電平兼容。它可以接地或上拉至5 V,具體取決于所需的增益范圍和輸出噪聲。

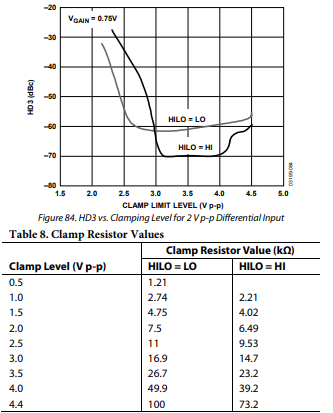

可選輸出電壓限制

RCLMP引腳為用戶提供了一種在過載情況下限制輸出電壓擺幅的方法。峰值到峰值限制電壓通過與地連接的電阻進行調整(見表8中的多個調整電壓和對應電阻值)。未連接時,默認限制電平為4.5 V峰峰值。請注意,三次諧波失真會隨著波形削波而增加。為實現最低失真,對于1 V峰峰值輸入擺幅的轉換器,箝位電平應設置為1.5 V峰峰值;對于2 V峰峰值輸入擺幅,設置為2.7 V峰峰值;對于0.5 V峰峰值輸入擺幅,設置為1 V峰峰值。最佳設置需通過實驗確定。圖84顯示了在2 V峰峰值差分輸入信號下,二次諧波失真與2增益模式下限制電平的函數關系。在HI增益模式下,更寬的限制電平是可取的。

輸出解耦

當驅動電容大于約10 pF的負載,或在其他電路板上有長電路連接時,添加電阻和/或鐵氧體磁珠組成的輸出網絡有助于確保穩定性。可以加入如81圖所示的奈奎斯特濾波器等組件。在評估板中,該電阻值為84.5 Ω。例如,在應用中使用120 nH磁珠時,可將該電阻與低阻值電阻并聯,以盡量減少負載變化。

-

增益放大器

+關注

關注

2文章

152瀏覽量

29468 -

VGA

+關注

關注

5文章

572瀏覽量

64176 -

AD8331

+關注

關注

0文章

3瀏覽量

7810

發布評論請先 登錄

放大器,低噪聲前置放大器參數,前置放大器廠家

AD8331前置放大器反饋電阻Riz的阻值匹配所有的Riz嗎?

AD8331/AD8332/AD8334,pdf datas

低噪聲前置放大器電路的設計步驟

AD8332 內置超低噪聲前置放大器和可編程輸入阻抗(RIN)的雙通道VGA

AD8334 內置超低噪聲前置放大器和可編程輸入電阻(RIN)的四通道VGA

AD8331 內置超低噪聲前置放大器和可編程輸入阻抗(RIN)的單通道VGA

AD8331/AD8332/AD8334:帶前置放大器和可編程輸入電阻(R<sub>IN</sub>)的超低噪聲VGA

AD8332-EVALZ:雙VGA、超低噪聲前置放大器和可編程RIN評估板數據表

AD8331/AD8332/AD8334內置超低噪聲前置放大器和可編程輸入阻抗(RIN)的雙通道VGA技術手冊

AD8331/AD8332/AD8334內置超低噪聲前置放大器和可編程輸入阻抗(RIN)的雙通道VGA技術手冊

評論