概述

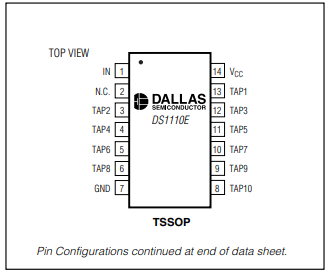

DS1110延遲線是DS1010的升級替代產品。它含有10個等間隔的抽頭,可以提供5ns至500ns的延遲。這些器件采用標準16引腳SO或14引腳TSSOP封裝。DS1110系列延遲線在5V,+25°C時,提供±5%或±2ns (較大者)的額定精度。輸入DS1110的邏輯信號經過一個固定延遲(由型號后的尾綴確定)后在10抽頭輸出端再現。DS1110具有相同精度的前沿和后沿延遲。每個抽頭可驅動10個74LS負載。Dallas Semiconductor可以為用戶定制標準產品,以滿足特殊需求。

數據表:*附件:DS1110 10抽頭硅延遲線技術手冊.pdf

應用

- 自動測試設備(ATE)

- 通信系統

- 醫療設備

- PC外設設備

特性

- 全硅、5V、10抽頭延遲線

- 直接替代DS1010的升級產品

- 10個等間隔抽頭

- 穩定、精確的延遲

- 相同的前沿與后沿精度

- 在5V,+25°C時,延遲容差±5%或±2ns (較大者)

- 經濟型

- 自動嵌入,低截面

- 低功耗CMOS

- TTL/CMOS兼容

- 兼容汽相、紅外和波峰焊

- 快速周轉原型

- 提供商業級與工業級溫度范圍的延遲線

- 可定制延遲

- 采用標準16引腳SO或14引腳TSSOP封裝

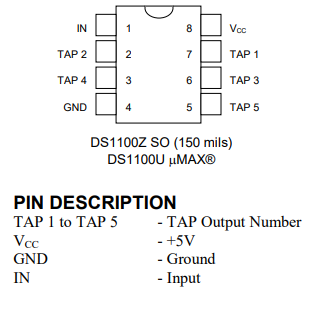

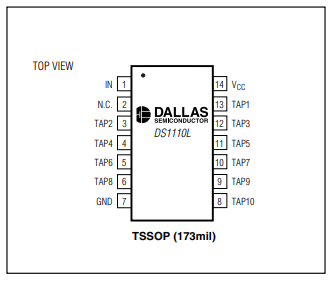

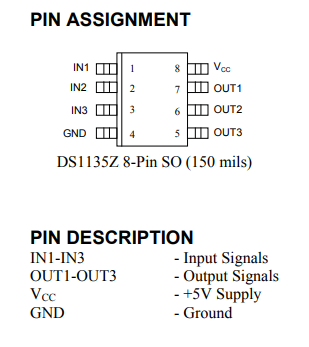

引腳配置描述

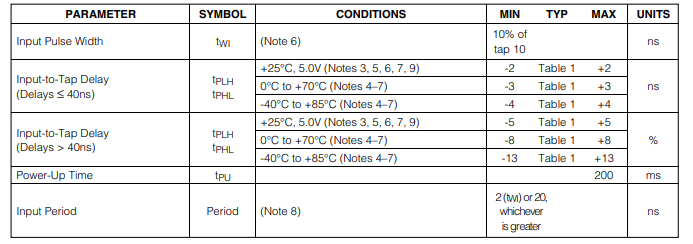

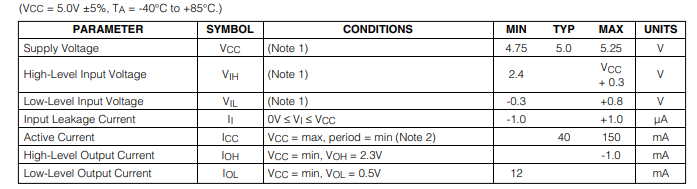

交流電氣特性

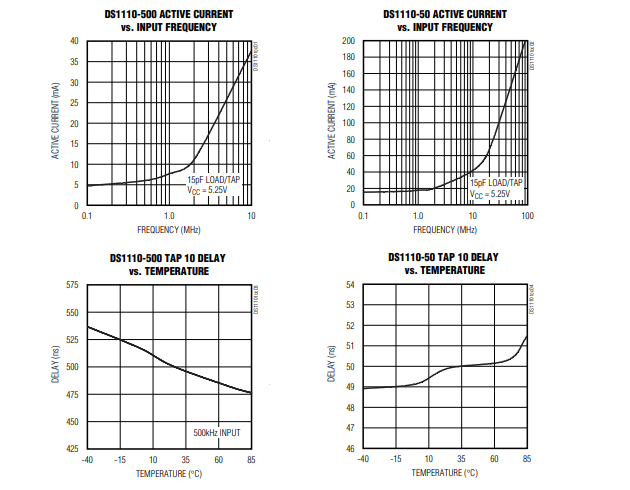

典型操作特性

詳細說明

DS1110 延遲線是 DS1010 的改進版本。它有十個等間距抽頭,可提供 15 納秒至 500 納秒的延遲。該器件采用標準 16 引腳 SO 或 14 引腳 TSSOP 封裝。DS1110 系列延遲線的標稱精度為 ±5% 或 ±2 納秒,在 0.5V 至 +25°C 條件下精度更高。DS1110 在抽頭 10 輸出端復制輸入邏輯狀態,從而減少了由部件編號引起的固定延遲。DS1110 旨在產生帶訓練邊緣的延遲,以確保精度。每個抽頭能夠驅動多達 74LS 類型負載。

術語

- 周期(Period) :第一個脈沖的上升沿與后續脈沖上升沿之間的時間間隔。

- 脈沖寬度(tWI,Pulse Width) :脈沖從上升沿 1.5V 點到下降沿 1.5V 點,以及從下降沿 1.5V 點到上升沿 1.5V 點之間的時間間隔。

- 輸入上升時間(tRISE,Input Rise Time) :輸入脈沖上升沿從 20% 幅度點到 80% 幅度點的時間間隔。

- 輸入下降時間(tFALL,Input Fall Time) :輸入脈沖下降沿從 80% 幅度點到 20% 幅度點的時間間隔。

- 上升沿時間延遲(tPLH,Time Delay, Rising) :輸入脈沖上升沿 1.5V 點與任意抽頭輸出脈沖上升沿 1.5V 點之間的時間間隔。

- 下降沿時間延遲(tPHL,Time Delay, Falling) :輸入脈沖下降沿 1.5V 點與任意抽頭輸出脈沖下降沿 1.5V 點之間的時間間隔。

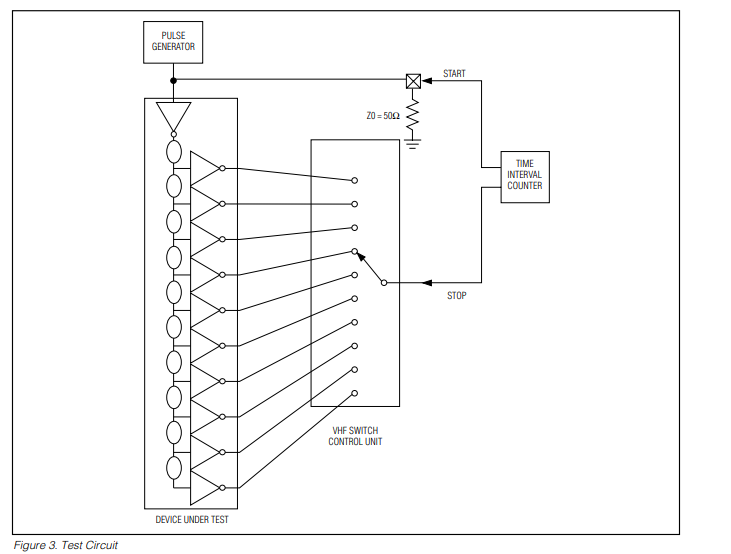

測試設置說明

圖 3 展示了用于測量 DS1110 定時參數的硬件配置。精密脈沖發生器在軟件控制下生成輸入波形。時間延遲由連接的時間間隔計數器(分辨率為 20 皮秒)測量。

-

封裝

+關注

關注

128文章

8522瀏覽量

144826 -

延遲

+關注

關注

1文章

74瀏覽量

13737 -

引腳

+關注

關注

16文章

1576瀏覽量

52374

發布評論請先 登錄

DS1110E-80+ 時鐘/計時 - 延遲線

DS1110E-400+ 時鐘/計時 - 延遲線

DS1110E-200+ 時鐘/計時 - 延遲線

DS1110LE-250+ 時鐘/計時 - 延遲線

DS1110S-450+ 時鐘/計時 - 延遲線

DS1110S-300+ 時鐘/計時 - 延遲線

DS1110E-300+ 時鐘/計時 - 延遲線

DS1110S-50+ 時鐘/計時 - 延遲線

DS1110E-450+ 時鐘/計時 - 延遲線

DS1110LE-125+ 時鐘/計時 - 延遲線

DS1110LE-60+ 時鐘/計時 - 延遲線

DS1110 10抽頭硅延遲線技術手冊

DS1110 10抽頭硅延遲線技術手冊

評論