做一款芯片最基本的環(huán)節(jié)是設(shè)計(jì)->流片->封裝->測試,芯片成本構(gòu)成一般為人力成本20%,流片40%,封裝35%,測試5%【對于先進(jìn)工藝,流片成本可能超過60%】。

測試其實(shí)是芯片各個環(huán)節(jié)中最“便宜”的一步,在這個每家公司都喊著“Cost Down”的激烈市場中,人力成本逐年攀升,晶圓廠和封裝廠都在乙方市場中“叱咤風(fēng)云”,唯獨(dú)只有測試顯得不那么難啃,Cost Down的算盤落到了測試的頭上。

但仔細(xì)算算,測試省50%,總成本也只省2.5%,流片或封裝省15%,測試就相當(dāng)于免費(fèi)了。但測試是產(chǎn)品質(zhì)量最后一關(guān),若沒有良好的測試,產(chǎn)品PPM【百萬失效率】過高,退回或者賠償都遠(yuǎn)遠(yuǎn)不是5%的成本能代表的。

芯片需要做哪些測試呢?

主要分三大類:芯片功能測試、性能測試、可靠性測試,芯片產(chǎn)品要上市三大測試缺一不可。在半導(dǎo)體芯片測試中,CP測試(Chip Probing, 晶圓測試)和FT測試(Final Test, 成品測試)是兩個十分關(guān)鍵的階段。它們分別對應(yīng)于芯片在封裝前后的測試,確保產(chǎn)品的質(zhì)量和性能。

功能測試,是測試芯片的參數(shù)、指標(biāo)、功能,的驗(yàn)證。

性能測試,由于芯片在生產(chǎn)制造過程中,有無數(shù)可能的引入缺陷的步驟,即使是同一批晶圓和封裝成品,芯片也各有好壞,所以需要進(jìn)行篩選。

可靠性測試,芯片通過了功能與性能測試,得到了好的芯片,但是芯片會不會被冬天里最討厭的靜電弄壞,在雷雨天、三伏天、風(fēng)雪天能否正常工作,以及芯片能用一個月、一年還是十年等等,這些都要通過可靠性測試進(jìn)行評估。

那要實(shí)現(xiàn)這些測試,我們有哪些手段呢?

測試方法:板級測試、晶圓CP測試、封裝后成品FT測試、系統(tǒng)級SLT測試、可靠性測試,多策并舉。

板級測試,主要應(yīng)用于功能測試,使用PCB板+芯片搭建一個“模擬”的芯片工作環(huán)境,把芯片的接口都引出,檢測芯片的功能,或者在各種嚴(yán)苛環(huán)境下看芯片能否正常工作。需要應(yīng)用的設(shè)備主要是儀器儀表,需要制作的主要是EVB評估板。

1. CP測試(Chip Probing, 晶圓測試)

1.1 定義

CP測試是在晶圓制造完成后、芯片封裝前進(jìn)行的電性測試。它通過探針卡(Probe Card)接觸芯片的焊盤(Pad),利用自動測試設(shè)備(ATE)測試芯片的基本功能和電性參數(shù),以篩選不良芯片。

1.2 主要目的

? 篩選不良芯片,避免浪費(fèi)封裝成本。

? 驗(yàn)證芯片基本性能,確保其符合規(guī)格要求。

? 數(shù)據(jù)收集,用于晶圓良率分析、工藝優(yōu)化和失效分析。

主要測試內(nèi)容

1. 直流測試(DC Test)

? 工作電壓(Vdd, Vss)

? 漏電流(Ioff, Leakage)

? 靜態(tài)電流(IDDQ Test)

? 輸入/輸出電平(VIH, VIL, VOH, VOL)

2. 交流測試(AC Test)

? 時序測試(Timing Test)

? 傳播延遲(Propagation Delay)

? 工作頻率測試(Functional Frequency Test)

3. 功能測試(Functional Test)

? 邏輯功能測試(如存儲器讀寫測試)

? 特殊模式測試(如Scan Chain, MBIST, JTAG)

封裝后成品FT測試,常應(yīng)用與功能測試、性能測試和可靠性測試中,檢查芯片功能是否正常,以及封裝過程中是否有缺陷產(chǎn)生,并且?guī)椭诳煽啃詼y試中用來檢測經(jīng)過“火雪雷電”之后的芯片是不是還能工作。需要應(yīng)用的設(shè)備主要是自動測試設(shè)備【ATE】+機(jī)械臂【Handler】+儀器儀表,需要制作的硬件是測試板【Loadboard】+測試插座【Socket】等。

系統(tǒng)級SLT測試,常應(yīng)用于功能測試、性能測試和可靠性測試中,常常作為成品FT測試的補(bǔ)充而存在,顧名思義就是在一個系統(tǒng)環(huán)境下進(jìn)行測試,就是把芯片放到它正常工作的環(huán)境中運(yùn)行功能來檢測其好壞,缺點(diǎn)是只能覆蓋一部分的功能,覆蓋率較低所以一般是FT的補(bǔ)充手段。需要應(yīng)用的設(shè)備主要是機(jī)械臂【Handler】,需要制作的硬件是系統(tǒng)板【System Board】+測試插座【Socket】。

FT測試的設(shè)備

? Handler(上下料設(shè)備):Multitest, Cohu, Seiko Epson

? ATE(自動測試設(shè)備):Advantest, Teradyne, National Instruments

? 燒錄設(shè)備(Programming Equipment):用于燒錄固件的芯片

可靠性測試,主要就是針對芯片施加各種苛刻環(huán)境,比如ESD靜電,就是模擬人體或者模擬工業(yè)體去給芯片加瞬間大電壓。再比如老化HTOL【High Temperature Operating Life】,就是在高溫下加速芯片老化,然后估算芯片壽命。還有HAST【Highly Accelerated Stress Test】測試芯片封裝的耐濕能力,待測產(chǎn)品被置于嚴(yán)苛的溫度、濕度及壓力下測試,濕氣是否會沿者膠體或膠體與導(dǎo)線架之接口滲入封裝體從而損壞芯片。當(dāng)然還有很多很多手段,不一而足,未來專欄講解。

總結(jié)

芯片測試的重要性,是確保芯片質(zhì)量和可靠性的最后一道防線。一個經(jīng)過充分測試的芯片,可以提供給客戶更高的可靠性和性能,增強(qiáng)公司的聲譽(yù)和競爭力。同時,芯片測試也對整個芯片設(shè)計(jì)和制造過程起到了指導(dǎo)作用,幫助發(fā)現(xiàn)和解決潛在的問題,提升整體生產(chǎn)效率和產(chǎn)品質(zhì)量。芯片測試的結(jié)果:好芯片被錯殺(沒通過測試),叫Yield Loss(產(chǎn)量損失)或over kill;壞芯片通過測試,叫Test Escape(測試逃逸);好的通過,壞的沒過,這是最理想的情況。Test Escape(測試逃逸)是指在測試芯片時,有些問題或缺陷沒有被發(fā)現(xiàn),從而逃脫了測試的范圍。這就像是有些壞點(diǎn)或故障在測試過程中被漏過了,最后進(jìn)入了市場。這可能導(dǎo)致產(chǎn)品的質(zhì)量問題和用戶的投訴。Yield Loss(產(chǎn)量損失)是指在制造芯片時,由于測試發(fā)現(xiàn)了一些問題或缺陷,導(dǎo)致了更多的芯片被判定為不合格而無法使用。這些不合格的芯片將會增加成本,并浪費(fèi)了制造能力。這兩個概念之間存在一種平衡。如果測試方法不夠嚴(yán)格,可能會有更多的測試逃逸,但產(chǎn)量損失可能較低。相反,如果測試方法過于嚴(yán)格,可能會減少測試逃逸,但產(chǎn)量損失可能會增加。因此,在芯片測試中,需要設(shè)計(jì)合理的測試方案。

聲明:

本號對所有原創(chuàng)、轉(zhuǎn)載文章的陳述與觀點(diǎn)均保持中立,推送文章僅供讀者學(xué)習(xí)和交流。文章、圖片等版權(quán)歸原作者享有,如有侵權(quán),聯(lián)系刪除。

北京漢通達(dá)科技主要業(yè)務(wù)為給國內(nèi)用戶提供通用的、先進(jìn)國外測試測量設(shè)備和整體解決方案,產(chǎn)品包括多種總線形式(臺式/GPIB、VXI、PXI/PXIe、PCI/PCIe、LXI等)的測試硬件、相關(guān)軟件、海量互聯(lián)接口等。經(jīng)過二十年的發(fā)展,公司產(chǎn)品輻射全世界二十多個品牌,種類超過1000種。值得一提的是,我公司自主研發(fā)的BMS測試產(chǎn)品、芯片測試產(chǎn)品代表了行業(yè)一線水平。

-

芯片

+關(guān)注

關(guān)注

459文章

52224瀏覽量

436587 -

測試

+關(guān)注

關(guān)注

8文章

5634瀏覽量

128355

發(fā)布評論請先 登錄

層出不窮的信號發(fā)生器可有效節(jié)省測試時間

功能測試儀的測試原理、功能及與在線測試的區(qū)別

通過界面和功能測試不能保證AI軟件的質(zhì)量

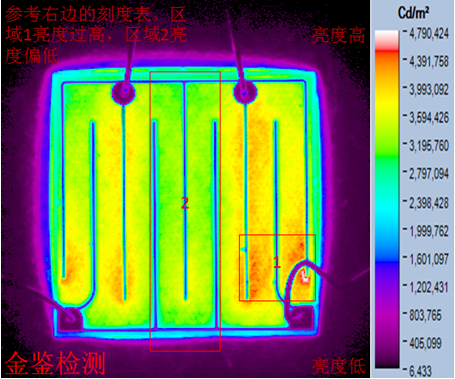

LED芯片發(fā)光均勻度測試案例分析

芯片不能窮測試

芯片不能窮測試

評論