概述

ADMV4821 是一款硅鍺 (SiGe)、24 GHz 毫米波 (mmW) 至 29.5 GHz 毫米波 5G 波束成形器。RF IC 高度集成,包含 16 個獨(dú)立通道,具有發(fā)射和接收功能。ADMV4821通過獨(dú)立的 RFV 和 RFH 輸入/輸出公共引腳支持 8 個水平和 8 個垂直極化天線。

數(shù)據(jù)表:*附件:ADMV4821 24至29.5GHz TX RX 雙極化波束形成器技術(shù)手冊.pdf

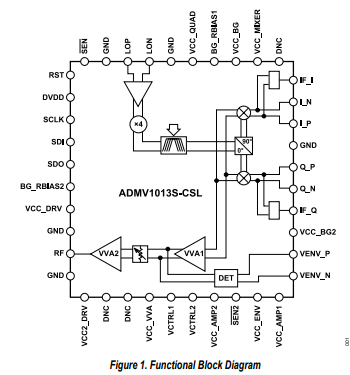

在發(fā)射模式下,RFV 和 RFH 輸入信號通過兩個獨(dú)立的 1:8 功率分配器進(jìn)行分離,并通過八個獨(dú)立的相應(yīng)發(fā)射通道。在此模式下,每個通道包括一個用于控制相位的矢量調(diào)制器 (VM) 和兩個用于控制幅度的數(shù)字可變增益放大器 (DVGA)。

在接收模式下,輸入信號通過兩組八個接收通道(垂直或水平),并通過一個連接到 RFV 引腳的獨(dú)立 8:1 合路器和一個連接到 RFH 引腳的獨(dú)立 8:1 合路器進(jìn)行組合。在此模式下,每個通道包括一個用于控制相位的 VM 和一個用于控制幅度的 DVGA。

VM 在發(fā)射或接收模式下提供完整的 360° 相位調(diào)整范圍。VM 為 5.625° 相位步長提供 6 位分辨率。

在傳輸模式下,DVGA 總動態(tài)范圍調(diào)整范圍為 32.4 dB。DVGA 提供 5 位或 6 位分辨率,分別產(chǎn)生 1.0 dB 或 0.5 dB 的幅度步長。

在接收模式下,DVGA 允許 17.1 dB 的動態(tài)范圍調(diào)整。DVGA 還提供 6 位分辨率,從而產(chǎn)生 0.5 dB 的幅度步長。DVGA 在整個增益范圍內(nèi)提供平坦的相位響應(yīng)。

發(fā)射機(jī)通道包含單獨(dú)的功率檢測器,用于檢測和校準(zhǔn)每個通道的增益以及通道間的增益失配。將 ADMV4821 RF 端口直接連接到貼片天線,以創(chuàng)建雙極化毫米波 5G 子陣列。

用戶可以使用 3 線或 4 線串行端口接口 (SPI) 對 ADMV4821 進(jìn)行編程。集成的片上低壓差 (LDO) 穩(wěn)壓器為 SPI 電路產(chǎn)生 1.8 V 電源,以減少所需的電源域數(shù)量。有多種 SPI 模式可在正常工作期間實現(xiàn)快速啟動和控制。

用戶可以單獨(dú)設(shè)置每個通道的幅度和相位,也可以通過使用片上存儲器進(jìn)行波束成形來同時對多個通道進(jìn)行編程。片上存儲器可存儲多達(dá) 256 個波束位置,這些位置可以任意組合分配給發(fā)射器或接收器模式。此外,4 個地址引腳允許對同一串行線路上的多達(dá) 16 個器件進(jìn)行 SPI 控制。專用的水平和垂直極化負(fù)載引腳還可以同步同一陣列中的所有器件。有一個水平和垂直極化發(fā)射和接收模式控制引腳(TRXV 和 TRXH),用于在發(fā)射和接收模式之間快速切換。

ADMV4821采用緊湊的熱增強(qiáng)型 10 mm × 10 mm、符合 RoHs 標(biāo)準(zhǔn)的基板柵格陣列 (LGA) 封裝。ADMV4821 可在 ?40°C 至 +95°C 外殼溫度范圍內(nèi)工作。這種 LGA 封裝允許用戶從封裝的頂部對 ADMV4821 進(jìn)行散熱,以實現(xiàn)最高效的散熱,并允許將天線靈活地放置在印刷電路板 (PCB) 的另一側(cè)。

在數(shù)據(jù)資料的整個數(shù)字中,Tx 表示發(fā)射(或發(fā)射器),Rx 表示接收(或接收器)。

應(yīng)用

- 5G 應(yīng)用

- 寬帶通信

- 測試和測量

- 航空航天和國防

特性

- RF 頻率范圍:24 GHz 至 29.5 GHz,將 n257、n258 和 n261 頻段集成在一個空間內(nèi)

- 16 個可選的 TX 通道

- 16 個可選的 RX 通道

- 水平和垂直極化

- 匹配的 50? 單端 RF 輸入和輸出

- 通過高分辨率矢量調(diào)制器實現(xiàn)相位控制

- 通過高分辨率 DGA 實現(xiàn)幅度控制

- 溫度補(bǔ)償

- 通過存儲器存儲 TX 和 RX 波束位置

- 工作溫度高達(dá) 95°C

- 符合 3GPP 規(guī)范

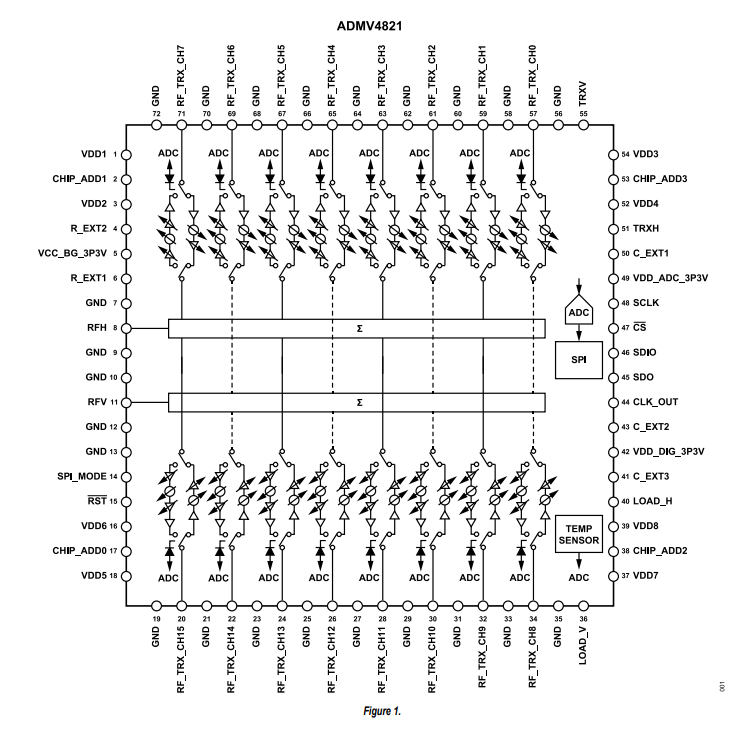

功能框圖

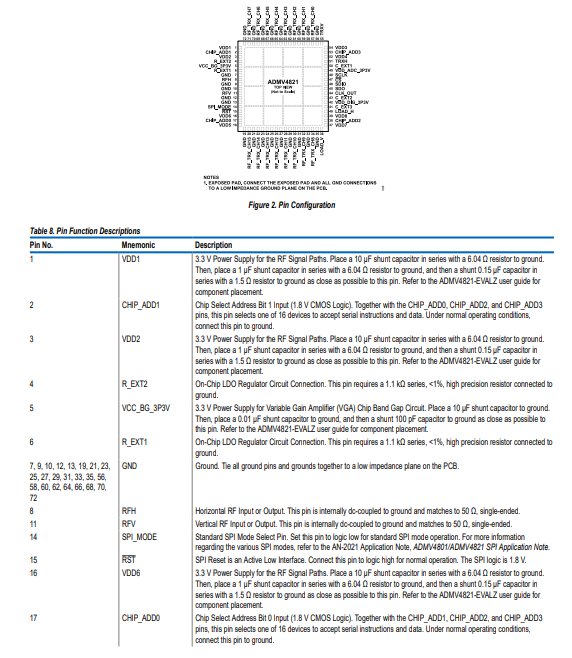

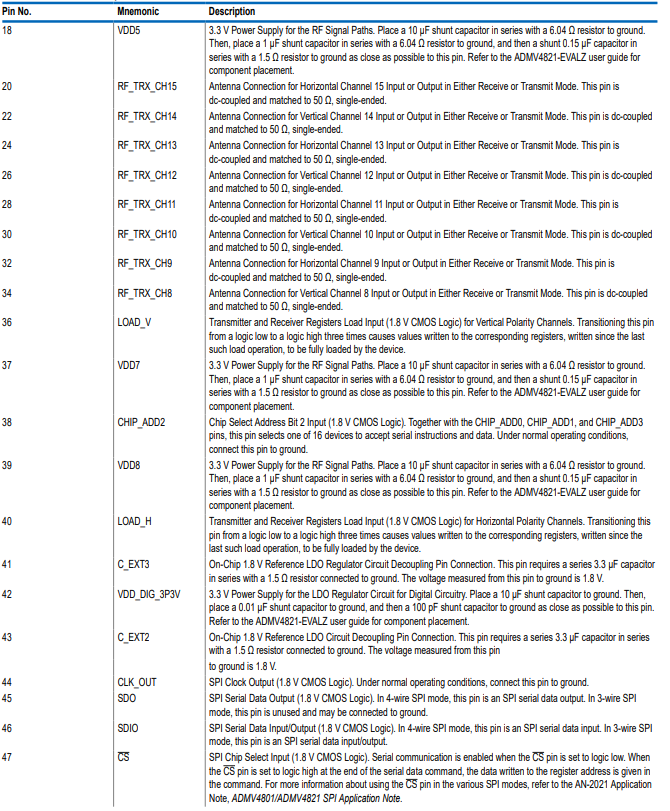

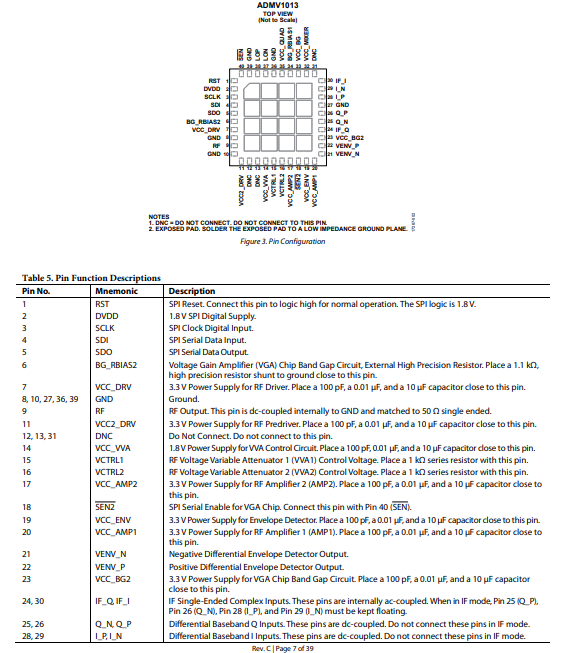

引腳配置描述

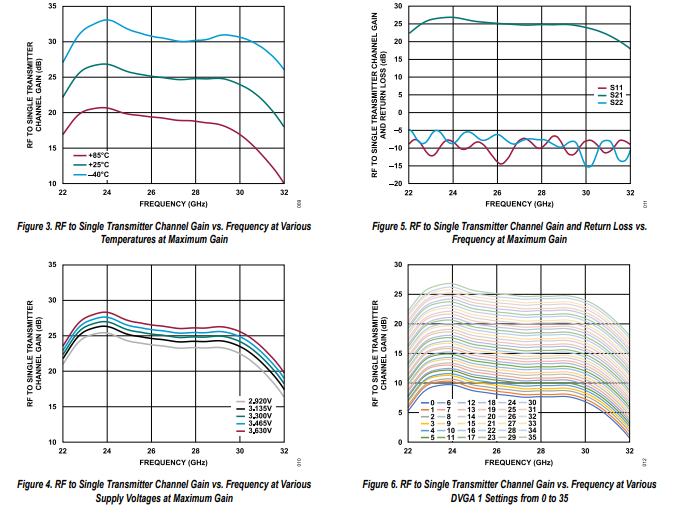

典型性能特征

應(yīng)用信息

AN - 2021應(yīng)用筆記《ADMV4801/ADMV4821 SPI應(yīng)用筆記》詳細(xì)介紹了通過SPI進(jìn)行增益和相位控制的相關(guān)信息,以及“工作原理”部分所述的所有其他功能。本應(yīng)用筆記包含SPI編程示例,這是初始化和加載所有必要寄存器以實現(xiàn)系統(tǒng)級性能的推薦方法。

為ADMV4821供電

ADMV4821只有一個電源域,電壓為3.3V。片上電壓調(diào)節(jié)器為ADMV4821內(nèi)部的所有電路生成所需的1.8V電源。所有屬于同一電源域的電源引腳可連接到單個電源電壓,以確保在ADMV4821電源引腳附近集成了適當(dāng)?shù)娜ヱ铍娙荩鏏DMV4821 - EVALZ用戶指南所示。

散熱片選擇

頂部散熱片和底部散熱片都可安裝到該器件上,以實現(xiàn)高效散熱。

底部散熱片要求在器件下方的電路板底層有大面積的裸露銅箔區(qū)域。

對于頂部散熱片,其尺寸必須與器件一致。尺寸過小的散熱片會導(dǎo)致散熱效率低下。需要使用導(dǎo)熱界面材料(TIM)將頂部散熱片連接到器件上。TIM會填充器件與散熱片之間的間隙,改善器件與散熱片之間的熱接觸。通常建議使用0.5毫米厚的TIM,以實現(xiàn)最佳的熱傳遞和器件性能。

向器件安裝散熱片的最大作用力在表6中有規(guī)定。器件下方的電路板必須得到充分支撐,以防止電路板彎曲。作用力必須垂直于器件,使壓力均勻分布在器件頂部。

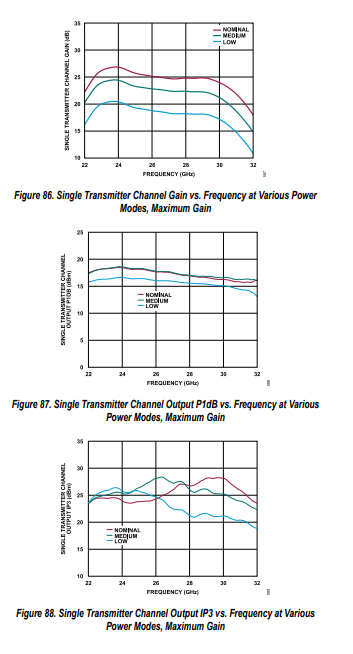

不同功率模式下的性能

發(fā)射模式的標(biāo)稱、中等和低功率模式數(shù)據(jù)

圖86至圖90展示了使用“不同功率模式的偏置控制”部分所述偏置條件時,各參數(shù)的性能表現(xiàn)。

-

SiGe

+關(guān)注

關(guān)注

0文章

99瀏覽量

23896 -

波束

+關(guān)注

關(guān)注

0文章

58瀏覽量

15926 -

5G

+關(guān)注

關(guān)注

1360文章

48728瀏覽量

570180

發(fā)布評論請先 登錄

數(shù)字波束形成相控陣中射頻電子的物理尺寸分配

基于FPGA器件和LVDS技術(shù)設(shè)計的高速實時波束形成器

如何去設(shè)計高速實時波束形成器系統(tǒng)?

UG-1283:評估ADAR1000 8 GHz至16 GHz、4通道、X波段和Ku波段波束形成器

ADMV1014:24 GHz至44 GHz,寬帶,微波下變頻器數(shù)據(jù)表

ADMV1012:17.5 GHz至24 GHz,GaAs,MMIC,I/Q下變頻器數(shù)據(jù)表

ADMV1128A: 24 GHz to 29.5 GHz, 5G, Microwave Upconverter and Downconverter Data Sheet ADMV1128A: 24 GHz to 29.5 GHz, 5G, Microwave Upconvert

ADMV1013S 24 GHz 至 44 GHz、寬帶、微波上變頻器技術(shù)手冊

ADMV1013 24GHz至44GHz、寬帶微波上變頻器技術(shù)手冊

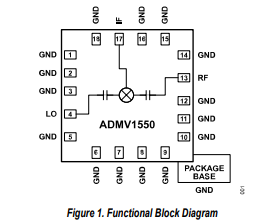

ADMV1550 15GHz至65GHz,GaAs,MMIC,雙平衡混頻器技術(shù)手冊

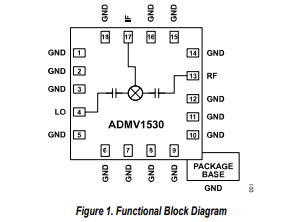

ADMV1530 5GHz至30GHz、GaAs、MMIC、雙平衡混頻器技術(shù)手冊

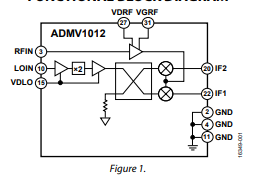

ADMV1012 17.5GHz至24GHz、GaAs、MMIC、I/Q下變頻器技術(shù)手冊

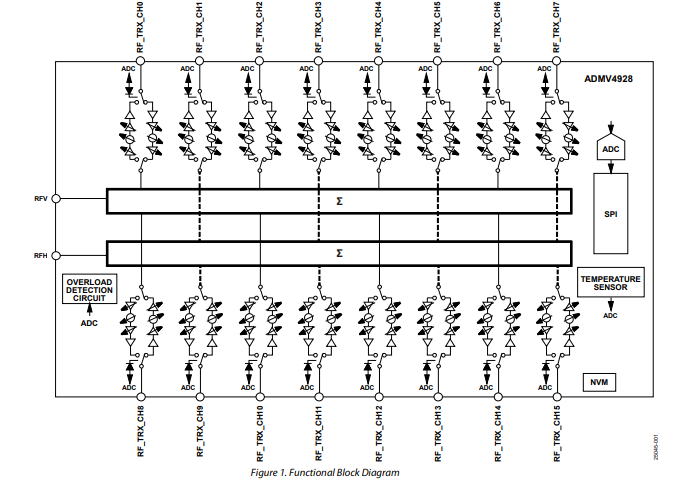

ADMV4928 37.0 GHz至43.5 GHz發(fā)射/接收雙極化波束形成器技術(shù)手冊

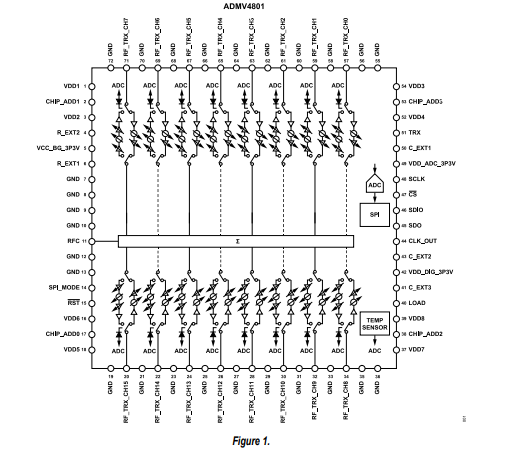

ADMV4821 24至29.5GHz TX/RX 雙極化波束形成器技術(shù)手冊

ADMV4821 24至29.5GHz TX/RX 雙極化波束形成器技術(shù)手冊

評論