在半導體技術的浩瀚星空中,每一次技術的突破都如同璀璨的星辰,照亮著人類科技進步的道路。近年來,隨著計算和人工智能應用的快速發展,對高性能、低功耗電子產品的需求日益增長,這驅使著科研人員不斷探索新的晶體管技術。加州大學圣巴巴拉分校的研究人員在這一領域邁出了重要一步,他們利用二維(2D)半導體技術,成功研發出新型三維(3D)晶體管,為半導體技術的發展開啟了新的篇章。

一、技術突破的背景與意義

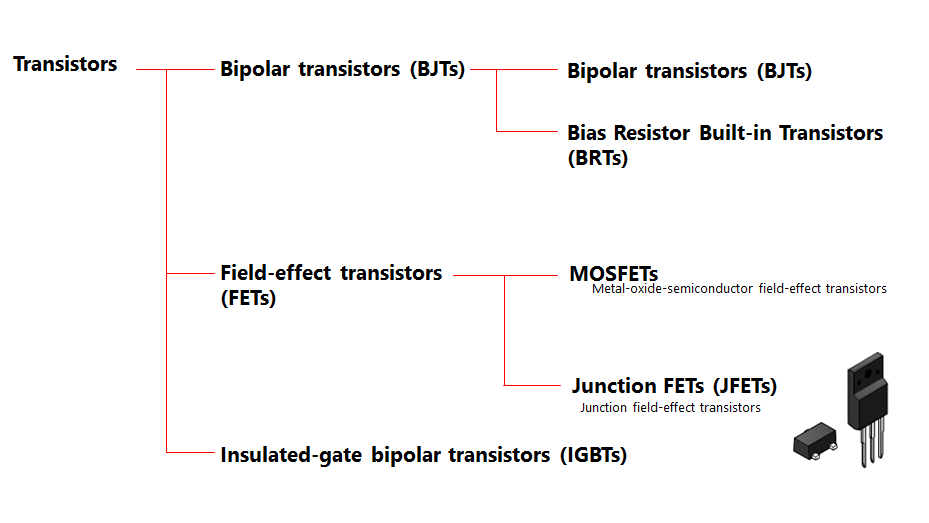

晶體管作為現代電子產品的基本元件,其性能的提升對于整個電子行業的進步至關重要。為了提高現有設備的性能并推動新技術的進步,科研人員一直致力于將晶體管小型化,以便更密集地封裝它們,并在相同尺寸的芯片上實現更多操作。事實上,微型化領域的一些重要進步已經促成了應變硅和高k/金屬柵極場效應晶體管(FET)的設計和開發,這些晶體管解決了尺寸縮小難題并提高了性能。

然而,就主流硅技術而言,晶體管只能縮小到一定尺寸,否則就會達到性能極限,尤其是在能效方面。這些限制被稱為“短溝道效應”,表現為亞閾值漏電流和開關不良,這使得在保持低功耗的同時縮小這些晶體管的尺寸變得困難。十多年前,隨著Fin-FET(鰭式場效應晶體管)的引入,許多限制都得到了克服。Fin-FET是一種3D架構,將“柵極”包裹在從晶體管源極到漏極的通道周圍,從而減輕了短通道效應,同時縮小了占位面積。然而,即使對于最先進的Fin-FET來說,將晶體管縮小到10納米以下通道長度,同時保持低功耗和良好的性能,也越來越具有挑戰性。

加州大學圣巴巴拉分校的研究人員正是在這一背景下,通過利用2D半導體技術,成功研發出新型3D晶體管,這一突破代表著朝著下一代晶體管技術邁出了重要一步。這種技術能夠支持計算和人工智能應用的快速發展,為性能提升、晶體管可擴展性和能源效率開辟了新的可能性。

二、新型3D晶體管的技術原理與實現

加州大學圣巴巴拉分校的研究人員將原子厚度的2D半導體集成到3D架構中,研發出新型3D晶體管。他們將這些3D柵極環繞(GAA)結構晶體管縮寫為NXFET,其中N=納米,X=片、叉或板,代表通道堆疊的拓撲結構。他們的研究確定了如何使用2D半導體獨特地設計此類晶體管。

具體而言,研究中引入的納米板FET架構被證明可以最大限度地發揮原子級厚度的2D材料(如二硫化鎢(WS?))的獨特性能。這種新穎的架構利用了2D層的橫向堆疊,類似于“板堆”,將集成密度提高了十倍,并具有等性能指標。通過利用2D材料獨特的物理和量子力學特性,研究人員克服了許多與用硅設計的傳統3D晶體管相關的限制。他們的模擬表明,納米板晶體管在能源效率和性能方面實現了顯著的改進,通道長度縮小到5nm以下。

為了評估其設計的性能,研究團隊利用最先進的模擬工具(包括QTX,一種基于非平衡格林函數框架的量子傳輸工具)。這種方法使他們能夠模擬關鍵因素,如能帶非拋物線性、有限帶寬、接觸電阻和載流子遷移率,這些測量值描述了材料與穿過它的電荷載流子(如電子)之間的關系。為了提供準確的輸入參數,研究人員還使用了密度泛函理論,該理論部分由已故的Walter Kohn開發,他是加州大學圣塔芭芭拉分校的物理學家,因“開發密度泛函理論”而獲得1998年諾貝爾化學獎。

三、新型3D晶體管的優勢與應用前景

新型3D晶體管在多個關鍵指標方面表現出色,優于硅基3D-FET。具體來說,基于2D半導體的3D-FET在驅動電流(操作器件的電流量)和能量延遲積(切換所需的能量)等方面具有顯著優勢。2D材料的薄度可最大限度地降低器件電容,從而降低功耗,而其垂直堆疊則支持在制造過程中實現更好的縮放。

這一技術的突破不僅展示了二維材料的潛力,還為將其集成到三維晶體管設計中提供了詳細的藍圖。這是半導體行業在尋求延續摩爾定律的過程中向前邁出的關鍵一步。摩爾定律指出,集成電路上的晶體管數量大約每兩年翻一番,這一規律已經指導了半導體行業幾十年的快速發展。然而,隨著晶體管尺寸的不斷縮小,傳統硅基晶體管的性能提升和功耗降低變得越來越困難。新型3D晶體管的出現,為半導體行業的持續發展提供了新的動力。

從應用前景來看,新型3D晶體管的影響超出了傳統計算的范圍。在邊緣AI、柔性電子和物聯網超低功耗設備方面都有潛在應用。隨著人工智能和物聯網技術的快速發展,對高性能、低功耗電子產品的需求日益增長。新型3D晶體管的出現,有望滿足這些新興應用的需求,推動相關技術的進一步發展。

四、行業內的其他技術進展與競爭態勢

在半導體技術領域,除了加州大學圣巴巴拉分校的研究人員外,其他科研機構和企業也在積極探索新型晶體管技術。例如,在2023年IEEE國際電子器件會議(IEDM2023)上,臺積電、三星和英特爾各自展示了在下一代晶體管結構領域的尖端技術。其中,被稱為“互補場效應晶體管(CFET)”的晶體管結構被視為1nm以下制程的關鍵要素,是繼FinFET和GAA之后的新一代晶體管技術。

CFET與此前晶體管結構的最大不同之處在于采用晶體管垂直堆疊結構,這或將開啟三維晶體管結構新紀元。業內人士介紹,在FinFET和GAA架構出現以前,芯片晶體管結構采用的是平面MOSFET。然而,當溝道長度小于一定值時,柵極對于溝道的控制能力會下降,出現短溝道效應。為了解決這個問題,業界提出了FinFET和GAA兩種新型晶體管結構。隨著摩爾定律的不斷發展,芯片制程也愈發接近物理極限,為了能夠進一步增加單位面積上的器件數量,業內開始嘗試將原本的立體結構晶體管再進行堆疊,提出了采用垂直堆疊結構的CFET。

臺積電、三星和英特爾都在密切關注CFET相關技術。臺積電指出,CFET晶體管現已在臺積電實驗室中進行性能、效率和密度測試,并已經實現了48nm的柵極間距。三星將CFET晶體管結構稱為3DSFET,目前的柵極間距為45/48nm,并在技術創新方面實現了對堆疊式pFET和nFET器件的源極和漏極進行有效的電氣隔離。英特爾則展示了將CFET晶體管結構與背面供電技術相結合的新技術,并利用該技術實現了60nm的柵極間距。

盡管CFET結構具有廣闊的應用前景,但目前仍面臨多層堆疊帶來的大量技術挑戰。例如,多層堆疊熱退火問題是CFET面臨的最大挑戰之一。半導體材料在晶體生長和制造過程中會出現缺陷、雜質、位錯等結構性缺陷,導致晶格不完整。通過熱退火處理可以使材料得到修復,但在堆疊結構中,每堆疊一層就要再多進行一次熱退火,增加了工藝難度和成本。

五、未來展望與挑戰

對于加州大學圣巴巴拉分校的研究人員來說,新型3D晶體管的成功研發只是一個開始。著眼于未來的發展,他們計劃深化與行業合作伙伴的合作,以加速這些技術的采用。同時,他們還計劃通過納入缺陷散射和自熱等其他現實因素來改進模型,以支持實驗驗證。

此外,新型3D晶體管技術在實際應用中還面臨一些挑戰。例如,如何將這種技術大規模應用于實際生產中,如何降低生產成本,如何進一步提高晶體管的性能和穩定性等。這些問題都需要科研人員和企業界共同努力去解決。

從整個半導體行業來看,隨著技術的不斷進步和競爭的加劇,新型晶體管技術的研發和應用將成為未來發展的重要方向。除了加州大學圣巴巴拉分校和臺積電、三星、英特爾等領先企業外,其他科研機構和企業也在積極投入資源進行相關研究。這種競爭態勢將推動半導體技術的不斷發展和創新。

六、結語

下一代3D晶體管技術的研發和應用標志著半導體行業在尋求延續摩爾定律的過程中邁出了重要一步。加州大學圣巴巴拉分校的研究人員通過利用2D半導體技術成功研發出新型3D晶體管,為半導體技術的發展開啟了新的篇章。這一技術的突破不僅展示了二維材料的潛力,還為將其集成到三維晶體管設計中提供了詳細的藍圖。盡管在實際應用中還面臨一些挑戰和競爭態勢,但隨著技術的不斷進步和創新的持續推動,相信新型3D晶體管技術將在未來發揮越來越重要的作用,推動半導體行業和相關技術的持續發展。

隨著人工智能、物聯網等新興技術的快速發展,對高性能、低功耗電子產品的需求日益增長。新型3D晶體管技術有望滿足這些新興應用的需求,推動相關技術的進一步發展。同時,這一技術的突破也將為半導體行業帶來新的商業機會和市場前景。相信在未來的發展中,新型3D晶體管技術將成為半導體行業的重要驅動力之一。

-

電子產品

+關注

關注

6文章

1204瀏覽量

59130 -

半導體封裝

+關注

關注

4文章

289瀏覽量

14268 -

3D晶體管

+關注

關注

0文章

25瀏覽量

17534

發布評論請先 登錄

中國下一代半導體研究超越美國

鎧俠與閃迪發布下一代3D閃存技術,實現4.8Gb/s NAND接口速度

互補場效應晶體管的結構和作用

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

晶體管基本原理與工作機制 如何選擇適合的晶體管型號

意法半導體下一代汽車微控制器的戰略部署

麻省理工學院研發全新納米級3D晶體管,突破性能極限

下一代芯片技術,新突破

下一代3D晶體管技術突破,半導體行業迎新曙光!

下一代3D晶體管技術突破,半導體行業迎新曙光!

評論