文章來源:學(xué)習(xí)那些事

原文作者:趙先生

本文介紹了影響集成電路可靠性的Cu/low-k互連結(jié)構(gòu)中的電遷移問題。

概述

在集成電路尺寸朝著深亞微米級不斷微縮的進(jìn)程中,金屬互連引發(fā)的諸如RC延遲(RC delay)、信號串?dāng)_以及功耗等一系列問題,給芯片性能的提升帶來了極為嚴(yán)峻的挑戰(zhàn)。圖1清晰呈現(xiàn)出柵延遲和互連延遲與工藝節(jié)點之間的關(guān)聯(lián)情況。為了成功攻克這些難題,推動集成電路持續(xù)向前發(fā)展,業(yè)界主要從以下三個關(guān)鍵方面展開了改進(jìn)工作:其一,選用電阻率更低的金屬材料,以銅替代鋁;其二,采用低介電常數(shù)(low-k)材料來替換二氧化硅;其三,增加布線層數(shù),從0.13um工藝時的7至8層,逐步增加到如今的十幾層,例如Intel的10nm工藝便包含13個互連層。

圖1:柵延遲和互連延遲與工藝節(jié)點的關(guān)系

銅互連

互連技術(shù)在初始階段所采用的金屬材料為鋁。然而,當(dāng)工藝發(fā)展至0.13um及其以下尺度時,鋁逐漸被銅所取代。這一替換使得RC延遲得以顯著降低,大約減小了40%。當(dāng)工藝節(jié)點進(jìn)入到28nm及以下時,通常會添加少量的Mn元素,以此來提升銅的EM(電質(zhì)遷移性能)。與鋁相比,銅具備諸多顯著優(yōu)勢:其一,銅的電阻率較低,其電阻率數(shù)值為1.67uΩ·cm,而鋁的電阻率為2.66uΩ·cm;其二,銅的抗電遷移能力較強(qiáng),銅發(fā)生電遷移的電流密度上限能夠達(dá)到5.5X10?A/cm2,而鋁在電流密度僅達(dá)到2.5X10?A/cm2時就會出現(xiàn)遷移現(xiàn)象;其三,銅具有熔點較高的特性,其散熱能力良好,并且載流能力遠(yuǎn)遠(yuǎn)強(qiáng)于鋁。不過,在銅互連工藝的發(fā)展歷程中,也遭遇了兩大棘手的挑戰(zhàn):其一是銅污染問題;其二是沉積問題。

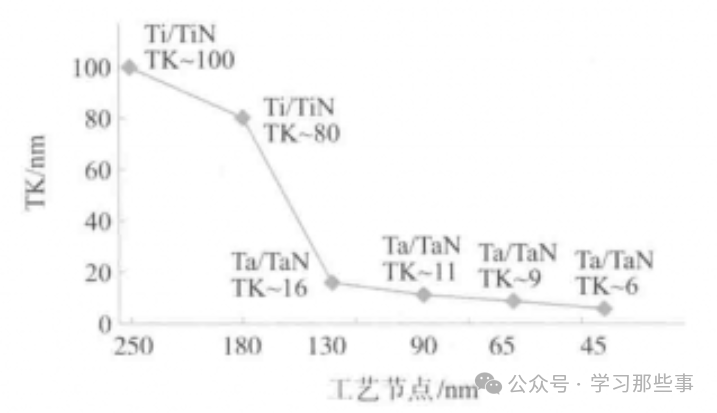

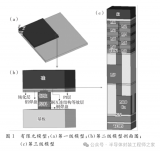

所謂銅污染,指的是銅原子(離子)在介電質(zhì)層中具有較強(qiáng)的擴(kuò)散傾向,這種擴(kuò)散會對介電質(zhì)層造成污染,進(jìn)而導(dǎo)致銅互連線之間出現(xiàn)電壓衰減的情況,嚴(yán)重時甚至?xí)l(fā)互連層間的電壓擊穿現(xiàn)象。為有效應(yīng)對這一問題,人們研發(fā)出了阻擋層工藝,通過采用氮化鉭/鉭(TaN/Ta)結(jié)構(gòu)對銅進(jìn)行包裹,以此來阻擋銅原子(離子)的擴(kuò)散。在這一結(jié)構(gòu)中,Ta對銅能夠起到良好的黏附作用,同時具備出色的定型效果;而TaN不僅對銅有著良好的阻擋能力,而且與介電層之間的黏附性也十分優(yōu)良。圖2展示的便是銅互連的示意圖。由此可見,銅互連的電阻值實際上是由銅本身的電阻以及阻擋層TaN/Ta的電阻共同構(gòu)成。由于銅的電阻率為1.67uΩ·cm,鉭的電阻率為30uΩ·cm,氮化鉭的電阻率為210μΩ·cm,所以互連線的阻值大致可表示為R≈R銅+R阻擋層 ,圖2同時給出了銅互連電阻的等效圖。倘若想要降低銅互連的電阻,可行的方法主要有兩種:一種是降低金屬線本身的電阻;另一種則是減小阻擋層的電阻。而最為直接的做法便是減小TaN/Ta阻擋層的厚度。從圖3中可以清晰地看到不同工藝節(jié)點下阻擋層厚度的變化情況。隨著工藝的不斷發(fā)展,阻擋層厚度持續(xù)變薄,這一變化導(dǎo)致臺階覆蓋性逐漸變差,同時對銅的黏附力也會相應(yīng)地減弱。此外,隨著特征尺寸不斷微縮,深寬比逐漸增大,在進(jìn)行溝槽和通孔的填充過程中,極易產(chǎn)生空洞,這些空洞的出現(xiàn)會對器件的可靠性造成嚴(yán)重影響。基于此,目前業(yè)界主要借助一些新工藝(如原子層沉積)來改善填充效果。然而,需要注意的是,阻擋層厚度不能無限制地減薄,它必須保持一定的厚度,才能夠充分發(fā)揮出良好的阻擋作用。因此,在10nm及以下工藝節(jié)點,業(yè)界開始采用新材料鈷作為阻擋層材料。

圖2:銅互連示意圖及電阻等效圖

圖3:不同工藝節(jié)點下阻擋層厚度的變化

在以往鋁的沉積過程中,是通過鋁與氯氣反應(yīng)所產(chǎn)生的氯化物來實現(xiàn)對鋁互連線的刻蝕,從而獲得期望的圖形。但銅的氟化物和氯化物在低溫環(huán)境下都難以揮發(fā),這就使得傳統(tǒng)的干法刻蝕工藝無法應(yīng)用于銅的刻蝕。為解決這一難題,人們發(fā)明了大馬士革工藝和化學(xué)機(jī)械平坦化拋光研磨工藝(CMP)。具體操作方法為:首先沉積介質(zhì)層,接著刻蝕出銅互連線的圖案,隨后進(jìn)行銅的填充,最后通過CMP工藝將表面磨平。大馬士革工藝一般可分為單大馬士革工藝和雙大馬士革工藝。其中,單大馬士革工藝相對較為簡單,就是先對介質(zhì)層進(jìn)行刻蝕,然后進(jìn)行金屬填充,例如后段互連中的第一層金屬(M1)就采用這種方式;而雙大馬士革工藝則需要刻蝕出通孔(via)和溝槽(trench),之后再進(jìn)行金屬填充,M1之后的金屬層大多采用該方式。在雙大馬士革工藝發(fā)展的初期,又可細(xì)分為先通孔(via first)和先溝槽(trench first)兩種方式。如圖4(a)所示為先通孔方式,即先進(jìn)行通孔的刻蝕,然后再進(jìn)行溝槽刻蝕。這種方法能夠較好地對通孔的尺寸進(jìn)行控制,但其存在一些缺點:①溝槽的深度控制難度較大;②通孔中填充介質(zhì)的高度需要進(jìn)行精密控制,否則會導(dǎo)致上部介質(zhì)形貌變差;③整個過程需要進(jìn)行兩次刻蝕動作,容易形成等離子體損傷。如圖4(b)所示為先溝槽方式,即先進(jìn)行溝槽刻蝕,之后再進(jìn)行通孔刻蝕。這種方法的制程相對較為簡單,但也存在一些不足之處:①對光刻工藝的套準(zhǔn)精度要求較高;②通孔底部尺寸很難控制;③溝槽的深度控制難度比較大;④同樣需要進(jìn)行兩次刻蝕,容易形成等離子體損傷。

圖4:雙大馬士革工藝的兩種流程

隨著器件尺寸的不斷微縮,大馬士革工藝面臨著如何精準(zhǔn)控制溝槽尺寸以及降低介質(zhì)層損傷的嚴(yán)峻挑戰(zhàn)。為解決這一問題,業(yè)界開發(fā)出了如圖5所示的金屬硬掩模層一體化刻蝕工藝(hard mask all-in-one)。該工藝的具體操作方法是:首先將溝槽圖案轉(zhuǎn)移到硬掩模上,然后通過光刻定義出通孔形貌,并通過一體化刻蝕形成通孔和溝槽,最后進(jìn)行金屬填充和CMP平坦化處理。金屬硬掩模層一體化刻蝕工藝具有以下顯著優(yōu)點:①由于只需將溝槽圖案轉(zhuǎn)移到硬掩模上,無需在刻蝕介質(zhì)層中刻出溝槽,所以使用的光刻膠(PR)厚度較薄,這使得光刻分辨率能夠得到顯著提高;②相較于光刻膠,硬掩模與介質(zhì)層之間的選擇比更高,能夠更為有效地控制關(guān)鍵尺寸,使刻蝕形貌更加理想;③采用一體化刻蝕方式,能夠有效地避免等離子體損傷。

圖5:金屬掩膜層一體化刻蝕工藝流程示意圖

Low-k材料

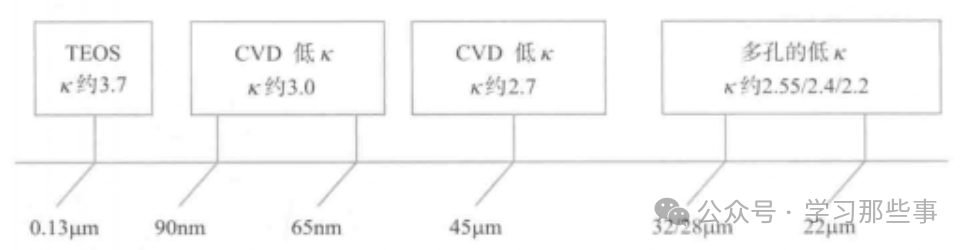

在銅互連技術(shù)體系里,互連層之間的電容模型呈現(xiàn)于圖6。鑒于電容大小與介電常數(shù)成正相關(guān)關(guān)系,業(yè)界為減小互連層間電容,進(jìn)而改善RC延遲,采用了介電常數(shù)(κ值)低于傳統(tǒng)二氧化硅的low-k材料。圖7展示了不同工藝節(jié)點下互連介質(zhì)層的κ值變化情況。

圖6:互連線寄生電容示意圖

圖7:不同工藝節(jié)點的k值

當(dāng)下,low-k材料的制備方式主要涵蓋三種:其一,在材料中摻入氟、碳、氫等強(qiáng)電負(fù)性元素,以此降低材料極性,進(jìn)而減小材料的κ值,像氟硅酸鹽玻璃(FSG)、摻碳?xì)溲趸?SiCOH)等較為常見,它們在0.13um至45nm工藝中得到廣泛應(yīng)用;其二,借助多孔技術(shù),降低材料的分子密度來實現(xiàn)κ值降低,例如多孔SiO?、多孔SiCOH等;其三,運用氣隙(airgap)技術(shù),將超低κ值的空氣隙嵌入互連介質(zhì)層,這同樣能顯著降低介電常數(shù)。在32/28nm及以下工藝中,由于對降低RC延遲所需的κ值要求更低,故而常運用多孔和氣隙技術(shù)來制備超low-k介質(zhì)層 。

Cu/low-k互連的電遷移問題

伴隨大規(guī)模集成電路持續(xù)發(fā)展,特征尺寸不斷縮小,金屬導(dǎo)線所通入的電流密度急劇上升。與此同時,芯片集成度提高,單位面積功耗增大,致使Cu/low-k互連結(jié)構(gòu)中的電遷移問題,已成為影響集成電路可靠性的關(guān)鍵因素之一。在金屬導(dǎo)線內(nèi),沿電場反方向運動的電子與金屬離子發(fā)生動量交換,致使金屬離子順著電子流方向移動,這種現(xiàn)象被稱作電遷移,它可能引發(fā)金屬線開路或斷路。盡管銅材料自身抗電遷移能力強(qiáng)于鋁,但雙大馬士革工藝使得銅的電遷移問題變得復(fù)雜。其中,通孔工藝、阻擋層質(zhì)量以及銅表面處理等諸多方面,均會對銅互連電遷移產(chǎn)生影響。

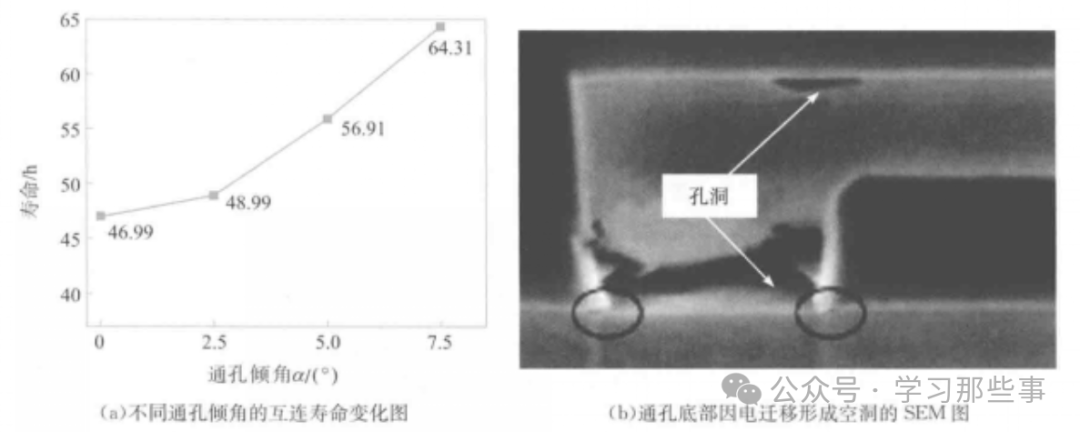

對于銅互連結(jié)構(gòu)而言,通孔因深寬比高、臺階覆蓋性欠佳、內(nèi)部電流密度大以及應(yīng)力集中等因素,相比溝槽互連線,更易出現(xiàn)電遷移失效情況。其中,通孔的傾斜角和通孔底部的形貌是兩大主要影響因素。具有一定傾斜角度的通孔結(jié)構(gòu),相較于垂直結(jié)構(gòu),更便于后續(xù)阻擋層和金屬銅的填充,能使臺階及側(cè)壁覆蓋性更佳,從而提升互連線的可靠性。圖8(a)所示為不同通孔傾角下互連壽命的變化情況。通孔底部是整個通孔工藝中最為薄弱之處,也是最易失效的部位。通孔底部刻蝕形貌的均勻程度、阻擋層TaN是否實現(xiàn)完全反濺射,以及后續(xù)銅填充的形貌等,都會對電遷移產(chǎn)生重大影響。圖8(b)展示的是通孔底部因電遷移形成的空洞。其中,阻擋層TaN的完全反濺射(re-sputter)是工藝難點。該過程通過轟擊通孔底部的阻擋層TaN,使底部TaN濺射到側(cè)壁上,以達(dá)到增加側(cè)壁阻擋層厚度、減薄底部厚度的目的。由于阻擋層電阻率遠(yuǎn)大于銅,若反濺射不完全,會導(dǎo)致通孔底部接觸電阻增大,電流流經(jīng)此處時,因電阻不均勻致使局部電流密度不一致,進(jìn)而產(chǎn)生空洞,引發(fā)電遷移失效。阻擋層肩負(fù)著阻止銅擴(kuò)散,以及確保介質(zhì)層與銅界面具備良好黏附性的雙重職責(zé)。良好的黏附性能減緩沿銅阻擋層界面的銅擴(kuò)散速度。

圖8:不同通孔傾角的互連壽命變化圖及電遷移所形成的空洞的SEM圖

銅互連的另一個電遷移失效高發(fā)區(qū)域是銅的表面,因為沿表面的銅擴(kuò)散速度快于沿晶粒間界的擴(kuò)散速度。為解決這一問題,業(yè)界在銅CMP之后,會在銅線上沉積一層覆蓋層。該覆蓋層可有效阻止銅擴(kuò)散,增強(qiáng)抗電遷移能力,且兩者間黏附性越強(qiáng),效果越顯著。對銅表面進(jìn)行處理是提升銅線與覆蓋層黏附性的有效手段,一般采用H等離子體對銅表面進(jìn)行處理,以此改善銅與覆蓋層的黏附性。

-

芯片

+關(guān)注

關(guān)注

459文章

52481瀏覽量

440589 -

集成電路

+關(guān)注

關(guān)注

5424文章

12042瀏覽量

368376 -

工藝

+關(guān)注

關(guān)注

4文章

681瀏覽量

29437 -

互連

+關(guān)注

關(guān)注

0文章

24瀏覽量

10479

原文標(biāo)題:Cu/low-k互連的電遷移問題

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Low-K材料在芯片中的作用

AL-CU互連導(dǎo)線側(cè)壁孔洞形成機(jī)理及改進(jìn)方法

直接互連結(jié)構(gòu)在數(shù)據(jù)交換中的應(yīng)用分析

Scratch Testing of Low-k Diele

什么是直接互連結(jié)構(gòu)(direct interconnecti

直流和脈沖電鍍Cu互連線的性能比較

電子封裝微互連中的電遷移

多核密碼處理器中的片上網(wǎng)絡(luò)互連結(jié)構(gòu)研究

可延展電子金屬導(dǎo)線通用互連結(jié)構(gòu)研究

高速BGA封裝與PCB差分互連結(jié)構(gòu)進(jìn)行設(shè)計與優(yōu)化

高速BGA封裝與PCB差分互連結(jié)構(gòu)設(shè)計

Aston? 過程質(zhì)譜提高 low-k 電介質(zhì)沉積的吞吐量

一文了解晶圓級封裝中的垂直互連結(jié)構(gòu)

優(yōu)化銅互連結(jié)構(gòu)的熱應(yīng)力分析與介電材料選擇

Cu/low-k互連結(jié)構(gòu)中的電遷移問題

Cu/low-k互連結(jié)構(gòu)中的電遷移問題

評論