隨著物聯(lián)網(wǎng)時(shí)代來(lái)臨,全球終端電子產(chǎn)品漸漸走向多功能整合及低功耗設(shè)計(jì),因而使得可將多顆裸晶整合在單一封裝中的SIP技術(shù)日益受到關(guān)注。除了既有的封測(cè)大廠積極擴(kuò)大SIP制造產(chǎn)能外,晶圓代工業(yè)者與IC基板廠也競(jìng)相投入此一技術(shù),以滿足市場(chǎng)需求。

早前,蘋果發(fā)布了最新的apple watch手表,里面用到SIP封裝芯片,從尺寸和性能上為新手表增色不少。而芯片發(fā)展從一味追求功耗下降及性能提升(摩爾定律),轉(zhuǎn)向更加務(wù)實(shí)的滿足市場(chǎng)的需求(超越摩爾定律)。

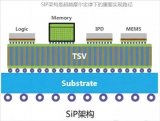

根據(jù)國(guó)際半導(dǎo)體路線組織(ITRS)的定義:SIP為將多個(gè)具有不同功能的有源電子元件與可選無(wú)源器件,以及諸如MEMS或者光學(xué)器件等其他器件優(yōu)先組裝到一起,實(shí)現(xiàn)一定功能的單個(gè)標(biāo)準(zhǔn)封裝件,形成一個(gè)系統(tǒng)或者子系統(tǒng)。

SIP定義

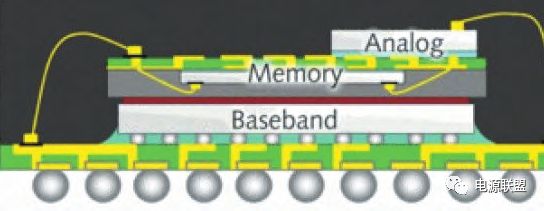

從架構(gòu)上來(lái)講, SIP 是將多種功能芯片,包括處理器、存儲(chǔ)器等功能芯片集成在一個(gè)封裝內(nèi),從而實(shí)現(xiàn)一個(gè)基本完整的功能。

SOC定義

將原本不同功能的 IC,整合在一顆芯片中。藉由這個(gè)方法,不單可以縮小體積,還可以縮小不同 IC 間的距離,提升芯片的計(jì)算速度。SOC稱為系統(tǒng)級(jí)芯片,也有稱片上系統(tǒng),意指它是一個(gè)產(chǎn)品,是一個(gè)有專用目標(biāo)的集成電路,其中包含完整系統(tǒng)并有嵌入軟件的全部?jī)?nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能開(kāi)始,到軟/硬件劃分,并完成設(shè)計(jì)的整個(gè)過(guò)程。

SOC與SIP之比較

自集成電路器件的封裝從單個(gè)組件的開(kāi)發(fā),進(jìn)入到多個(gè)組件的集成后,隨著產(chǎn)品效能的提升以及對(duì)輕薄和低耗需求的帶動(dòng)下,邁向封裝整合的新階段。在此發(fā)展方向的引導(dǎo)下,形成了電子產(chǎn)業(yè)上相關(guān)的兩大新主流:系統(tǒng)單芯片SOC(System on Chip)與系統(tǒng)化封裝SIP(System in a Package)。

SOC與SIP是極為相似,兩者均將一個(gè)包含邏輯組件、內(nèi)存組件,甚至包含被動(dòng)組件的系統(tǒng),整合在一個(gè)單位中。

SOC是從設(shè)計(jì)的角度出發(fā),是將系統(tǒng)所需的組件高度集成到一塊芯片上。

SIP是從封裝的立場(chǎng)出發(fā),對(duì)不同芯片進(jìn)行并排或疊加的封裝方式,將多個(gè)具有不同功能的有源電子元件與可選無(wú)源器件,以及諸如MEMS或者光學(xué)器件等其他器件優(yōu)先組裝到一起,實(shí)現(xiàn)一定功能的單個(gè)標(biāo)準(zhǔn)封裝件。

構(gòu)成SIP技術(shù)的要素是封裝載體與組裝工藝,前者包括PCB、LTCC、Silicon Submount(其本身也可以是一塊IC),后者包括傳統(tǒng)封裝工藝(Wire bond和Flip Chip)和SMT設(shè)備。無(wú)源器件是SIP的一個(gè)重要組成部分,如傳統(tǒng)的電容、電阻、電感等,其中一些可以與載體集成為一體,另一些如精度高、Q值高、數(shù)值高的電感、電容等通過(guò)SMT組裝在載體上。

SIP封裝

從集成度而言,一般情況下,SOC只集成AP之類的邏輯系統(tǒng),而SiP集成了AP+mobile DDR,某種程度上說(shuō)SIP=SOC+DDR,隨著將來(lái)集成度越來(lái)越高,emmc也很有可能會(huì)集成到SIP中。

從封裝發(fā)展的角度來(lái)看,因電子產(chǎn)品在體積、處理速度或電性特性各方面的需求考量下,SOC曾經(jīng)被確立為未來(lái)電子產(chǎn)品設(shè)計(jì)的關(guān)鍵與發(fā)展方向。但隨著近年來(lái)SOC生產(chǎn)成本越來(lái)越高,頻頻遭遇技術(shù)障礙,造成SoC的發(fā)展面臨瓶頸,進(jìn)而使SIP的發(fā)展越來(lái)越被業(yè)界重視。

SIP的封裝形態(tài)

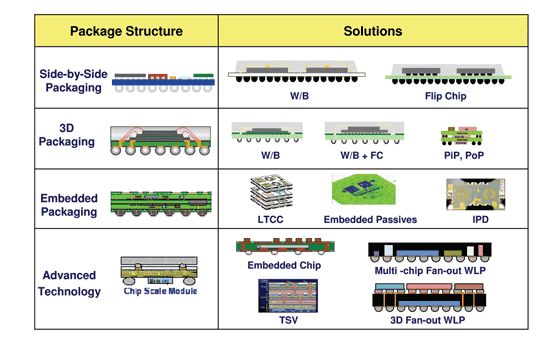

SIP封裝技術(shù)采取多種裸芯片或模塊進(jìn)行排列組裝,若就排列方式進(jìn)行區(qū)分可大體分為平面式2D封裝和3D封裝的結(jié)構(gòu)。相對(duì)于2D封裝,采用堆疊的3D封裝技術(shù)又可以增加使用晶圓或模塊的數(shù)量,從而在垂直方向上增加了可放置晶圓的層數(shù),進(jìn)一步增強(qiáng)SIP技術(shù)的功能整合能力。而內(nèi)部接合技術(shù)可以是單純的線鍵合(Wire Bonding),也可使用覆晶接合(Flip Chip),也可二者混用。

另外,除了2D與3D的封裝結(jié)構(gòu)外,還可以采用多功能性基板整合組件的方式——將不同組件內(nèi)藏于多功能基板中,達(dá)到功能整合的目的。不同的芯片排列方式,與不同的內(nèi)部接合技術(shù)搭配,使SIP的封裝形態(tài)產(chǎn)生多樣化的組合,并可依照客戶或產(chǎn)品的需求加以客制化或彈性生產(chǎn)。

幾種SIP封裝方案

SIP的技術(shù)難點(diǎn)

SIP的主流封裝形式是BGA,但這并不是說(shuō)具備傳統(tǒng)先進(jìn)封裝技術(shù)就掌握了SIP技術(shù)。

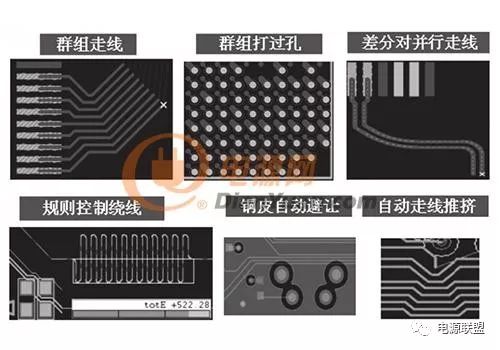

對(duì)于電路設(shè)計(jì)而言,三維芯片封裝將有多個(gè)裸片堆疊,如此復(fù)雜的封裝設(shè)計(jì)將帶來(lái)很多問(wèn)題:比如多芯片集成在一個(gè)封裝內(nèi),芯片如何堆疊起來(lái);再比如復(fù)雜的走線需要多層基板,用傳統(tǒng)的工具很難布通走線;還有走線之間的間距,等長(zhǎng)設(shè)計(jì),差分對(duì)設(shè)計(jì)等問(wèn)題。

此外,隨著模塊復(fù)雜度的增加和工作頻率(時(shí)鐘頻率或載波頻率)的提高,系統(tǒng)設(shè)計(jì)的難度會(huì)不斷增加,設(shè)計(jì)者除具備必要的設(shè)計(jì)經(jīng)驗(yàn)外,系統(tǒng)性能的數(shù)值仿真也是必不可少的設(shè)計(jì)環(huán)節(jié)。

SOC與SIP技術(shù)趨勢(shì)

從集成度而言,一般情況下, SOC 只集成 AP 之類的邏輯系統(tǒng),而 SIP 集成了AP+mobileDDR,某種程度上說(shuō) SIP=SOC+DDR,隨著將來(lái)集成度越來(lái)越高, emmc也很有可能會(huì)集成到 SIP 中。從封裝發(fā)展的角度來(lái)看,因電子產(chǎn)品在體積、處理速度或電性特性各方面的需求考量下, SOC 曾經(jīng)被確立為未來(lái)電子產(chǎn)品設(shè)計(jì)的關(guān)鍵與發(fā)展方向。但隨著近年來(lái) SOC生產(chǎn)成本越來(lái)越高,頻頻遭遇技術(shù)障礙,造成 SOC 的發(fā)展面臨瓶頸,進(jìn)而使 SIP 的發(fā)展越來(lái)越被業(yè)界重視。?

-

SiP

+關(guān)注

關(guān)注

5文章

526瀏覽量

106451 -

soc

+關(guān)注

關(guān)注

38文章

4386瀏覽量

222691

原文標(biāo)題:SoC封裝技術(shù)與SIP封裝技術(shù)之經(jīng)典比較

文章出處:【微信號(hào):Power-union,微信公眾號(hào):電源聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一文讀懂SIP與SOC封裝技術(shù)

Sip技術(shù)是什么?Sip封裝技術(shù)優(yōu)缺點(diǎn)

簡(jiǎn)單介紹SoC與SiP中芯片解密的應(yīng)用

一文看懂SiP封裝技術(shù)

SiP(系統(tǒng)級(jí)封裝)技術(shù)的應(yīng)用與發(fā)展趨勢(shì)

層疊封裝技術(shù)的發(fā)展道路和概念

基于LTCC技術(shù)實(shí)現(xiàn)SIP的優(yōu)勢(shì)和特點(diǎn)討論

SIP封裝有什么優(yōu)點(diǎn)?

SIP技術(shù)封裝外形圖的位置度是如何制定的。

SIP系統(tǒng)封裝技術(shù)淺析

SIP封裝和采用SiP工藝的DFN封裝是什么

關(guān)于HIC、MCM、SIP封裝與SOC的區(qū)別

LGA‐SiP封裝技術(shù)解析

SiP系統(tǒng)級(jí)封裝、SOC芯片和合封芯片主要區(qū)別!合封和sip一樣嗎?

SIP封裝技術(shù):引領(lǐng)電子封裝新革命!

SoC封裝技術(shù)與SIP封裝技術(shù)的區(qū)別

SoC封裝技術(shù)與SIP封裝技術(shù)的區(qū)別

評(píng)論