在集成電路制造工藝升級(jí)的過程中,High-K和FinFET的出現(xiàn)對(duì)摩爾定律的延續(xù)發(fā)生了重要的作用,并一再打破了過去專家對(duì)行業(yè)的預(yù)測(cè)。近年來,隨著工藝的進(jìn)一步演進(jìn),業(yè)界又開始產(chǎn)生了對(duì)晶體管能否繼續(xù)縮進(jìn)產(chǎn)生了疑惑。

在今日開幕的CSTIC2018上,F(xiàn)inFET的發(fā)明者胡正明教授發(fā)表了題為《Will Scaling End?What Then?》的演講,探討集成電路制造的發(fā)展方向。

胡教授表示,在1999年的時(shí)候,業(yè)界的普遍觀點(diǎn)是晶體管微縮將會(huì)在35納米的時(shí)候結(jié)束。

然而,就在同一年,UC Berkeley推出了45納米的FinFET晶體管。得益于新的晶體管構(gòu)造模式,器件的性能測(cè)試參數(shù)獲得了不錯(cuò)的效果。

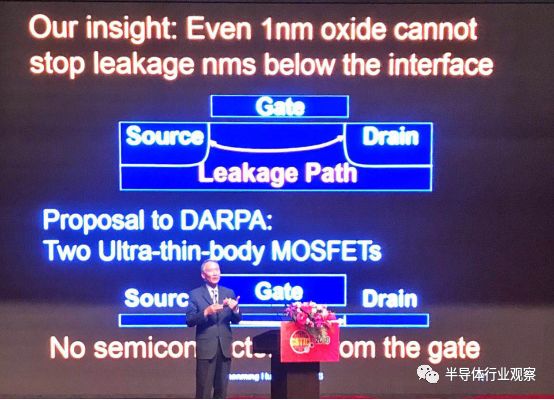

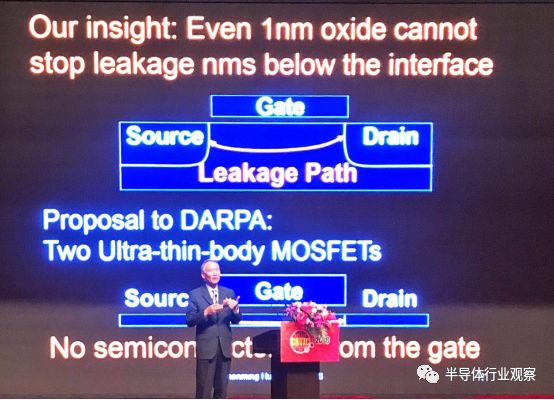

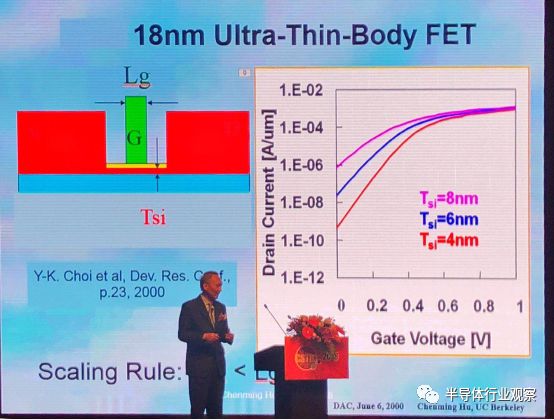

在當(dāng)時(shí),胡正明教授團(tuán)隊(duì)即發(fā)現(xiàn),即使1nm的氧化層也無法消除界面以下數(shù)納米處的漏電,所以他們向DARPA提議了兩種Ultra-thin-body的MOSFET。

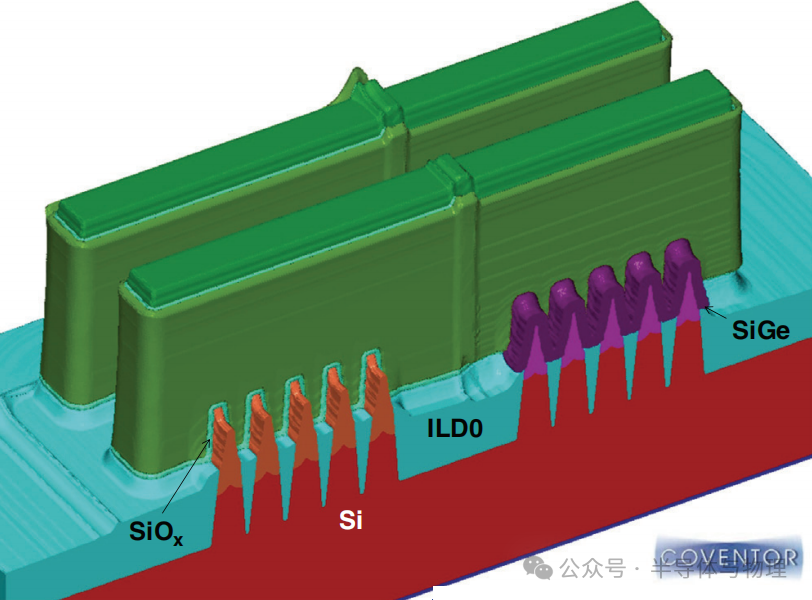

其中之一就是堪稱改變整個(gè)半導(dǎo)體歷史的FinFET:

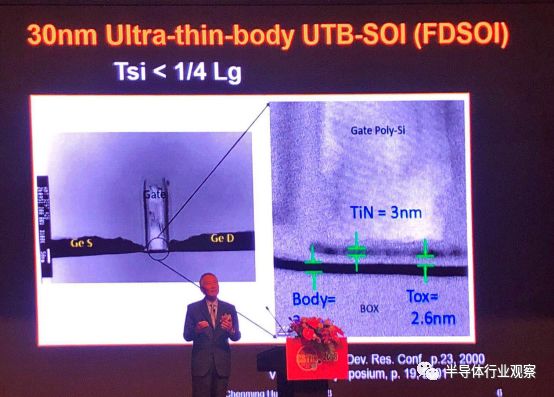

另一結(jié)構(gòu)就是UTB-SOI (FDSOI):

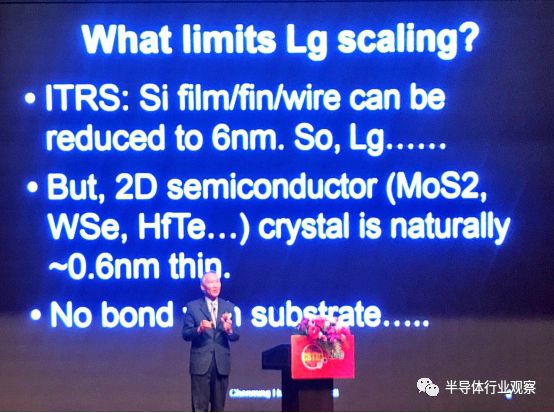

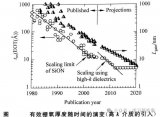

在談到限制Lg微縮的原因,根據(jù)ITRS的的觀點(diǎn),硅的film/fin/wire能夠減小到6nm。

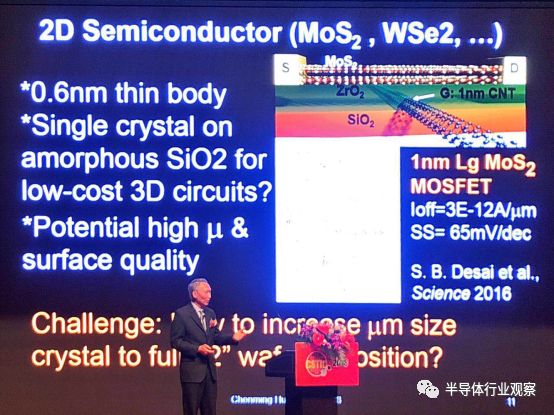

但是,MoS2、WSe和HfTE等材料的晶體天然厚度就是0.6nm,基于這些材料的2D晶體管擁有更短的Lg和更好的電學(xué)特性,但是制作工藝很困難,想要在12寸wafer上均勻生長(zhǎng)其實(shí)有很大的挑戰(zhàn)。

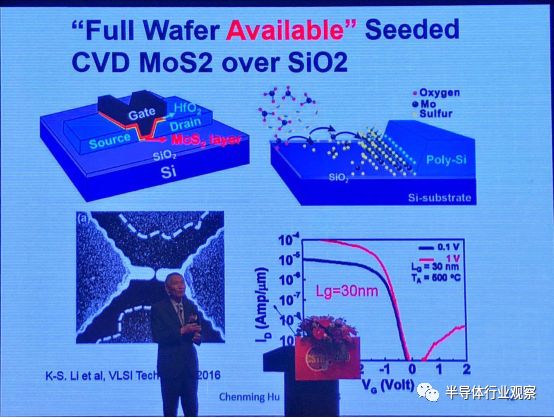

他進(jìn)一步指出,F(xiàn)ull wafer available Seeded CVD MOS2 over SiO2

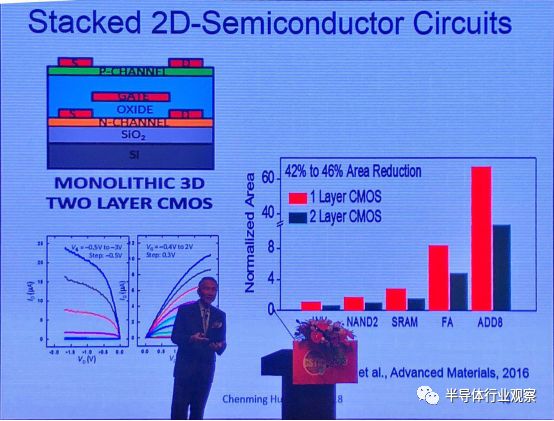

之后胡教授介紹了堆疊的2D半導(dǎo)體電路

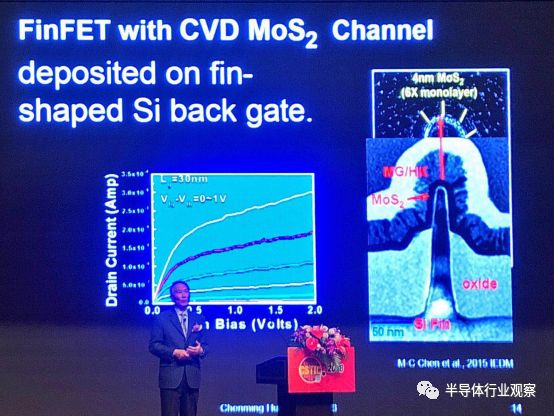

還談到了CVD MoS2 溝道放置在鰭狀Si back gate的FinFET

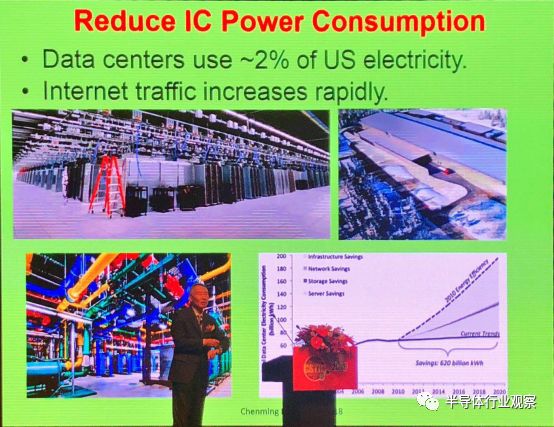

胡教授強(qiáng)調(diào)了降低IC功耗的重要性

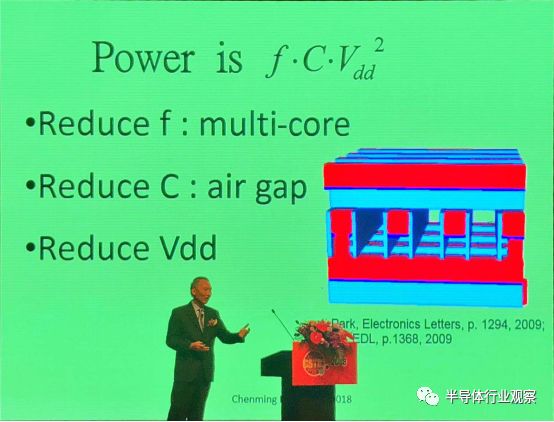

要達(dá)到降低功耗的目的,那就需要從以下三個(gè)方向考慮:

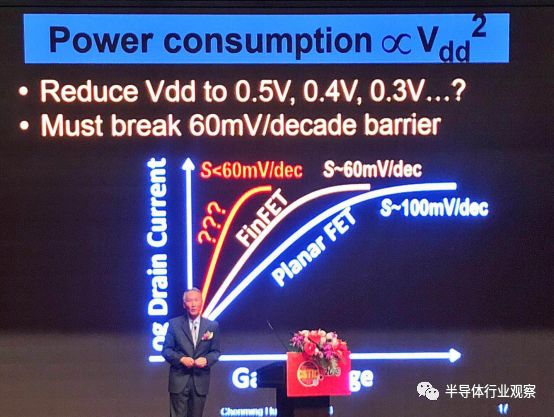

首先他分享了關(guān)于降低Vdd的觀點(diǎn)

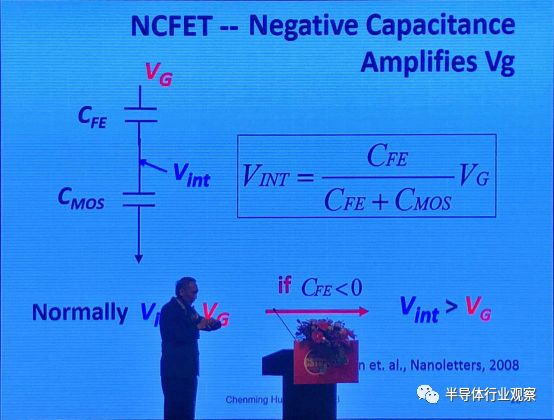

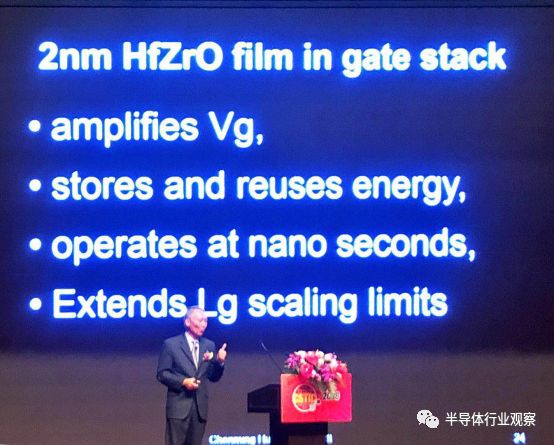

然后胡教授還談到了負(fù)電容晶體管(NCFET)

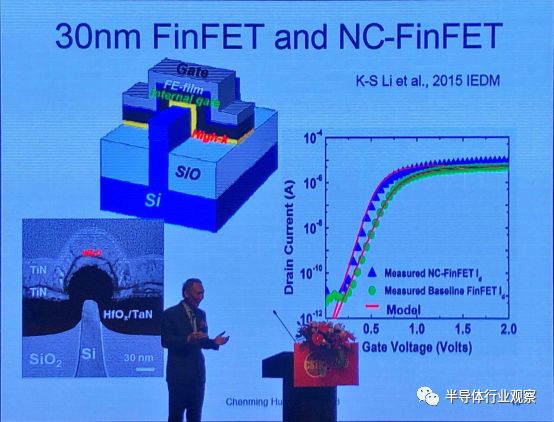

他將30納米 FinFET和NCFET做了對(duì)比

并進(jìn)一步強(qiáng)調(diào)了NCFET的特性

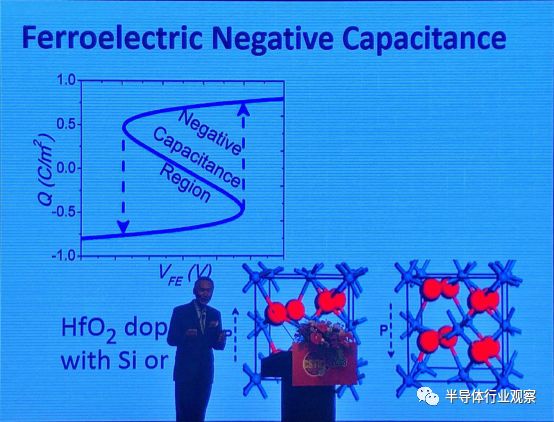

之后胡教授還介紹了Ferroelectric Negative Capacitance

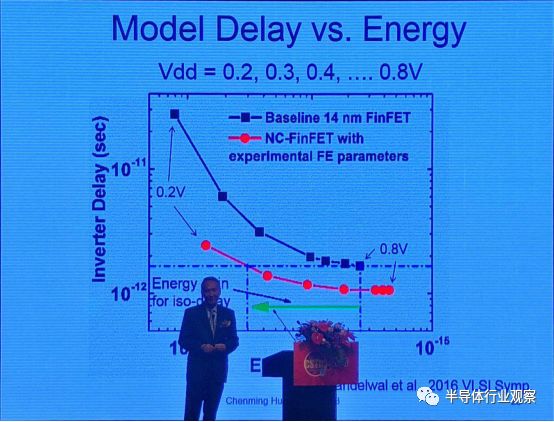

還做了一個(gè)不同電壓下的表現(xiàn)對(duì)比

他還總結(jié)了以下幾點(diǎn)

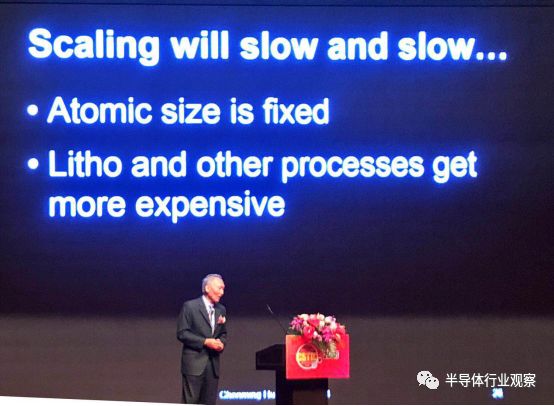

胡教授表示,晶體管微縮會(huì)變得越來越慢。

一方面因?yàn)樵拥某叽缡枪潭ǖ模瑫?huì)達(dá)到物理極限;另一方面光刻和其他制造技術(shù)變得越來越昂貴。但是通過器件創(chuàng)新,cost-power-speed能夠繼續(xù)改進(jìn)。

整個(gè)半導(dǎo)體產(chǎn)業(yè)一定能長(zhǎng)期增長(zhǎng)。不是每個(gè)人都會(huì)獲益,有輸家和贏家,但是因?yàn)榘雽?dǎo)體體量很大,贏家會(huì)很成功。過去幾年半導(dǎo)體產(chǎn)值超過1995年前所有總和,半導(dǎo)體成長(zhǎng)不會(huì)慢于全球經(jīng)濟(jì)增長(zhǎng),因?yàn)槿藗冃枰?a href="http://www.asorrir.com/v/" target="_blank">智能的設(shè)備。

最后,胡教授就他這個(gè)演講,做了一個(gè)總結(jié):

-

集成電路

+關(guān)注

關(guān)注

5418文章

11943瀏覽量

367073 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28574瀏覽量

232420 -

晶體管

+關(guān)注

關(guān)注

77文章

9977瀏覽量

140631

原文標(biāo)題:胡正明:晶體管微縮會(huì)終結(jié)嗎?

文章出處:【微信號(hào):MooreNEWS,微信公眾號(hào):摩爾芯聞】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

CMOS集成電路的基本制造工藝

集成電路設(shè)計(jì)與制造過程

鰭式場(chǎng)效應(yīng)晶體管制造工藝流程

集成電路外延片詳解:構(gòu)成、工藝與應(yīng)用的全方位剖析

集成電路制造工藝升級(jí)的過程中,晶體管微縮會(huì)終結(jié)嗎?

集成電路制造工藝升級(jí)的過程中,晶體管微縮會(huì)終結(jié)嗎?

評(píng)論