倒摻雜阱(Inverted Doping Well)技術作為一種現代半導體芯片制造中精密的摻雜方法,本文詳細介紹了倒摻雜阱工藝的特點與優勢。

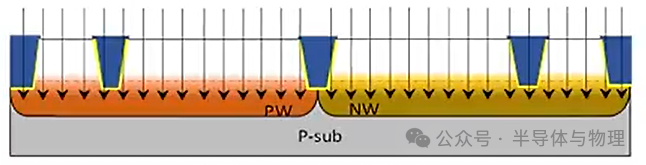

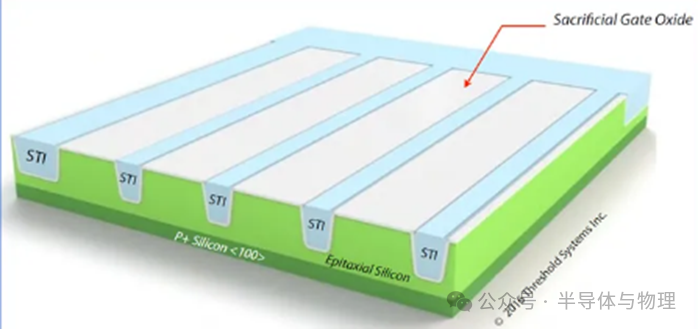

在現代半導體芯片制造中,倒摻雜阱(Inverted Doping Well)技術作為一種精密的摻雜方法,對于實現高性能和高密度的集成電路至關重要。倒摻雜阱工藝通過精確控制摻雜深度和橫向擴散,有效改善了閂鎖效應和DIBL(drain induced barrier lowering)同時降低了電流在阱等效電阻上的壓降,并且能夠靈活調節閾值電壓以優化器件性能和亞閾值漏電流,從而顯著提升了芯片的可靠性和性能,有利于制造高密度、高性能的先進半導體器件。

倒摻雜阱工藝的特點與優勢:

1、阱離子注入

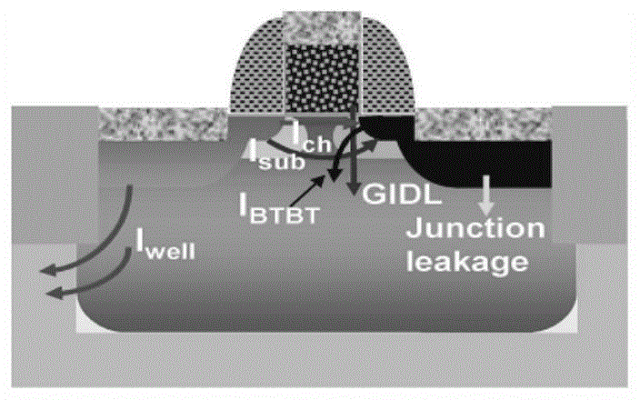

改善閂鎖效應:大摻雜濃度的深層阱區可以降低阱的等效電阻,減少電流通過時的壓降,有效緩解閂鎖效應(Latch-up),即兩個寄生雙極型晶體管之間的正反饋導通現象。

減小耗盡區寬度:增大摻雜濃度可以縮小漏極與襯底(或阱)間的耗盡區寬度,進而減輕DIBL(Drain Induced Barrier Lowering,源-柵電壓引起的閾值電壓降低)效應,提高短溝道器件的性能。

特點:采用高能量和高濃度的離子注入,峰值濃度通常出現在幾微米的深度。

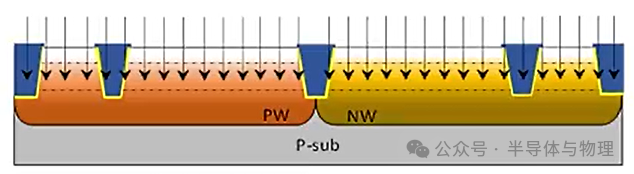

2、溝道離子注入

優化DIBL效應:適當調節溝道摻雜濃度能夠減小源和漏耗盡區寬度,進一步改善DIBL效應。

載流子遷移率折衷:增加溝道摻雜濃度雖然有助于減小DIBL效應,但也會因為庫侖散射增加而降低載流子遷移率,最終影響器件速度。因此,在提升器件穿通特性和保持高速度之間需要找到一個平衡點。

特點:使用中等能量和中等濃度的離子注入,目標區域位于高摻雜阱區上方的溝道部分,緊鄰源和漏有源區。

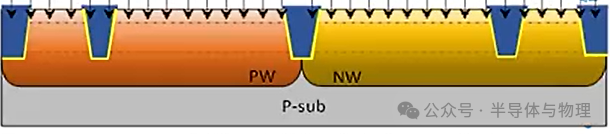

3、閾值電壓離子注入

閾值電壓調控:溝道表面附近的摻雜濃度直接決定了閾值電壓的高低,通過精準調控這一參數,可以設計出不同閾值電壓級別的晶體管,如高、中、低閾值電壓器件。

亞閾值漏電流管理:隨著閾值電壓的升高,亞閾值區的漏電流會相應減少;反之,則會增加。這為工程師提供了靈活的設計空間,以滿足特定應用的需求。

特點:利用低能量和低濃度的離子注入,重點在于溝道表面附近的摻雜濃度調整

-

半導體

+關注

關注

335文章

28625瀏覽量

232851 -

芯片制造

+關注

關注

10文章

677瀏覽量

29539

原文標題:離子注入:倒摻雜阱

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體制冷機chiller在半導體工藝制程中的高精度溫控應用解析

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

半導體制造里的ALD工藝:比“精”更“精”!

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

半導體芯片制造中倒摻雜阱工藝的特點與優勢

半導體芯片制造中倒摻雜阱工藝的特點與優勢

評論