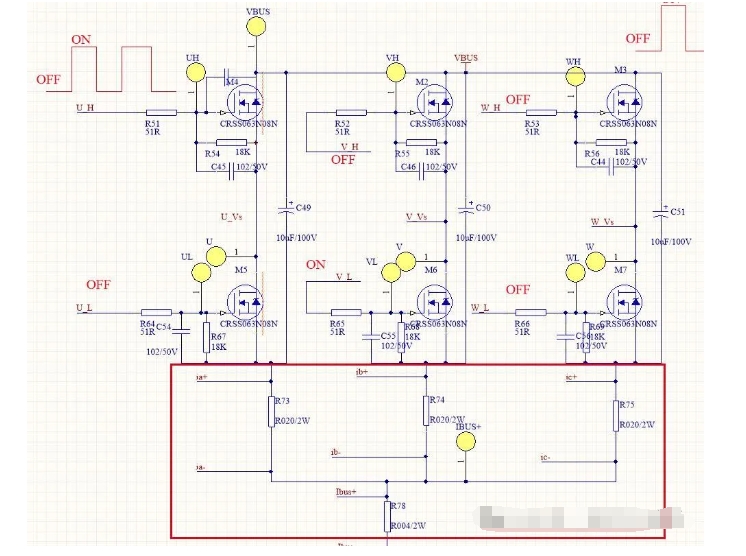

電流采樣是FOC中基礎且重要的一個步驟,只有電流采樣準確了整個算法才能獲得好的效果。電流采樣是采集續流電流,也就是在三個下管導通的時候采樣,采集中間時刻的電流,可以反映平均電流(用電感續流來理解,在電感續流的時候,中間時刻的電流就可以反應平均電流)。電流采樣方式一般分為三電阻、雙電阻、單電阻采樣,其優缺點如下圖所示。

1.2.

采樣電阻的位置

這里使用下采樣電阻,也就是電流采樣電阻放在下端,有兩個好處:一是共模電壓接近0V,信號處理相對比較容易。二是在一個PWM周期內采樣電阻存在不通電的情況,這樣可以降低采樣電阻的功率。另外,母線上還有一個母線電阻,這個電阻有兩個作用。一是用于單電阻采樣;二是采集母線電流,實現過流保護。另外,存在將電阻串在相線上的情況,如下圖所示。此時相比下電阻采樣,采集的電流就不同了,因為電流始終是連續的,不存在采樣窗口的問題。為了采集平均電流,可以采集三上橋臂導通的中間時刻的電流。但是這種方案運放的共模電壓也高了,并且由于電流始終流過電阻,所以電阻的功率要比下電阻采樣要高。

1.3.

采樣窗口問題

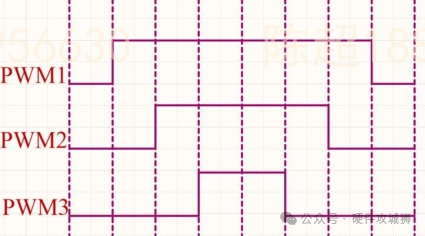

當下管的PWM占空比很小的時候,如下圖所示的PWM3。由于ADC采樣需要保持一定的時間,所以占空比很小的時候采集到的數據就可能不準。由KCL可知此時的三相電流的和為0,此時如果是三電阻采樣方案,那么可以使用另外兩相占空比大的算出第三相的電流。而如果是雙電阻采樣那么就沒辦法了,只能就這樣使用,或者限制下管的最小占空比,這樣才能保證采樣的電流是準確的。對于單電阻采樣來說,需要根據不同的開關組合得到對應的電流,而且需要在一個PWM周期內采樣兩次,依靠算法來重構三相電流,所以是最困難的一種方案。

2.運放電路

為了降低采樣電阻的功耗,一般采樣電阻的阻值都很小。那么其兩端的壓差也很小,如果直接輸入單片機的ADC進行采集,那么單片機很難分辨出來。所以為了提高分辨率,需要對電壓進行放大。此外,這么小的電壓信號在放大之前也很容易受到干擾,所以對于PCB的布局布線有要求,需要盡量減小干擾。注意:采集到的電流信號不需要進行濾波處理,因為濾波會造成信號延遲。

2.1.運放和比較器

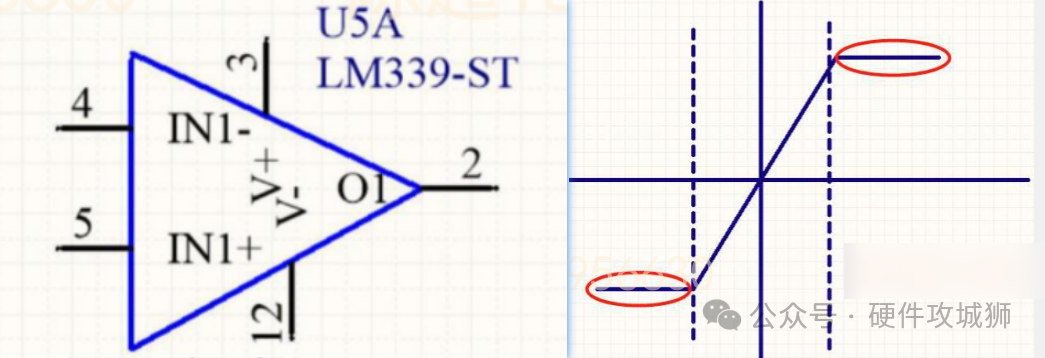

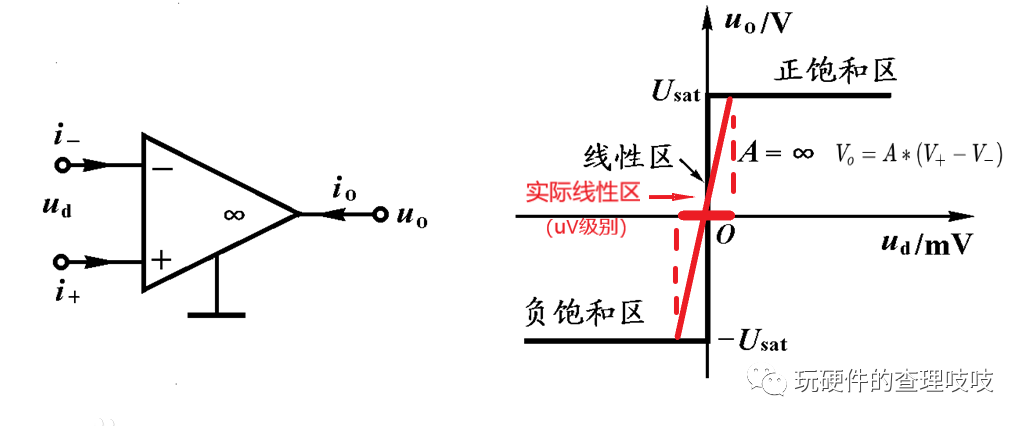

如下圖所示,比較器的兩個輸入端接兩個模擬信號,比較器的輸出是一個數字信號,即高低電平。但是比較器內部是集電極開路或者漏極開路輸出,所以需要在比較器的輸出端接上拉電阻。比較器輸出數字信號,他的跳邊沿很陡。也就是說比較器的輸出要么飽和,要么截止,而運放一般工作在放大區。所以按照輸出特性曲線來說,比較器工作在下圖的紅圈處(注意下面的紅圈也可以認為是負飽和區,只不過一般運放的負端接GND,那么就是0V,也認為是截止)。而運放工作在虛線內的放大區。為了讓比較器的輸出沿更陡,一般接一個正反饋。而運放工作在線性區。為了讓運放不飽和,一般會接一個負反饋,抑制運放的飽和,讓他工作在線性區。此外,運放接入正反饋,也可以當做比較器來使用。

2.2.

差分放大

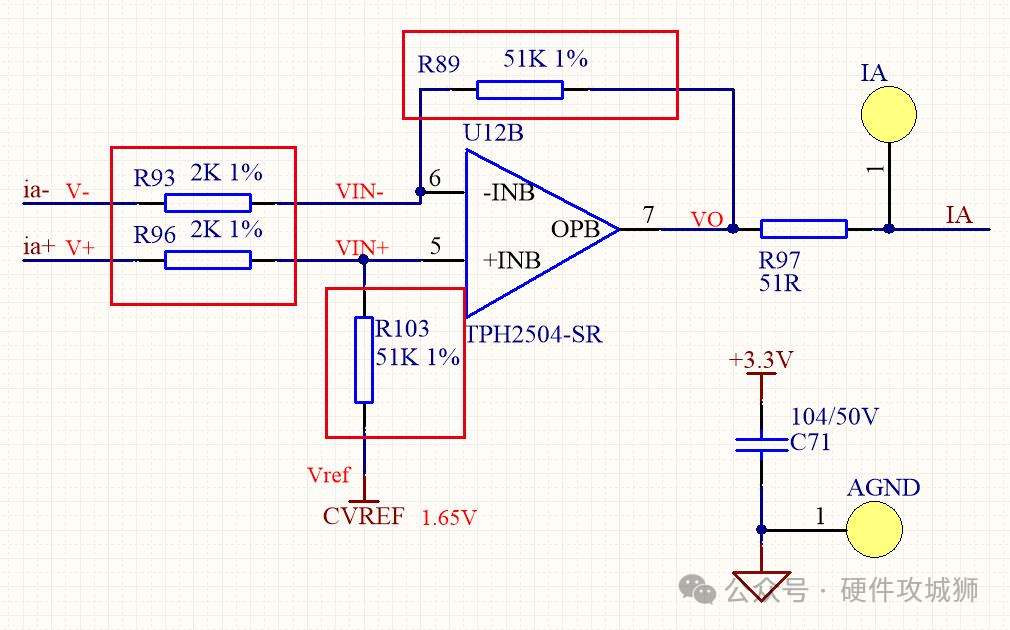

所謂差分就是對兩個信號求差,差分放大就是對兩個信號的差值進行放大。其實這里根據采樣電路就決定了使用的就是差分,因為需要計算的是采樣電阻兩端的壓差,也就是電位差,這就是差分。差分放大的好處是可以消除共模干擾,所謂共模就是信號對地來說,共模干擾就是信號相對于地這個參考點來說的干擾。如下圖所示,如果Ia+和Ia-都存在對地的干擾,那么信號作差之后共模干擾就會減小,這樣運放輸出的信號就更加準確。

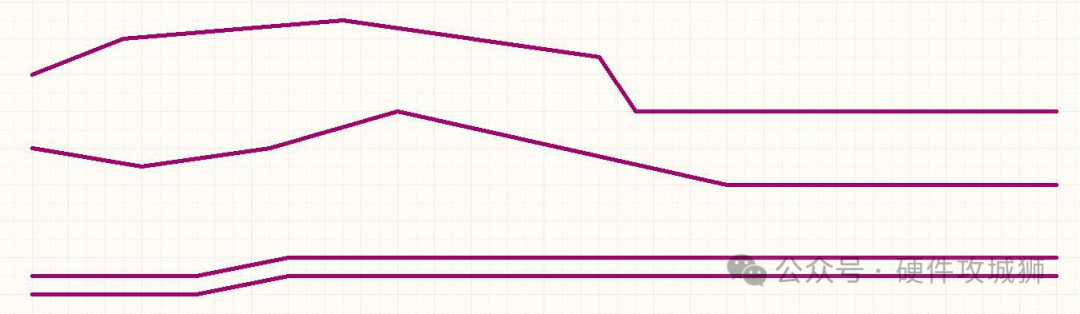

差分接法雖然可以減小共模干擾的影響,但是也存在差模干擾。所謂差模干擾,就是兩根信號線之間的干擾。這是因為兩個信號線之間的環路有磁場的變化,這樣就會引入干擾。所以差模干擾跟信號走線也有關系,如果兩根信號線之間的環路比較大的話,空間就會大,這樣磁場變化引起的干擾也就會越大。因此差分接法走線的時候也盡量要走差分線,這樣可以把環路空間減小,起到抑制差模干擾的作用。如下圖所示,上面的走線圍城的面積空間大,環路大,這樣信號線上有電流流過時,就會產生空間磁場,就會有磁耦合產生干擾。而下面的走線形式環路小,空間小,這樣產生的干擾就小,下面這種形式的走線就是差分走線。

實際的PCB中,差分走線的間距放一倍的線寬就行,一般是0.3mm。并且走線必須要同一層,不在同一層的話需要打孔,打孔的話就會產生寄生電容,這樣就會對信號產生影響,所以走線最好在同一層。

2.3.偏置電壓

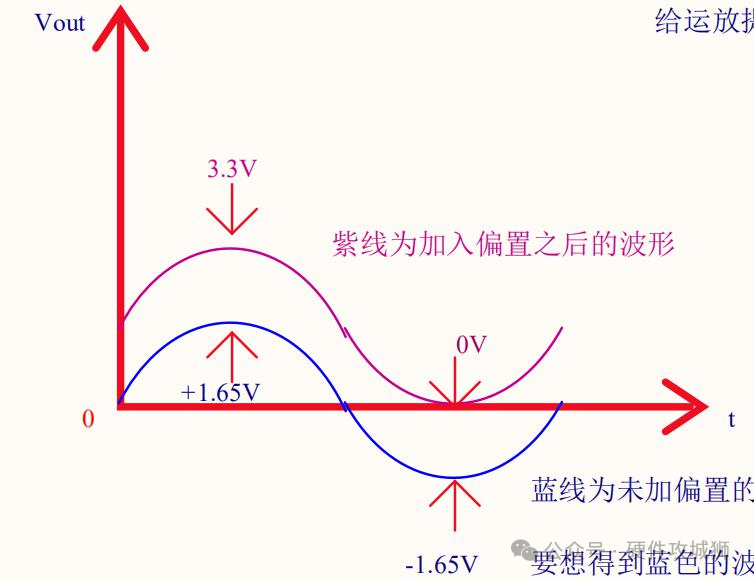

由于采樣電阻上的電流可以從下往上流,也可以從上往下流,也就是兩端的電壓可正可負,那么輸入運放的差分電壓就是正負電壓。如果運放是正負電源供電,那么此時運放可以輸出放大的正負電壓,但是單片機沒法檢測負壓信號,所以運放只能單電源供電。如果運放是單電源供電,那么又無法輸出負壓,所以需要對負壓進行處理,也就是對負壓進行電壓抬升,如下圖所示。這個抬升電壓也很簡單,根據波形對稱,再考慮單片機的AD采樣電壓為3.3V,所以選擇3.3V的一半。

2.4.運放放大倍數的選擇

為了提高分辨率,讓運放的輸出越接近3.3V越好,留一點余量一般考慮輸出3V即可。這里的運放輸出3V,指的是采樣電阻流過電機的額定電流時運放的輸出。所以這里也能看出來,如果電機的工況能夠確定,這里的運放放大倍數也能確定。也就是如果選了個大電機,而工況都是小負載電流很小,那么按照電機額定電流設計的電路板的分辨率就會低,控制效果不好。這也解釋了為什么ODrive在云臺電機這種小電流的電機上沒有進行電流采樣,因為它是針對大電流設計的,小電流的時候分辨率太低了。對于以下電阻的取值,需要根據放大倍數來選擇。反饋電阻一般不建議大于100K,因為根據大量測試大于100K的話容易引入噪音,也就是干擾。最后根據運放的虛短和虛斷就可以求得運放的輸出和輸入之間的關系。

![]()

在匹配好放大倍數的前提下,這里的2K電阻考慮到了一定的限流作用,而且功耗會低一些。其他沒有很多的考慮,這里選擇1K的電阻,然后和反饋電阻匹配好放大倍數也可以。

此外,有的時候會在運放的兩個輸入端接入一個pF級別的電容,用于濾除差分干擾。但是只要能夠控制這個差分回路,可以不用接這個電容,接了這個電容可能會對信號造成延遲。所以即使加,也是加入一個很小的電容,pF級別。運放的輸出到單片機的ADC引腳之間有一個電阻R97,這個電阻一般取值為幾十歐姆,要考慮ADC內部的采樣保持電容的充電時間。這個電阻是充電阻抗,可以破壞走線寄生參數帶來的震蕩。因為走線上存在寄生參數,很容易滿足震蕩條件,加了電阻的話可以破壞震蕩條件。(?)

2.5.運放選型

運放選型一般從供電電壓、帶寬、速度(壓擺率)等角度考慮。供電電壓一般參考單片機的電壓來選擇, 比如3.3V的單片機就選擇3.3V供電的運放。帶寬就是在這個頻率范圍內,放大的信號不出現衰減或失真,一般經驗值選擇5-20M。壓擺率表示運放的輸出速度,也就是輸出電壓的變化率,一般選擇在5-10V/us。此外, 采樣電阻上的信號的頻率并不等于載波頻率,而是跟轉速有關系,也就是一個電周期的頻率大小。電流采樣的運放不一定要選擇高速運放,一般來說壓擺率選擇5V/us也足夠使用。

-

運放

+關注

關注

49文章

1190瀏覽量

54022 -

電流采樣

+關注

關注

2文章

49瀏覽量

17140

原文標題:電流采樣與運放電路

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電流采樣與運放電路分享

電流采樣與運放電路分享

評論