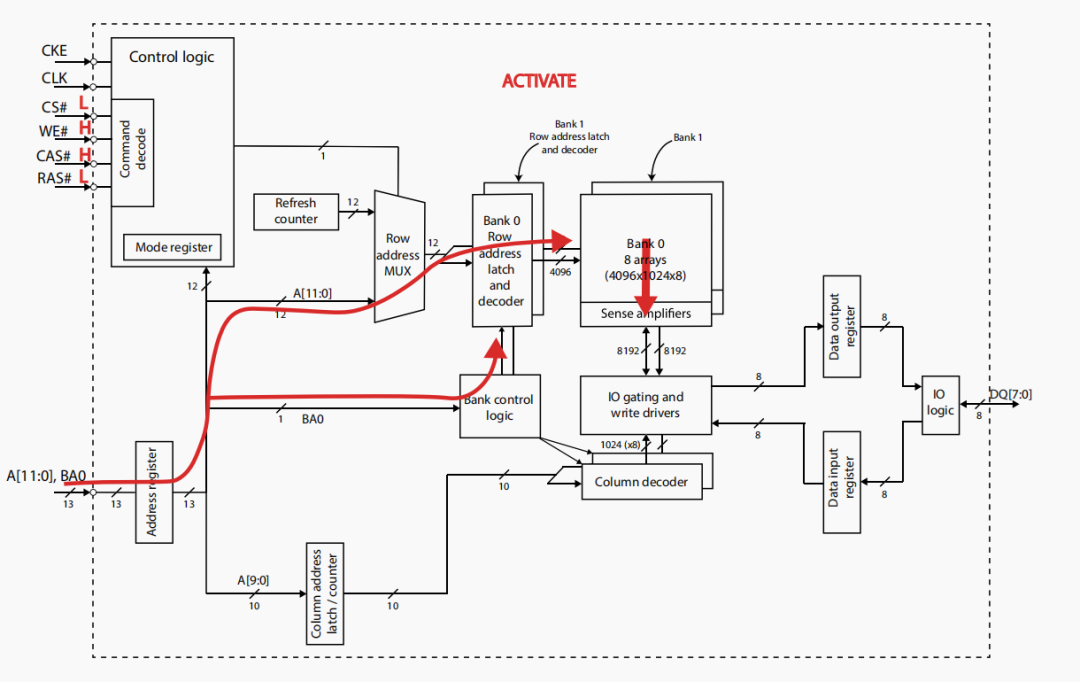

在向SDRAM 中的任何行發出 READ或 WRITE 命令之前,必須先打開該行。這是通過 ACTIVE 命令完成的。ACTIVE 命令的目的是打開或者說激活(active)bank中的一行并將數據從 DRAM 移動到bank的靈敏放大器。下圖說明了 ACTIVE 命令的執行情況。

來自地址總線的地址 A11-A0存儲在所選bank的行地址鎖存器和譯碼器中。地址位BA選擇bank及其行地址鎖存器和解碼器。

然后,將整個數據行讀入靈敏放大器中。與 DRAM 類似,與ACTIVE 命令相關的兩個timing是:行地址到列地址延遲 (tRCD)和行有效時間 tRAS。

tRCD是激活命令將數據從DRAM單元陣列移動到保持整個數據行的感測放大器所需的時間。在tRCD之后,可以發出某列讀或寫訪問命令,通過輸入/輸出buffer和數據總線在感測放大器和內存控制器之間移動數據 。

行地址到列地址延遲tRCD,應除以時鐘周期,向上取整到最接近的整數,以確定ACTIVE命令后讀寫的最早時鐘邊沿。例如,具有125 MHz 時鐘(周期為8納秒),20 納秒的tRCD產生2.5 個時鐘周期,四舍五入為 3。

向同一rank中不同行發出的ACTIVE 命令只能在先前激活的行被預充電后發出。

行激活時間,tRAS,是必須經過的最小時間,這之后才能向打開的行發出PRECHARGE命令。所以,tRAS也稱為作為激活到預充電時間。

-

SDRAM

+關注

關注

7文章

441瀏覽量

56020 -

鎖存器

+關注

關注

8文章

922瀏覽量

42107 -

命令

+關注

關注

5文章

726瀏覽量

22671

原文標題:SDRAM中的active命令介紹

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高分辨率視頻圖像處理中SDRAM控制器的設計

SDRAM的介紹及設計應用

SOPC中SDRAM controller 的Timing配置

【開源騷客】《輕松設計SDRAM控制器》第六講—SDRAM寫模塊講解

【開源騷客】《輕松設計SDRAM控制器》第八講—命令解析模塊講解

SDRAM理論基礎講解

教程 | SDRAM讀寫時序介紹(配時序圖)

SDRAM控制器的設備與VHDL實現

SiTime產品及Active-Semi 產品介紹

DRAM、SDRAM及DDR SDRAM之間的概念詳解

如何操作SDRAM的自刷新命令而不影響正常讀寫操作?

SDRAM中的active命令介紹

SDRAM中的active命令介紹

評論