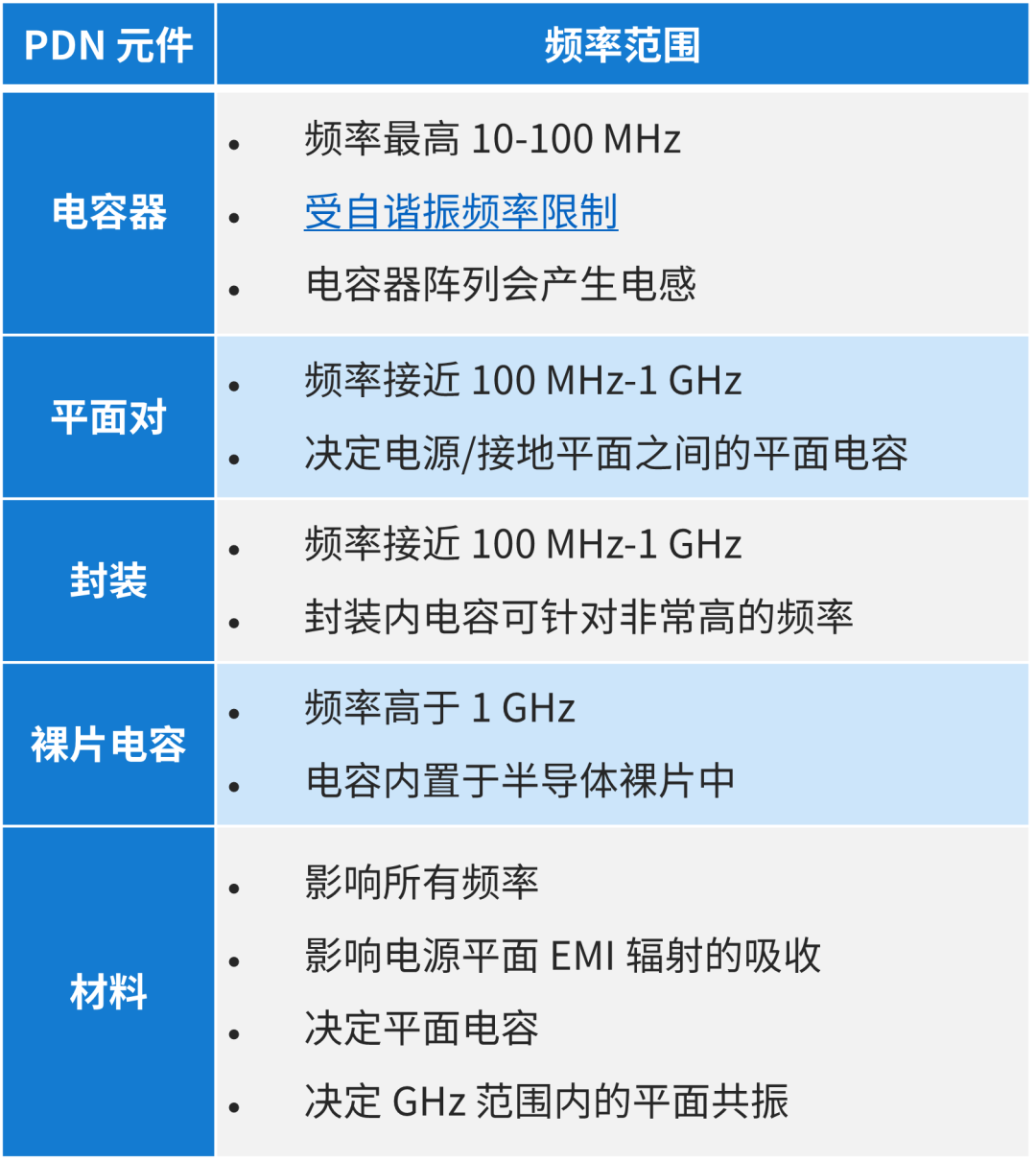

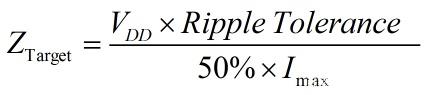

在數字系統中,PCB 的電源分配網絡 (power delivery network,即 PDN) 需要在較寬的頻率范圍內具有較低的阻抗值,以確保在數字器件運行時,電壓波動能保持在較低水平。決定 PDN 阻抗的因素有很多,不單單是數字處理器中用于穩定功率輸出的電容器。在工作頻率達到 GHz 級別的先進系統中,PDN 阻抗不僅受到電容器的影響,還有很多因素會決定 PDN 阻抗,即便在非常高的頻率下也是如此。

1

SMD 電容器(頻率范圍最高 10-100 MHz)

電容器是決定 PDN 阻抗并確保穩定功率傳輸的主要元件。大多數市售電容器都能保持較低的 PDN 阻抗,但它們所能達到的頻率范圍取決于以下多種因素:

電容值

ESR 和 ESL 值(決定自諧振頻率)

SMD 電容器外殼尺寸

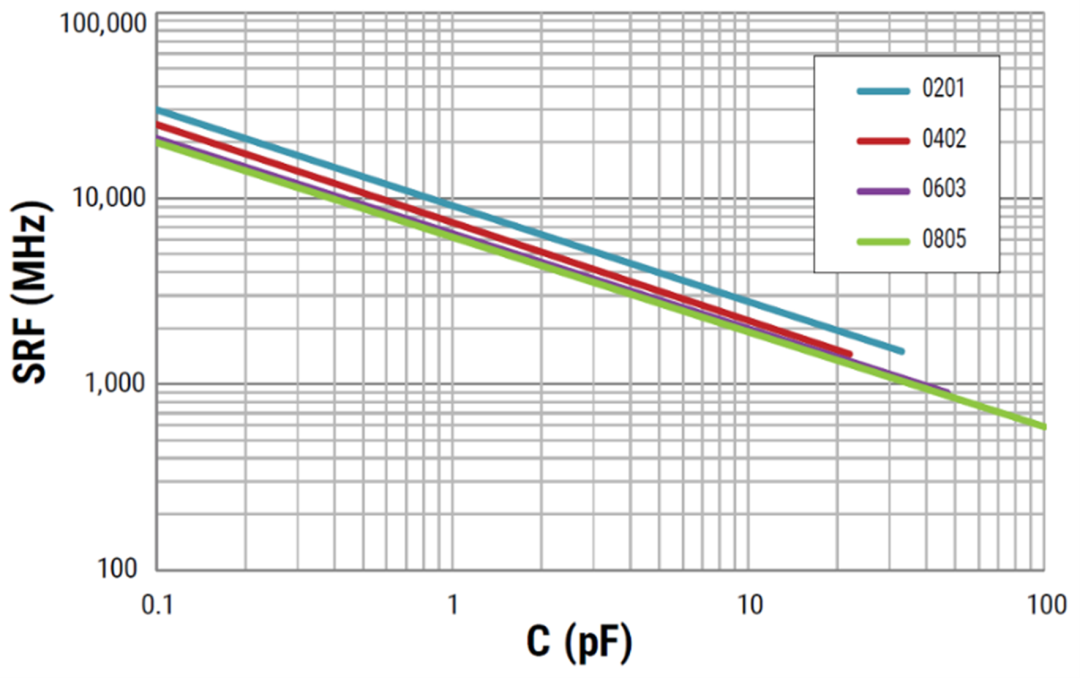

要判斷電容器能否確保 PDN 阻抗維持在較低水平,最終考慮的頻率范圍是電容器的自諧振頻率范圍。總體來說,較小的外殼尺寸和較低的電容值可提供較高的自諧振頻率。

有些電容器是專門針對非常高的頻率設計的,如 RF 電路中使用的電容器。讓我們通過一個例子來了解一下這些電容器開始產生電感的頻率范圍。我們可以看到,這些電容器的自諧振頻率因外殼尺寸而異,可以達到非常高的數值(理論上而言)。實際上,并非所有電容器都能達到如下所示的極高諧振頻率。我們將在下文中詳細說明。

不同外殼尺寸下高頻電容器的自諧振頻率變化趨勢。

2

平面對(頻率范圍接近 100 MHz-1 GHz)

當 PDN 阻抗曲線接近 100 MHz 的范圍時,電容器將停止供電,而 PDN 阻抗曲線將由平面電容決定。當數字系統需要較大的電流時,會使用電源-接地平面對,這樣也是為了提供較高的電容,以便在極高的諧振頻率下仍能保持電容阻抗。平面的功率輸出能力取決于電源-接地平面對中的擴散電感 (spreading inductance)。

最終,在非常高的頻率(數十 Ghz)下,平面將開始共振并從邊緣散發輻射。這時,平面對中的材料選擇和電介質厚度成為影響 PDN 阻抗和噪聲發射的主要因素。

3

封裝(頻率范圍從 100 MHz 到 1 GHz)

先進數字器件的封裝可包含自身的電容,以便在 GHz 范圍內以較低的阻抗傳輸功率。這些器件可對 PCB 上的平面對進行補償,因為平面對在 GHz 頻率下可能會產生電感。

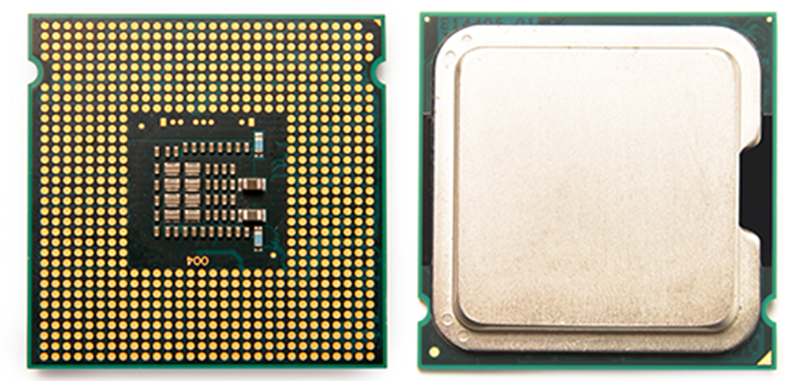

此類封裝包括片式電容器,可能還包括嵌入式電容器,以確保穩定的功率傳輸和較低的 PDN 阻抗,直接作用于器件封裝中的半導體裸片。將這些電容直接置于封裝上,可避免 PCB 上的焊盤和過孔產生電感,還可避免 BGA/LGA 封裝中的引腳電感。

CPU 封裝可包含自身的 PDN 元件,以便在低阻抗下實現功率傳輸。

4

裸片電容(頻率范圍大約在 1 GHz 以上)

半導體裸片可提供自身的電容,通常在裸片上直接提供總計 pF 級別的電容。該電容的好處是直接位于裸片上,電感極小,可為數字接口供電。這是在 1 GHz 或以上的頻率下提供電容的最佳用例,以便支持速度最快的數字接口。

5

PCB 材料(所有頻率)

任何 PCB 材料都會影響電磁波的傳播,從而影響 PDN 阻抗曲線。我們在上文介紹電源-接地平面對時說過,在數十 GHz 頻率下,平面區域會像平行板諧振器一樣開始共振。

為確保電源-接地平面對發揮最大作用,分隔二者的材料應具備一些重要特性:

首選高 Dk 值的材料,因為它們能提供更高的電容

損耗正切值適中或較高,以抑制噪音

首選薄層材料,以獲得更高的電容和更高的諧振截止頻率

使用非常薄的高 Dk 值電介質(如嵌入式電容材料),可以減少振蕩 PDN 的輻射發射,并提高總平面電容。這些材料的成本較高,但在高帶寬、高功率的數字系統中卻經常需要。

6

總結

我們通過下表總結了 PDN 的各個部分及其對頻率的影響。

電源完整性的最后一個關鍵因素與 PCB 完全無關,這個因素是電源穩壓器或 VRM 的頻率響應能力。VRM 電路通過控制環路確保穩定的輸出電壓,而 VRM 的頻率響應需要足夠快,以便抑制功率輸出可能存在的噪聲。如果電源軌上出現快速瞬變,VRM 就不能進入持續振蕩狀態。在為大型數字處理器設計高電流/低電壓電源穩壓器時,瞬變下的測量值應滿足要求。

-

pcb

+關注

關注

4351文章

23405瀏覽量

406585 -

阻抗

+關注

關注

17文章

970瀏覽量

47016 -

數字系統

+關注

關注

0文章

150瀏覽量

21129 -

PDN

+關注

關注

0文章

84瀏覽量

22992

發布評論請先 登錄

搞定電源完整性,不如先研究PDN!

【送書福利】不懂PDN談何電源完整性?請收下這本PDN設計指導硬核書

電源傳輸網絡(PDN)的具體作用

基于可分解的多目標進化算法的PDN阻抗的優化

電源完整性和配電網絡阻抗對同步開關噪聲的影響

具有寄生提取功能的PDN阻抗分析(Q&A)

PDN設計

PDN 元件對阻抗的影響

PDN 元件對阻抗的影響

評論