高速先生成員--姜杰

聊電容,不能只聊電容,還要聊電阻和電感。看似很簡單,其實,一點都不難。

因為去耦電容的模型基本都可以用下面三種元素的簡單組合來表示。

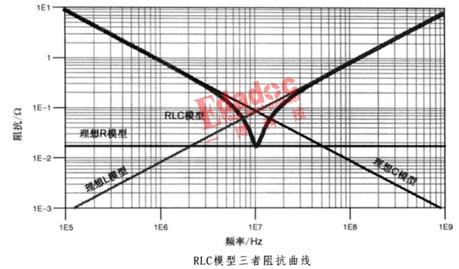

理想電容C的阻抗是隨頻率的增加而逐漸減小的一條斜線,實際上由于電容中等效寄生電阻(ESR)和等效寄生電感(ESL)的攪局,問題開始變得復雜。不同的電容自諧振頻點不同,諧振點阻抗各異,濾波頻段也有區(qū)別……

看似很復雜,其實,很簡單。

電容搞搞“振”,第一“振”來自同一電容ESRESLC的串聯(lián)諧振(也叫做自諧振)。

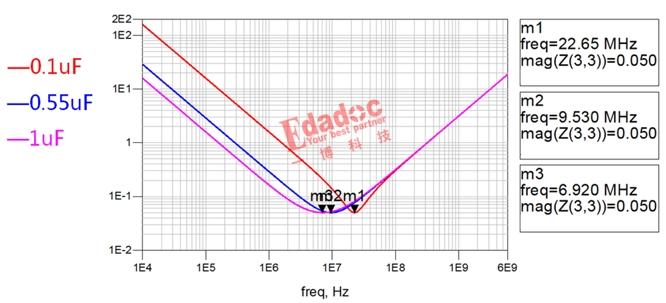

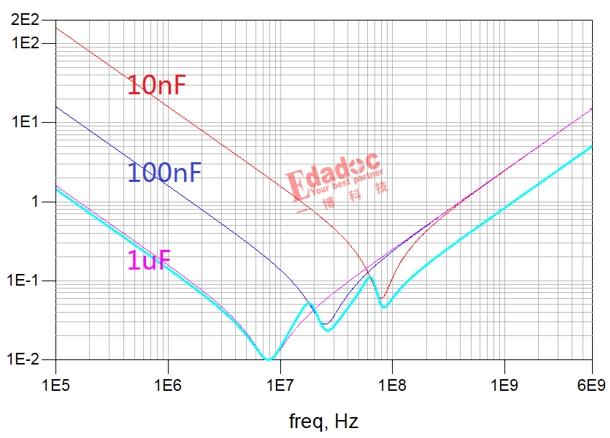

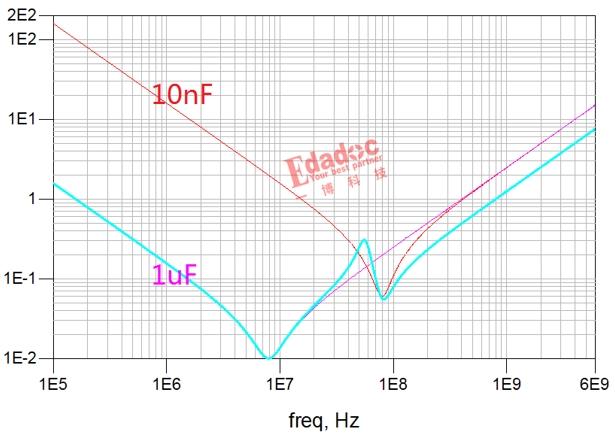

先來看看電容模型的各參數(shù)是如何影響阻抗曲線的。對于電容容值C,不難發(fā)現(xiàn),相同ESR和ESL的情況下,隨著容值的增加,自諧振頻點向低頻移動,同時,濾波頻段也會加寬。

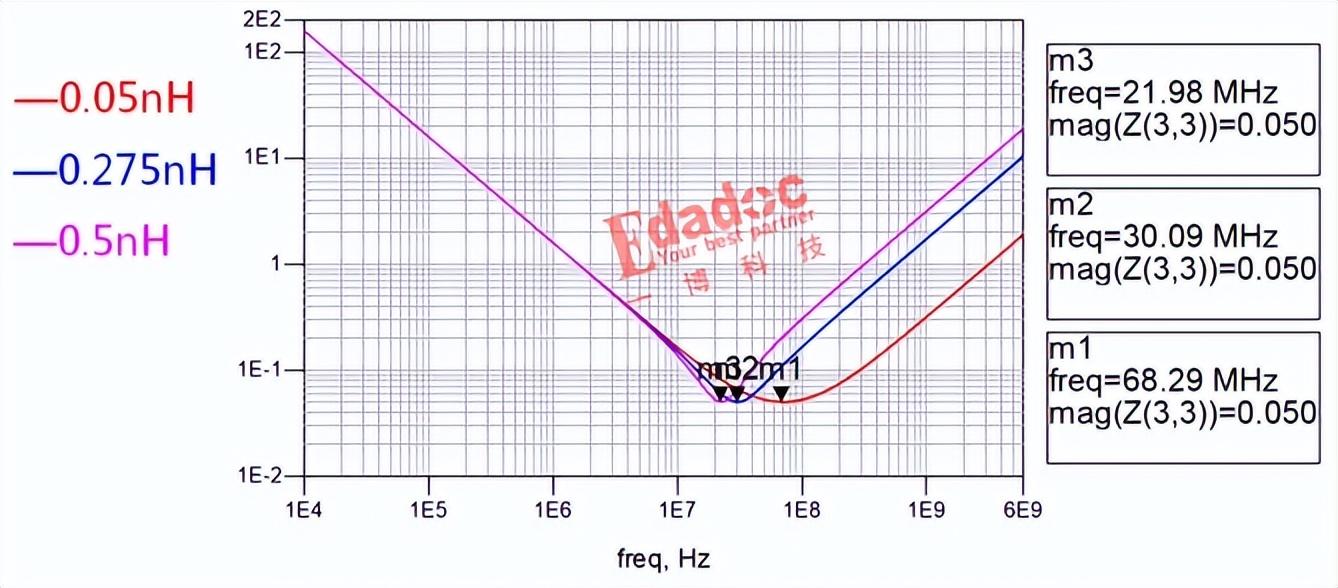

接下來再看哈ESL的影響。在保持其它參數(shù)不變的情況下,隨著ESL的增加,自諧振頻點向低頻移動,同時,濾波頻段也會隨著變小。

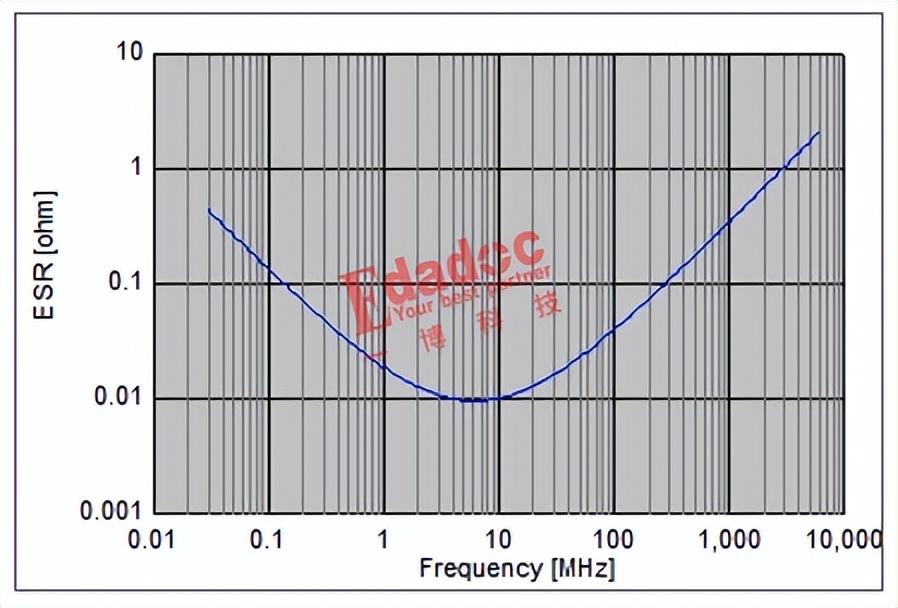

需要注意的是,ESR的情況會復雜一些,因為它是一個頻變的參數(shù)。

ESR隨頻率變化的趨勢與該電容的阻抗變化一致。

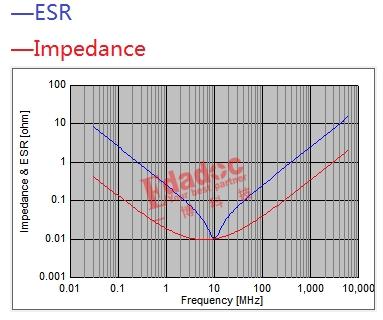

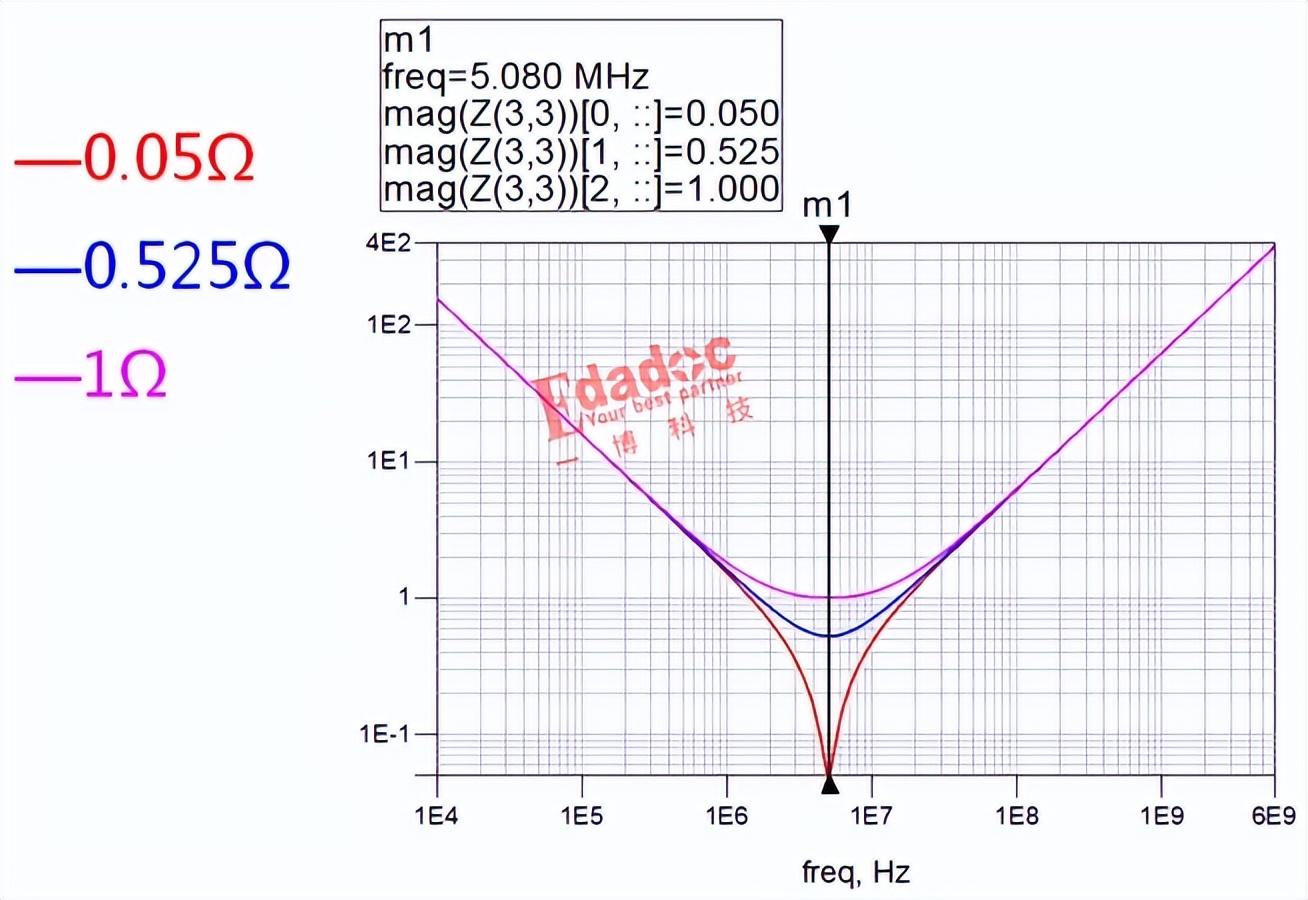

不過,為了簡化問題,我們這里先把ESR作為一個常數(shù),它的變化對阻抗曲線的影響如下圖。

對比上面幾個圖,我們會發(fā)現(xiàn)一個有趣的現(xiàn)象,那就是電容自諧振頻點的ESR基本決定了阻抗的最小值。

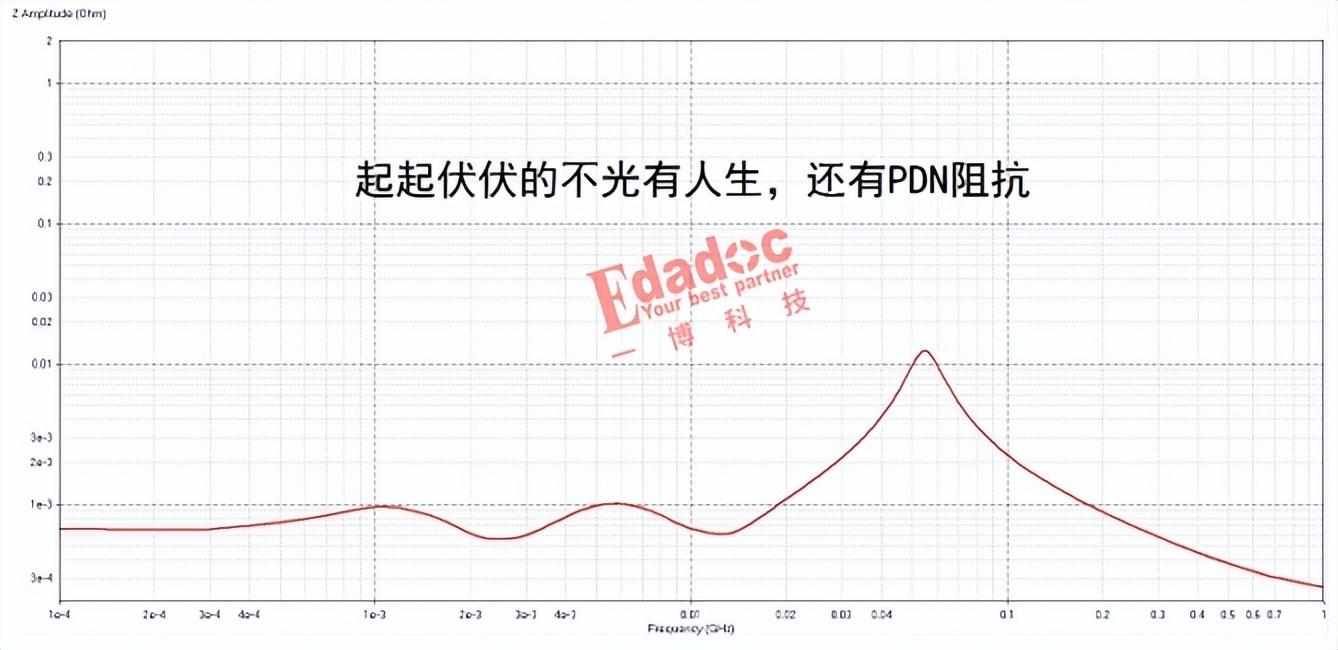

以上只是單一容值電容的阻抗曲線。了解PDN阻抗曲線的童鞋會發(fā)現(xiàn)常見情況并非如此,而是像人生一樣總是起起伏伏。

其實,這是容值不同的電容并聯(lián)諧振的結果,也是本文要說的第二“振”。

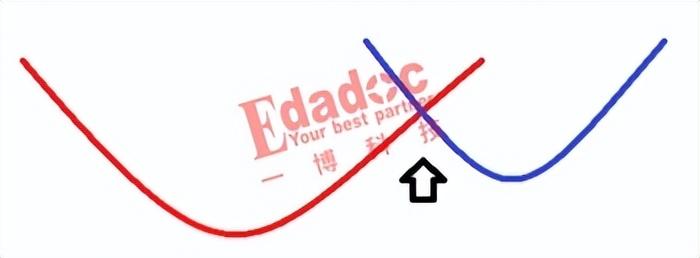

分析起來也很簡單,當一個電容的感性區(qū)遇上另一個電容的容性區(qū),諧振峰就出現(xiàn)了。

綜合考慮VRM和芯片內去耦,如果說第一“振”決定了阻抗曲線的波谷,第二“振”通常確定了阻抗曲線的波峰。

電容種類這么多,原理圖設計或者備料出錯的機會大大增加,作為一名設計攻城獅,希望板子簡單點,精簡一些電容,這個要求并不過分吧?

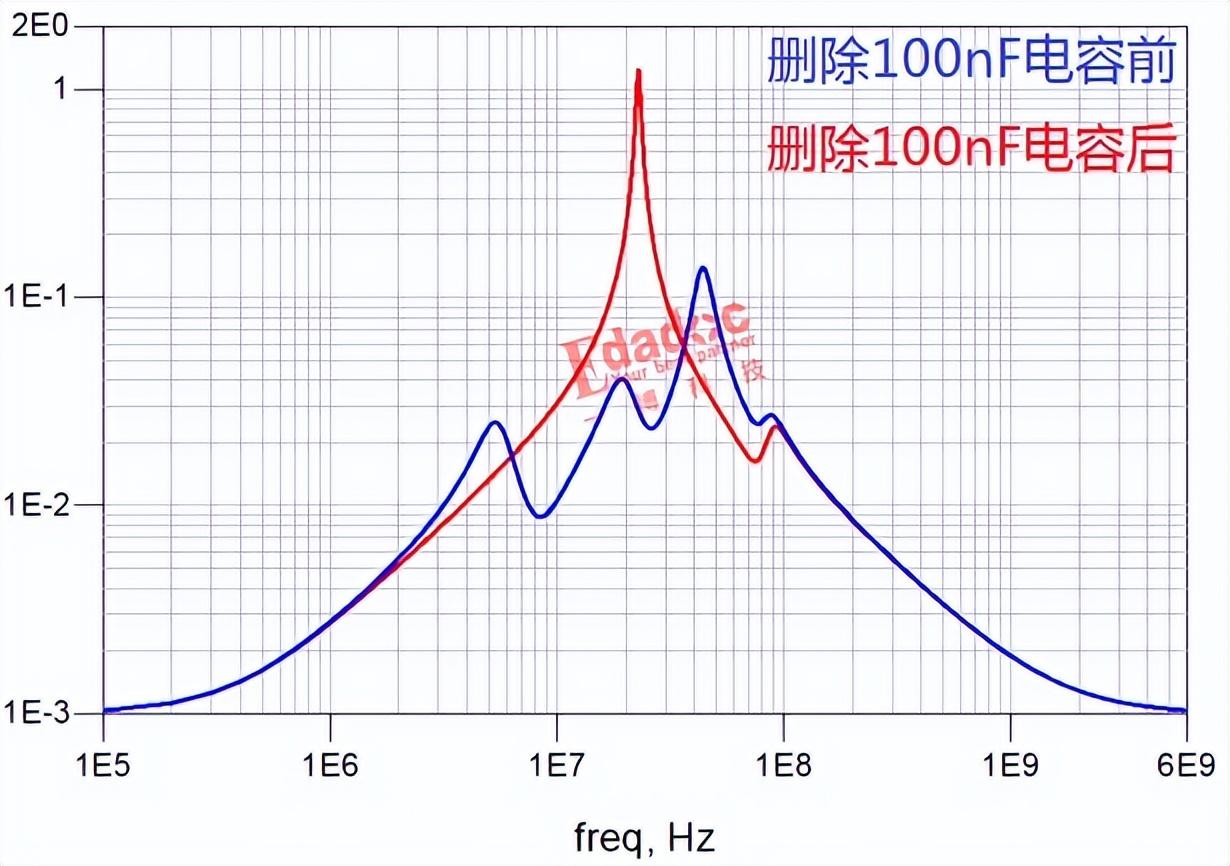

說干就干,在前文三種電容并聯(lián)的基礎上,去掉100nF的電容,看看會怎樣。

這么看,除了在100nF的去耦頻段出現(xiàn)一個諧振峰,好像也沒什么問題,畢竟,這個峰值也沒那么高。我們繼續(xù)把VRM和芯片內去耦模型加上,看全鏈路的情況。

See?高速先生一直強調的調整電容要合理真不是嚇唬你。

當然,這個例子只是為了凸顯電容影響而挑選的極端情況。

電容不是老虎屁股,一點摸不得,具體種類和數(shù)量可以通過仿真進行優(yōu)化,是增是減,It depends!

對于電容相關的電感參數(shù),除了電容自身的ESL,還需要關注什么?

審核編輯 黃宇

-

電容

+關注

關注

100文章

6233瀏覽量

153292 -

PDN

+關注

關注

0文章

84瀏覽量

23007

發(fā)布評論請先 登錄

PDN 電源分配網絡設計步驟 PDN layout步驟

電容搞搞”振“,PDN有幫襯

電容搞搞”振“,PDN有幫襯

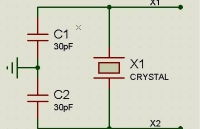

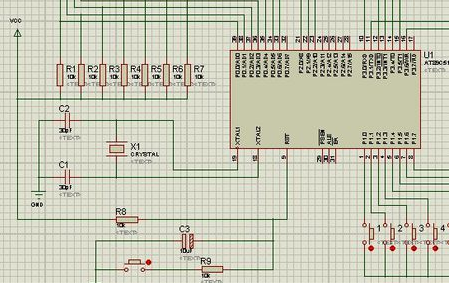

單片機晶振的負載電容有什么作用

PDN設計

PDN 電源分配網絡設計步驟 PDN layout步驟

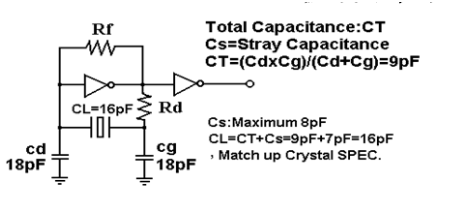

無源晶振(Crystal)的負載電容

引起單片機晶振不起振的原因有哪些呢?

PDN 元件對阻抗的影響

電容搞搞”振“,PDN有幫襯

電容搞搞”振“,PDN有幫襯

評論