PDN 阻抗仿真概述

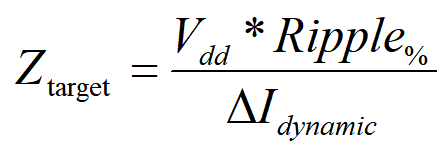

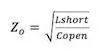

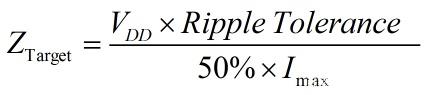

PDN(Power Delivery Network)阻抗表征電源分配網(wǎng)絡(luò)在頻域內(nèi)的動態(tài)響應(yīng)特性,定義為從負載端觀察到的電源分配系統(tǒng)輸入阻抗。其設(shè)計目標為在全頻段內(nèi)保持PDN阻抗低于目標阻抗(Target Impedance),目標阻抗的計算公式為:

其中,△Idynamic為負載芯片瞬態(tài)電流變化量,通常取Imax的50%作為經(jīng)驗值。電源噪聲容限(Ripple%)根據(jù)應(yīng)用場景不同,典型值為3%~5%。

建模及結(jié)果分析

我們可以使用SIDesigner仿真軟件,進行PDN前仿真分析,有以下兩種方法:

S參數(shù)仿真方法(頻域法)

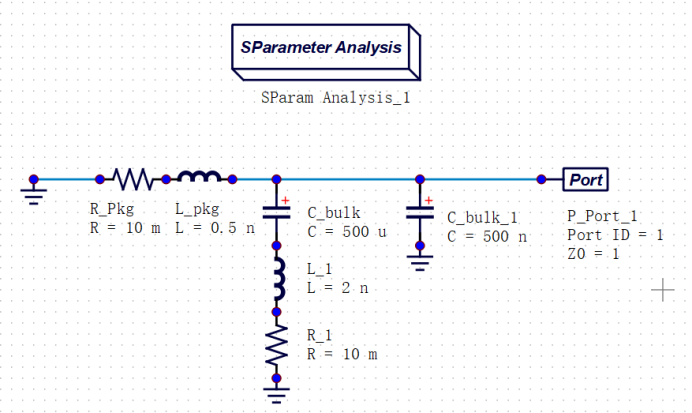

1. 等效電路建模:

在SIDesigner中構(gòu)建分布式PDN模型,包含:

板級寄生參數(shù)Rpkg=5mΩ ,Lpkg=0.5nH;

去耦電容網(wǎng)絡(luò)Cbulk=500uF,ESL=2nH,ESR=10mΩ;

片上電容Cdie=500nF。

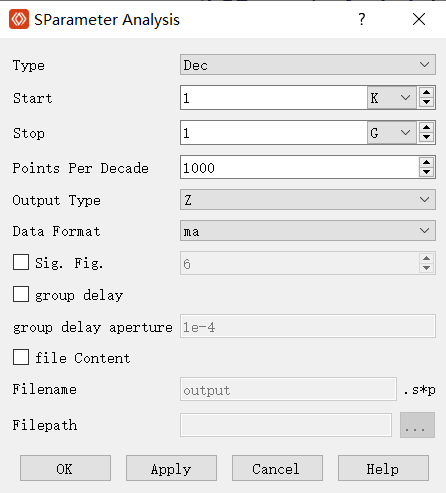

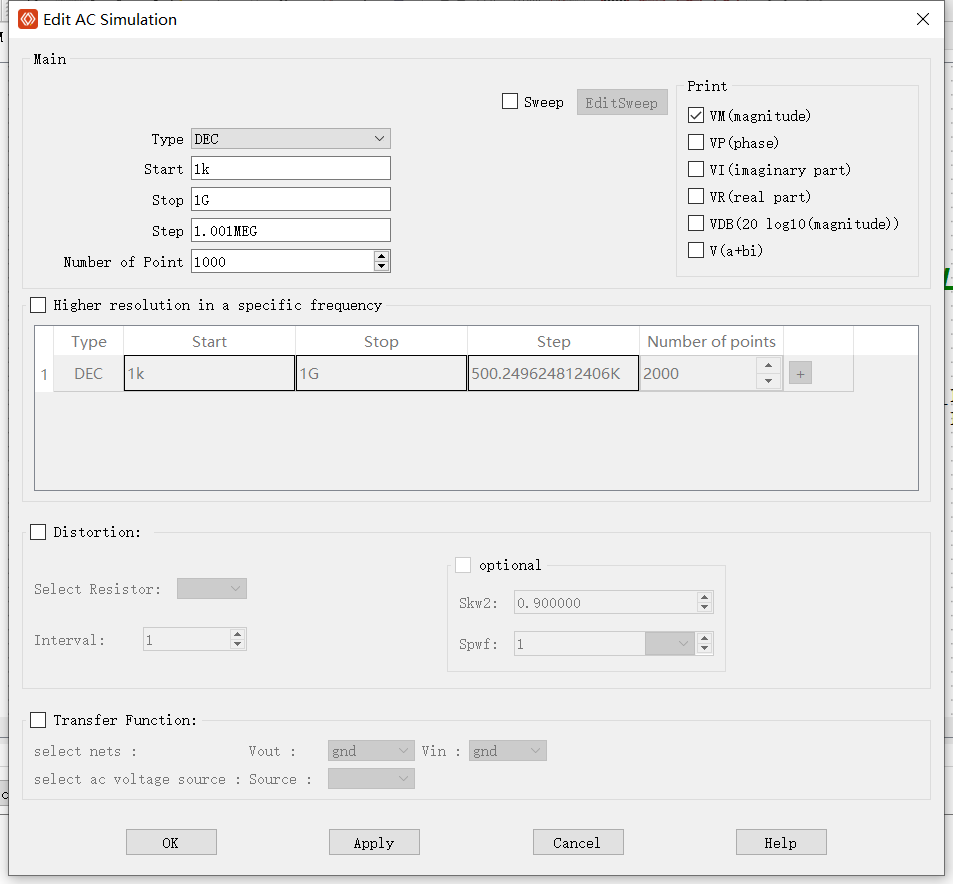

2. 仿真設(shè)置:

采用S參數(shù)仿真,掃頻范圍1kHz–1GHz,提取Z11參數(shù)作為PDN阻抗曲線。

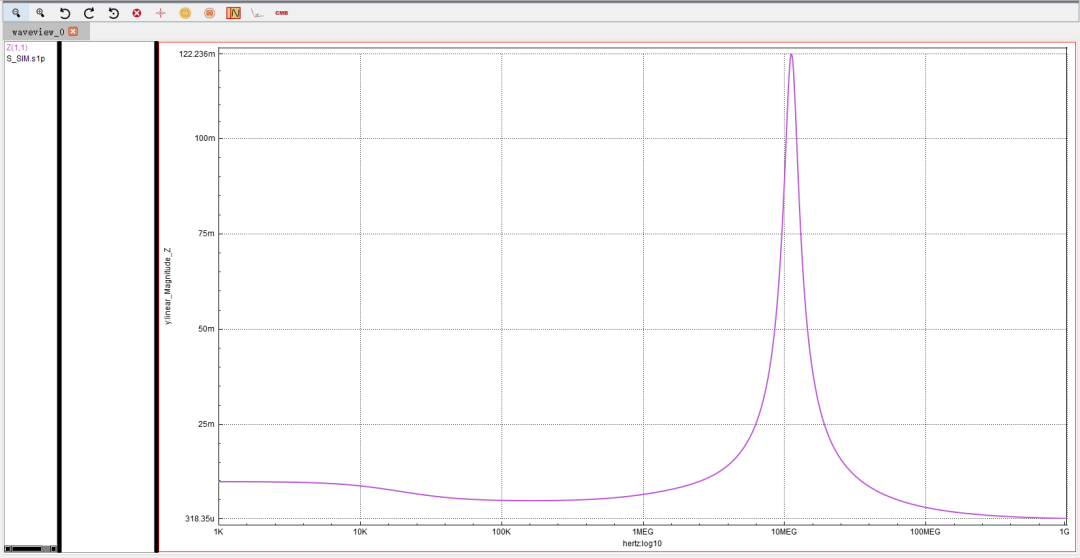

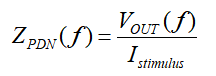

3. 關(guān)鍵結(jié)果:

11.2MHz頻點處,因Cbulk與Cdie的LC諧振產(chǎn)生反諧振峰(Anti-resonance),導(dǎo)致阻抗抬升2個數(shù)量級。

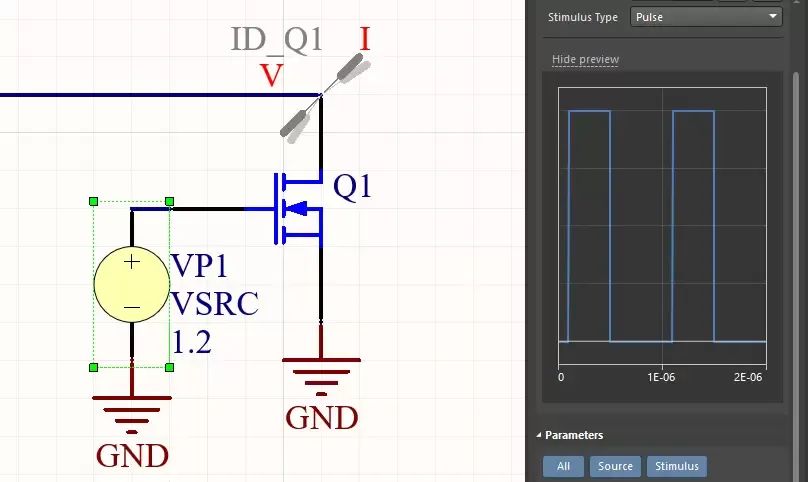

AC仿真方法(激勵響應(yīng)法)

1. 激勵配置:

在負載端注入1A --AC電流源(相位0°),頻率掃描范圍與S參數(shù)法一致。

2.觀測指標:

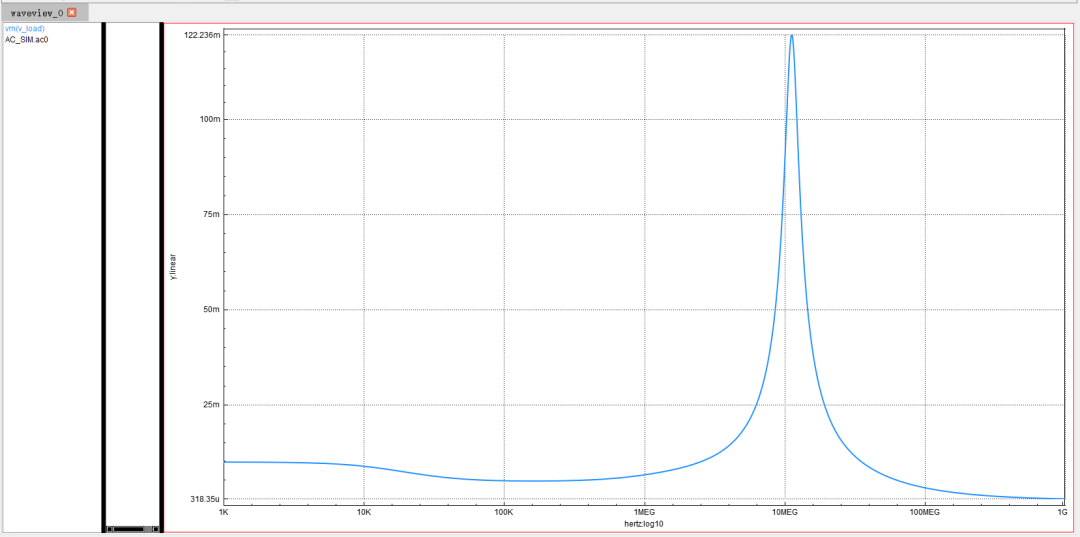

直接測量電源網(wǎng)絡(luò)輸出電壓Vout(f),計算阻抗:

我們將Istimulus設(shè)置為1A,則Zpdn和Vout代數(shù)值相同。

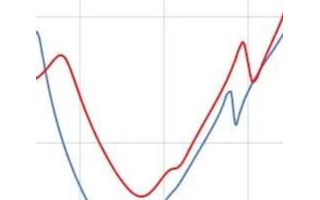

3.查看仿真結(jié)果并與S參數(shù)法的對比:

可以看到,兩者阻抗曲線趨勢一致,諧振點都處于11.2MHz處。

總結(jié)

綜上,AC仿真和S參數(shù)仿真均屬于頻域分析方法,在PCB設(shè)計階段均可使用以上兩種方法,通過掃頻獲取PDN網(wǎng)絡(luò)在不同頻點的阻抗特性,仿真得出以下關(guān)鍵結(jié)果:

(1) 阻抗-頻率曲線:識別反諧振點

(2) 頻域穩(wěn)定性分析:通過相位裕度判定諧振風險

(3) 電容貢獻度分解:量化各去耦電容在不同頻段的阻抗補償作用

-

阻抗

+關(guān)注

關(guān)注

17文章

970瀏覽量

46920 -

仿真

+關(guān)注

關(guān)注

51文章

4222瀏覽量

135186 -

S參數(shù)

+關(guān)注

關(guān)注

2文章

144瀏覽量

46860 -

PDN

+關(guān)注

關(guān)注

0文章

84瀏覽量

22972

原文標題:PDN阻抗特性前仿真分析

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

SPICE中的PDN阻抗仿真與分析

電源分配網(wǎng)絡(luò)(PDN)與目標阻抗的計算方法

PCB特征與PDN性能的關(guān)系

PDN設(shè)計的目的

Altium Designer PDN Analyze簡介

基于可分解的多目標進化算法的PDN阻抗的優(yōu)化

在電源PDN性能的世界里 原來這些因素才至關(guān)重要

具有寄生提取功能的PDN阻抗分析(Q&A)

PDN設(shè)計

利用Altium Designer自帶PDN Analyzer對電源平面進行PDN實例仿真分析,超經(jīng)典!

SPICE中的PDN阻抗仿真設(shè)計

PDN 環(huán)路電感對紋波和總阻抗有何影響?

PDN 元件對阻抗的影響

PDN阻抗仿真方法解析

PDN阻抗仿真方法解析

評論