高速信號(hào)行為、RF信號(hào)傳播和PDN仿真是PCB中最難仿真的部分。在這些電磁現(xiàn)象中,高速信號(hào)傳播和RF傳播需要電磁場(chǎng)求解器工具來(lái)提取有用的結(jié)果。在電路仿真中需要考慮的寄生效應(yīng)和設(shè)計(jì)特定效應(yīng)過(guò)多。盡管我們很努力,但信息實(shí)在太多了,在這兩種情況下難以建模。

PDN仿真有些不同,因?yàn)橐抡娴南嚓P(guān)頻率范圍較低,對(duì)于大多數(shù)設(shè)備而言通常小于10GHz。這意味著可以使用SPICE仿真而不是完整的電磁場(chǎng)求解器仿真,為相對(duì)較小的電路板上支持中速數(shù)字元件的PDN建模。只要電路板足夠小或頻率足夠低以至于可以忽略傳播,就可以通過(guò)SPICE仿真收獲有用的結(jié)果。

如果您以前從未這樣做過(guò),我將展示如何設(shè)置以及您可能會(huì)收獲什么樣的結(jié)果。通過(guò)仿真連接到PDN的負(fù)載元件中的開關(guān)動(dòng)作,可提取某些有用的數(shù)據(jù)來(lái)描述您的PDN,甚至可以計(jì)算其網(wǎng)絡(luò)參數(shù)。在下方我將展示的仿真中,目標(biāo)是提取:

PDN阻抗頻譜

在負(fù)載元件的輸入引腳處測(cè)量的瞬態(tài)響應(yīng)

這些參數(shù)如何隨著電容值的變化而變化

對(duì)相對(duì)低速和小型電路板的限制很重要,我將詳述這到底意味著什么。

設(shè)置PDN仿真

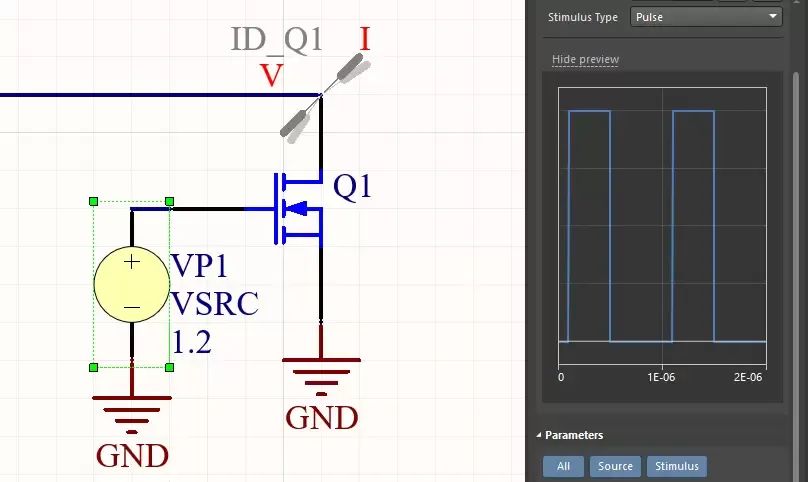

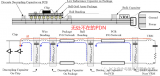

用于描述PDN阻抗和計(jì)算瞬態(tài)響應(yīng)的標(biāo)準(zhǔn)仿真如下圖所示。我已將其放置在Altium 365 Viewer中,以便用戶可以瀏覽設(shè)計(jì)并查看仿真是如何設(shè)置的。點(diǎn)此查看

仿真原理圖是使用一組未按任何特定順序選擇的去耦電容器創(chuàng)建的。起初我一直把這個(gè)數(shù)字保持在較低水平,但稍后我將在的仿真中增加這個(gè)數(shù)字,這樣我們就可以看到增加電容會(huì)如何影響結(jié)果。在繼續(xù)的同時(shí),我們將調(diào)整其他參數(shù)。

等效電路模型

此原理圖是使用Altium Designer中內(nèi)置的仿真通用元件庫(kù)中的元件設(shè)置的。如果不是Altium Designer用戶,您當(dāng)然可以使用SPICE包或其他原理圖編輯器中的通用元件,在任何其他仿真程序中重新創(chuàng)建。正如我在原理圖中指出的那樣,整體仿真由四個(gè)部分組成:

穩(wěn)壓器:這是為PDN供電的穩(wěn)壓器模塊或電路。我已包括其標(biāo)稱輸出電阻和電感。

衰減:這是去耦電容器部分。電容器將ESL和ESR作為分立元件包括在內(nèi),只是為了清楚地顯示它們。請(qǐng)注意,您還可以將這些值定義為屬性面板中這些元件的參數(shù)。

平面:本節(jié)定義了我們的電源/接地平面對(duì)的電容、電感和電阻。本節(jié)中的電感是擴(kuò)散電感,我在另一篇文章中對(duì)此進(jìn)行了描述。

PWR_IN:這是我們負(fù)載IC中的輸入電源部分。我已嘗試通過(guò)電感、引腳封裝電感和輸入端的接觸電阻,對(duì)輸入進(jìn)行建模。這些值因產(chǎn)品和封裝而異,但此處的值是典型的數(shù)量級(jí)數(shù)字。

此等效電路模型需要調(diào)整平面電容(CP1)、平面電感(LP1)和去耦電容的數(shù)量。我們將使用瞬態(tài)分析和交流掃描仿真來(lái)獲得這些數(shù)據(jù)。在此之前,我們應(yīng)該討論上圖所示的NMOS元件。

負(fù)載建模

PWR_IN部分包含一個(gè)負(fù)載模型,它只是一個(gè)開關(guān)n通道MOSFET。在建模負(fù)載并查看PDN上的瞬態(tài)響應(yīng)時(shí),目標(biāo)是檢查PDN如何對(duì)開關(guān)操作做出反應(yīng),然后吸收電流。以這種方式使用快速M(fèi)OSFET,可檢查負(fù)載電流如何根據(jù)某些邏輯輸入突然切換到高電流狀態(tài)。該邏輯輸入通過(guò)在屬性面板中將VSRC元素設(shè)置為脈沖模式以實(shí)現(xiàn)建模目的。我已將升壓和降壓時(shí)間設(shè)置為1ns。盡管1/(升壓時(shí)間)帶寬為500MHz,但這不在超高頻范圍內(nèi),因此信號(hào)可能會(huì)受到平面去耦不良和較大電容器的影響。

仿真中的PWR_IN部分

另一種方法是將電流源設(shè)置為脈沖模式。這將有效地執(zhí)行在低電流狀態(tài)和高電流狀態(tài)之間切換負(fù)載的相同功能。然后,仿真將讀取輸出給MOSFET漏極的電流和電壓。更準(zhǔn)確的方法是放置一個(gè)CMOS緩沖電路來(lái)仿真IO,但這對(duì)于檢查接地反彈或抖動(dòng)等問(wèn)題會(huì)更好,因此我們將其保存以備后用。現(xiàn)在,我們將查看上述模型,以檢查當(dāng)邏輯電路切換狀態(tài)并通過(guò)PDN汲取電流時(shí)會(huì)發(fā)生什么。

結(jié)果

首先,我想看看上述案例的結(jié)果,我們有9個(gè)不同值的并聯(lián)去耦電容器,它們都具有相似的ESL和適中的ESR值。ESR值在這里很重要,因?yàn)樗兄诶絇DN阻抗頻譜,正如我在另一篇關(guān)于PDN阻抗的文章中所展示的那樣。仿真參數(shù)如下:

瞬態(tài)分析:10ns步長(zhǎng),5-10us總仿真時(shí)間

交流掃描:10GHz最大頻率,計(jì)算PDN的|Z|

去耦電容器編號(hào):我將查看上面的9個(gè)電容器模塊和一個(gè)由36個(gè)電容器組成的四倍模塊。

平面電容:低態(tài)(CP1 = 20 pF)和高態(tài)(CP1 = 1 nF)

內(nèi)芯電壓:VDD = 1.8 V

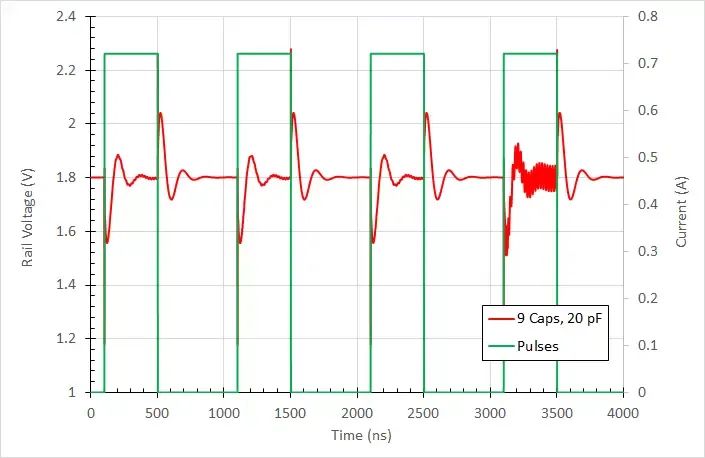

9個(gè)電容器,20pF平面電容

僅使用9個(gè)去耦電容器和20pF平面電容,我們可以看到瞬態(tài)響應(yīng)中具有非常大的波動(dòng),幅度達(dá)到約300 mV,疊加在所需的1.8V內(nèi)芯電壓上。這對(duì)于任何實(shí)際應(yīng)用來(lái)說(shuō)都大到無(wú)法接受,并且會(huì)在輸出上產(chǎn)生大的干擾。此處顯示的數(shù)據(jù)摘自.sdf文件并導(dǎo)出為Excel格式。

使用9個(gè)去耦電容器和20 pF平面電容的瞬態(tài)結(jié)果

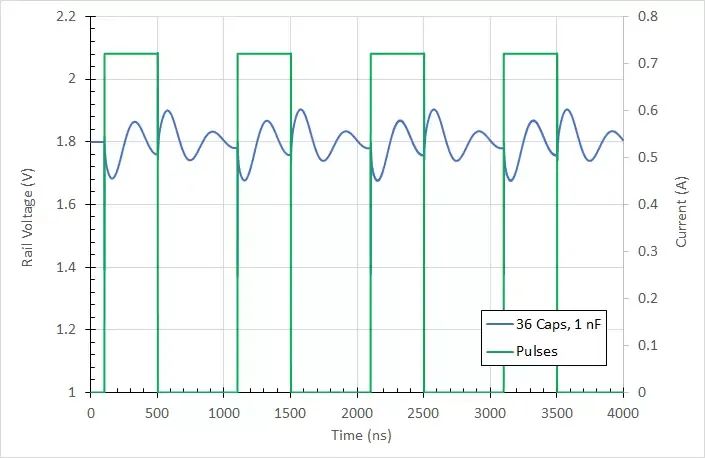

36個(gè)電容,1 nF平面電容

讓我們看看當(dāng)我們將去耦電容器的數(shù)量增加到四倍并將平面電容增加到50倍時(shí)會(huì)發(fā)生什么。此設(shè)計(jì)的新版本和改進(jìn)版本如下所示。基本上,復(fù)制去耦電容器模塊是為了增加該去耦網(wǎng)絡(luò)的等效電容。

結(jié)果清楚地顯示了具有電源/接地平面對(duì)以及更多去耦電容器的好處;隨著電容的增加,瞬態(tài)響應(yīng)的幅度通常會(huì)下降,正如我們所預(yù)料的那樣。當(dāng)我們將電容器數(shù)量增加到四倍并增加平面電容時(shí),PDN上的電源軌響應(yīng)僅以100mV的幅度波動(dòng)。

使用36個(gè)去耦電容器和1 nF平面電容的瞬態(tài)結(jié)果

對(duì)于1.8V電源軌來(lái)說(shuō),這仍然有點(diǎn)大,似乎使用36個(gè)電容器應(yīng)該會(huì)產(chǎn)生更好的結(jié)果。通過(guò)查看每種情況下的阻抗頻譜 ,我們可以了解為什么使用更多電容器不會(huì)產(chǎn)生明顯的阻尼。

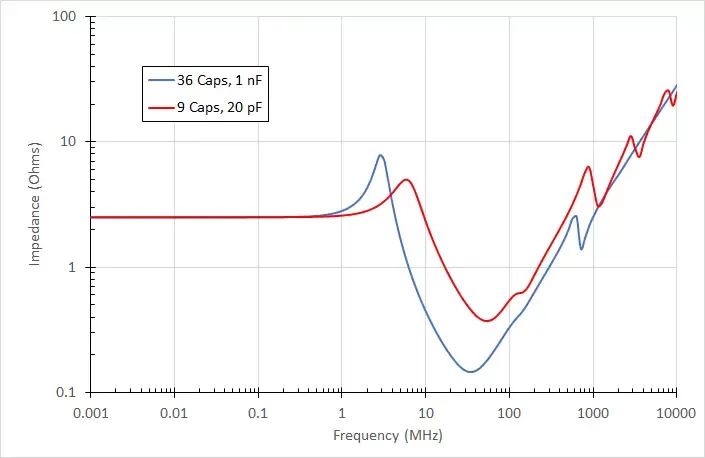

阻抗比較

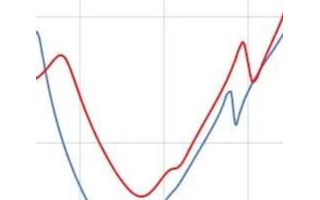

我們還可以取頻域中復(fù)V/I響應(yīng)函數(shù)的比率(AC掃描結(jié)果),然后計(jì)算該比率的大小以獲得PDN阻抗。我們可以看到PDN阻抗仍然偏大,尤其是在1/(升壓時(shí)間)帶寬限制附近。在查看PDN阻抗頻譜時(shí),我們也可以看到其優(yōu)勢(shì),如下所示。下圖將36 decaps/1 nF的當(dāng)前情況與之前的9 decaps/20 pF情況進(jìn)行了比較。

PDN阻抗仿真結(jié)果對(duì)比

請(qǐng)注意,在大約10年內(nèi),我們能達(dá)到低阻抗(100 mOHM)。我們希望這個(gè)低阻抗頻帶更低更寬。我們還有一些在3MHz左右的峰值和630MHz的高頻響應(yīng)。為了解決這些問(wèn)題,我們可能需要更多數(shù)量和多樣性的電容器。我們可以使用一些其他技巧,例如在層過(guò)渡到IC期間增加過(guò)孔數(shù),因?yàn)檫@會(huì)減少PWR_IN輸入級(jí)的總電感,而我們可以在SPICE仿真中反映這一點(diǎn)。

實(shí)際上,在高IO計(jì)數(shù)IC中,具有36個(gè)低ESL/低ESR電容器很常見;當(dāng)然,在單脈沖中會(huì)產(chǎn)生720mA電流的IC中也是如此。事實(shí)上,如果您查看一些使用具有高IO計(jì)數(shù)的高速元件的參考設(shè)計(jì)或評(píng)估產(chǎn)品,您會(huì)發(fā)現(xiàn)36個(gè)去耦電容器是一個(gè)較低的數(shù)字。僅供參考,此脈沖的dI/dt值為720MA/秒(即每秒720兆安!),這是一個(gè)龐大的數(shù)字,需要許多電容器快速放電。在這種薄平面分離電介質(zhì)上嵌入電容材料也會(huì)增加平面電容。

為什么是“小型”電路板?

什么才算是“小型”PDN?請(qǐng)記住,當(dāng)負(fù)載切換時(shí),寬帶電流脈沖被拉入PDN,并且該脈沖以光速沿PDN傳播。將其視為一種傳播信號(hào),但它承載的是能量而不是數(shù)據(jù)。在小型PDN的限制下,我們可以像在傳輸線中一樣忽略傳播效應(yīng)。事實(shí)上,傳輸線比較在這里是恰當(dāng)?shù)模琍DN有時(shí)被描述為使用與傳輸線相同的集總電路模型。

當(dāng)傳輸功率脈沖中具有最大頻率元件的波長(zhǎng)遠(yuǎn)大于標(biāo)稱電路板尺寸時(shí),我們可以忽略傳輸功率必須從穩(wěn)壓器輸出傳播到負(fù)載輸入這一事實(shí)。這與理解為什么我們可以在傳輸線中定義臨界長(zhǎng)度的邏輯相同。一旦設(shè)計(jì)過(guò)大,或者當(dāng)相關(guān)帶寬達(dá)到非常高的頻率時(shí),將需要電磁求解器來(lái)運(yùn)行完整的PDN阻抗仿真并提取瞬態(tài)響應(yīng)。

缺少什么?

精明的設(shè)計(jì)工程師應(yīng)該注意到一些重要的事情:我們沒有將耗散包括在平面電容中!這引用了介電常數(shù)的虛部,通過(guò)將一些與平面電容串聯(lián)的電阻相加來(lái)實(shí)現(xiàn)建模目的。它在傳輸線的阻抗方程中基本上起著與G相同的作用。此電阻的大小需要一些額外的計(jì)算,這將取決于分隔平面層的介電材料的損耗量。在下一篇關(guān)于電源平面諧振的文章中,我們將能夠看到層壓板中高損耗切線的有益影響。

我們還能仿真什么?

上方結(jié)果清楚地顯示了增加電容如何降低PDN阻抗并有助于穩(wěn)定內(nèi)芯電壓。上述電容器僅為隨機(jī)選擇,并非基于針對(duì)特定頻率范圍的全面分析。如果我們通過(guò)這項(xiàng)練習(xí)并在更寬的帶寬上降低PDN阻抗,就能收獲更好的結(jié)果。

我們可以在SPICE中仿真的其他一些點(diǎn)包括:

我們已經(jīng)通過(guò)計(jì)算輸入和輸出端口的阻抗,得出PDN的S參數(shù)

拉入PDN的任何電流脈沖的脈沖響應(yīng)

PDN中多軌之間的傳輸阻抗

額外電感影響,例如在電源引腳上添加鐵氧體;我們將在即將發(fā)表的文章中對(duì)此進(jìn)行探討

將旁路電容器直接添加到負(fù)載的電源輸入中(與Q1并聯(lián))

Altium Designer中的內(nèi)置SPICE包可以幫助您執(zhí)行一系列仿真,包括PDN仿真。當(dāng)您準(zhǔn)備將這些文件發(fā)布給您的協(xié)作者進(jìn)行更高級(jí)的仿真時(shí),Altium 365平臺(tái)可以輕松協(xié)作和共享您的項(xiàng)目。您可以在一個(gè)軟件包中找到設(shè)計(jì)和生產(chǎn)高級(jí)電子產(chǎn)品所需的一切。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4351文章

23405瀏覽量

406615 -

仿真

+關(guān)注

關(guān)注

51文章

4234瀏覽量

135290 -

RF

+關(guān)注

關(guān)注

65文章

3170瀏覽量

168491 -

SPICE

+關(guān)注

關(guān)注

6文章

190瀏覽量

43361 -

PDN

+關(guān)注

關(guān)注

0文章

84瀏覽量

22994

原文標(biāo)題:【技術(shù)博客】SPICE中的PDN阻抗仿真與分析

文章出處:【微信號(hào):AltiumChina,微信公眾號(hào):Altium】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

SPICE中的PDN阻抗仿真與分析

PDN阻抗仿真方法解析

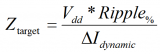

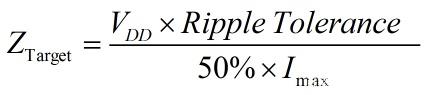

電源分配網(wǎng)絡(luò)(PDN)與目標(biāo)阻抗的計(jì)算方法

multisim中添加spice模型 仿真 AD8304

AD8137 SPICE仿真錯(cuò)誤

電源旁路之SPICE仿真與現(xiàn)實(shí)的差距

淺析SPICE仿真軟件

請(qǐng)問(wèn)在spectre仿真器中怎么去使用spice模型?

PDN設(shè)計(jì)的目的

PDN設(shè)計(jì)

利用Altium Designer自帶PDN Analyzer對(duì)電源平面進(jìn)行PDN實(shí)例仿真分析,超經(jīng)典!

PDN 環(huán)路電感對(duì)紋波和總阻抗有何影響?

PDN 元件對(duì)阻抗的影響

SPICE中的PDN阻抗仿真設(shè)計(jì)

SPICE中的PDN阻抗仿真設(shè)計(jì)

評(píng)論