對于硬件設計人員來說,了解PDN的每個元件的諧振頻率(例如,體旁路和去耦電容,平面電容和互連電感)及其對PI的影響非常重要。具有差的PI的PCB(例如,在50MHz及更高時具有高PDN阻抗)引起由PDN供電的信號的SSN和抖動。本文演示了PCB上PDN阻抗與SSN之間的關系。

分析和結果

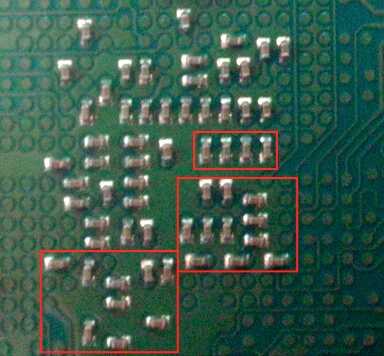

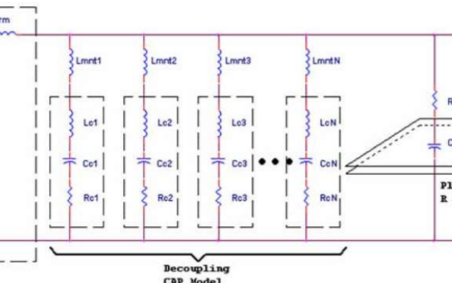

原型如圖所示圖1已實施。該處理器帶有外部40MHz晶體振蕩器,有三個主要接口:320Mbps數據或160MHz時鐘速率的DDR2 SDRAM,80MHz時鐘速率的并行閃存和通用I/O.所有這些組件都從降壓轉換器獲取功率。在PCB上,每個電源引腳上的處理器BGA正下方放置0.1μF去耦電容,如圖2所示。

圖1DUT的方框圖

圖2處理器下的去耦電容放置

為了顯示PDN阻抗和SSN之間的關系,在原型PCB上嘗試了表I中列出的兩個測試用例。在測試用例A中,卸載了一部分去耦電容(如圖2中的紅框所示)。另一方面,所有去耦電容都加載到測試用例B中。

表I.正在研究的去耦條件

| 測試用例 | 條件 |

| A | 一部分去耦電容器被卸載 |

| B | 所有去耦電容都加載 |

首先,比較10MHz至500MHz的PDN阻抗曲線(使用Mentor Graphics Hyperlynx進行仿真)。由于Vcc和地之間的去耦電容量較低,測試用例A的阻抗高于情況B.

圖3PDN阻抗圖

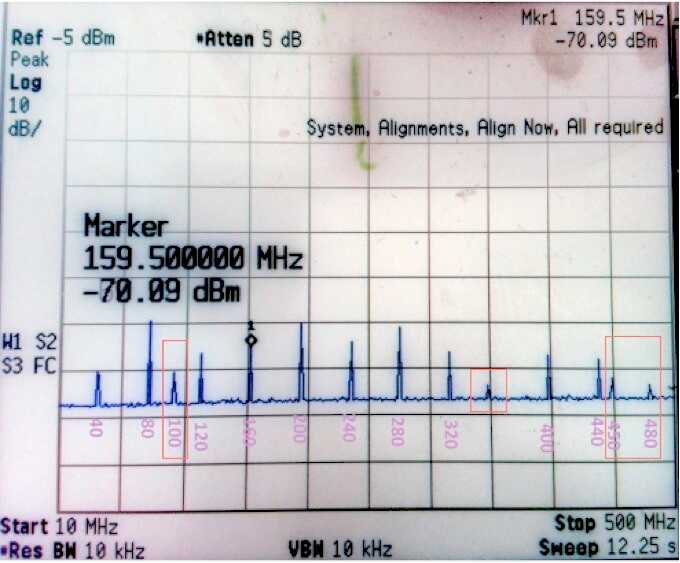

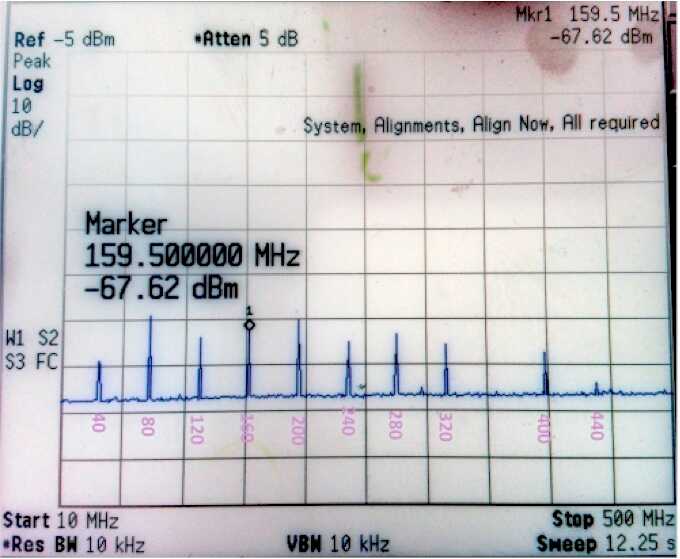

其次,兩個測試案例比較了Vcc的功率譜(使用頻譜分析儀通過交流耦合探測),范圍從10MHz到500MHz 。參考情況B(圖4b),觀察到的尖峰主要由40MHz晶體振蕩器,160MHz DDR2和80MHz閃存接口以及相關內部處理器PLL的諧波貢獻。但在情況A中,由于較低的總去耦電容,Vcc頻譜中出現額外的尖峰(圖4a中用紅色框出)。

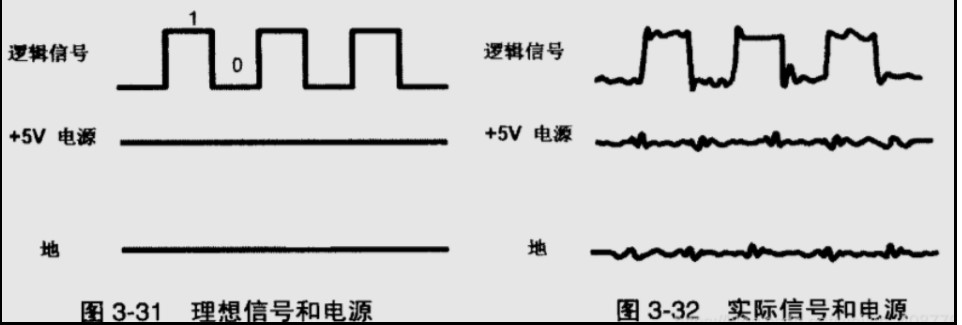

Vcc上的噪聲是由PDN阻抗與瞬態之間的相互作用引起的IC內所有同步切換信號的電流,即SSN。當更多的去耦電容正確放置在Vcc線上時,可以抑制SSN和Vcc噪聲。

圖4a電源測試用例A的Vcc頻譜

圖4b測試用例的Vcc功率譜B

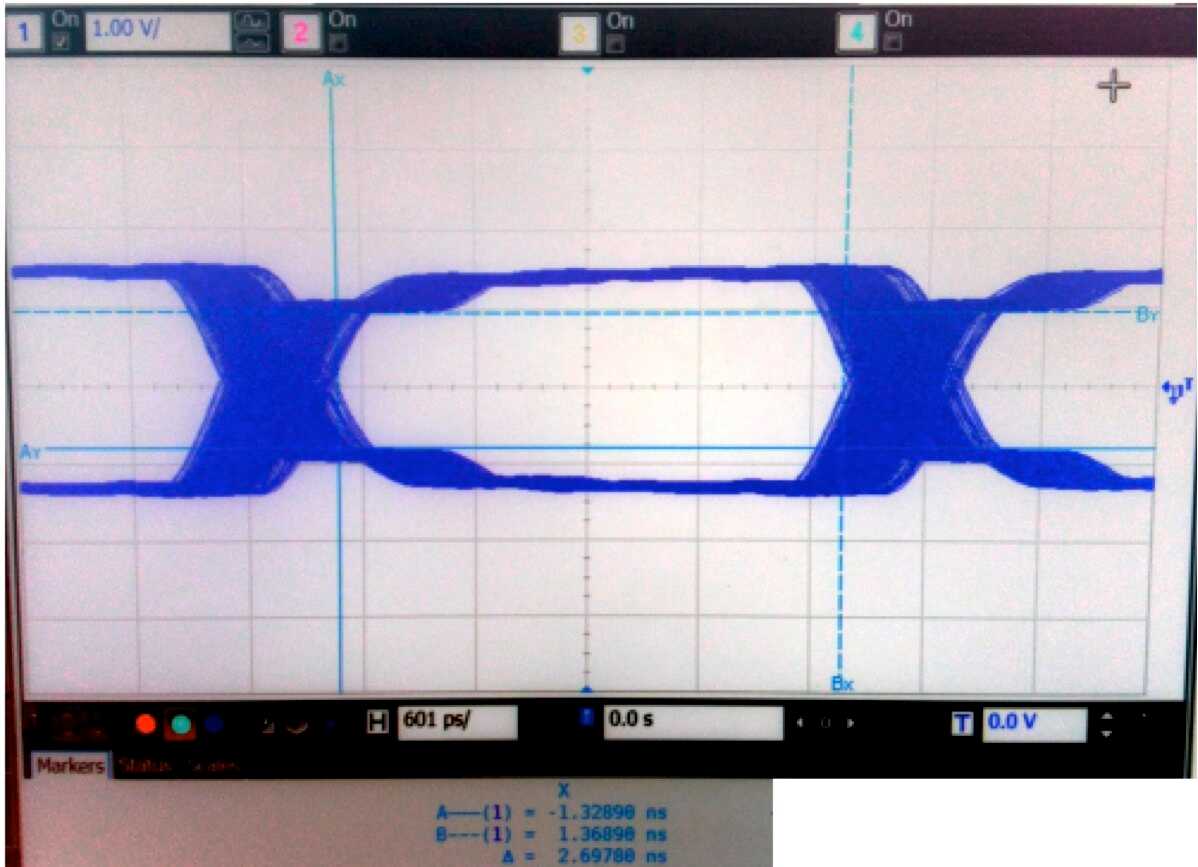

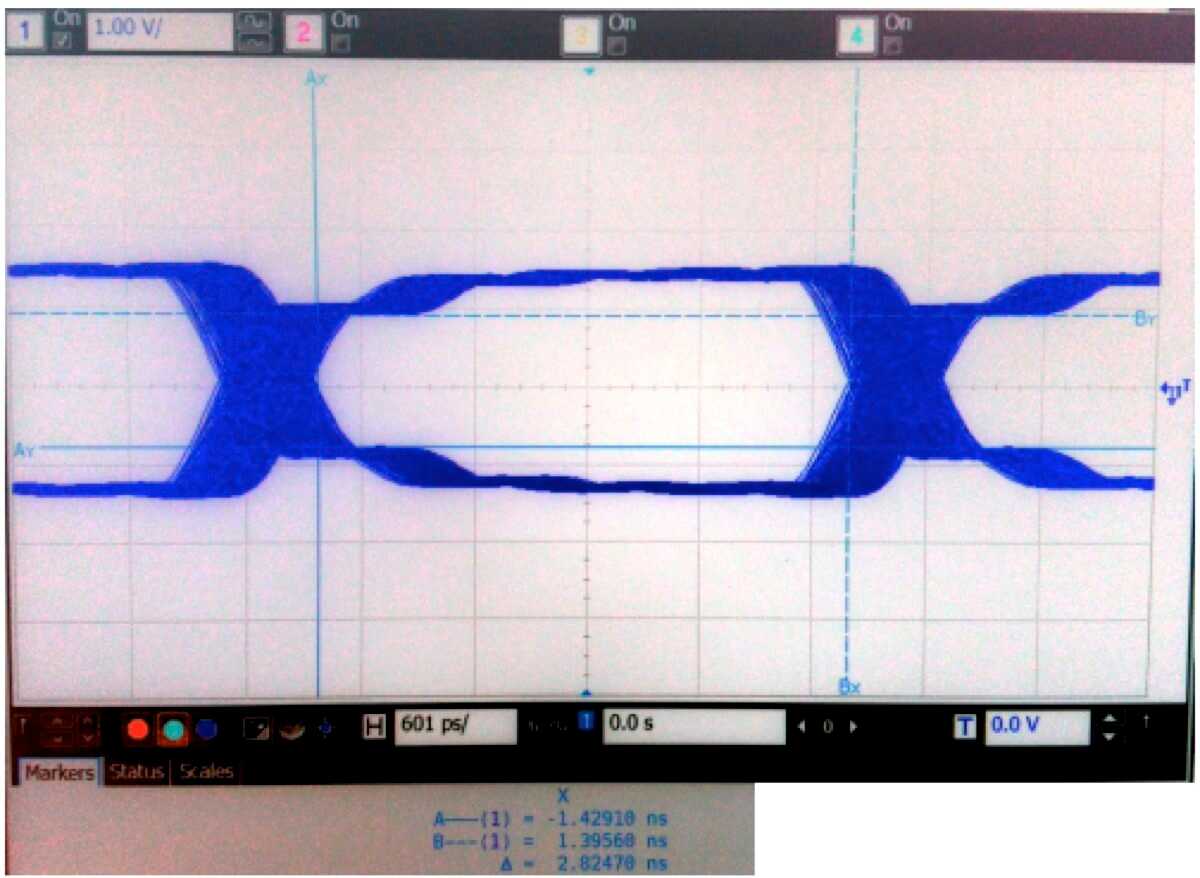

第三,比較兩個測試用例的以160MHz(3.125ns單位間隔)運行的DDR2時鐘信號的眼圖開度。在情況B(2.825ns)與情況A(2.698ns)的情況下,較大的眼寬表明抑制Vcc噪聲有助于減少處理器發送的信號中的抖動。

圖5a測試用例A的DDR2時鐘信號眼圖

圖5b測試案例B的DDR2時鐘信號眼圖

結論

在這個實際實驗中證明了PDN阻抗對SSN和抖動的影響。至關重要的是,PCB PDN必須以嚴格的方式實施,以確保質量,穩健性和功能性。

-

PCB打樣

+關注

關注

17文章

2972瀏覽量

22364 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28452 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43753

發布評論請先 登錄

配電網絡柱上開關監測系統應用方案

電源系統優化——深入解讀優化高速數據轉換器的配電網絡

簡單總結一些造成電源完整性的問題

什么是電源和信號完整性?

基于最小路的配電網可靠性評估

電源完整性之同步開關噪聲SSN

電源和信號完整性的分析與測試

配電網是什么意思 配電網電壓等級

電源完整性分析參考解決方案

電源完整性和配電網絡阻抗對同步開關噪聲的影響

電源完整性和配電網絡阻抗對同步開關噪聲的影響

評論