在今年的IEEE IMW 2024活動中,三星DRAM業務的資深副總裁Lee指出,已有多家科技巨頭如三星成功制造出16層3D DRAM,其中美光更是發展至8層水平。

然而,他也強調,現階段三星正致力于探索3D DRAM及垂直堆疊單元陣列晶體管(VS-CAT)的可行性,暫無大量量產的計劃。值得注意的是,Lee曾在美光擔任過未來存儲芯片的研究工作,后于去年加入三星。

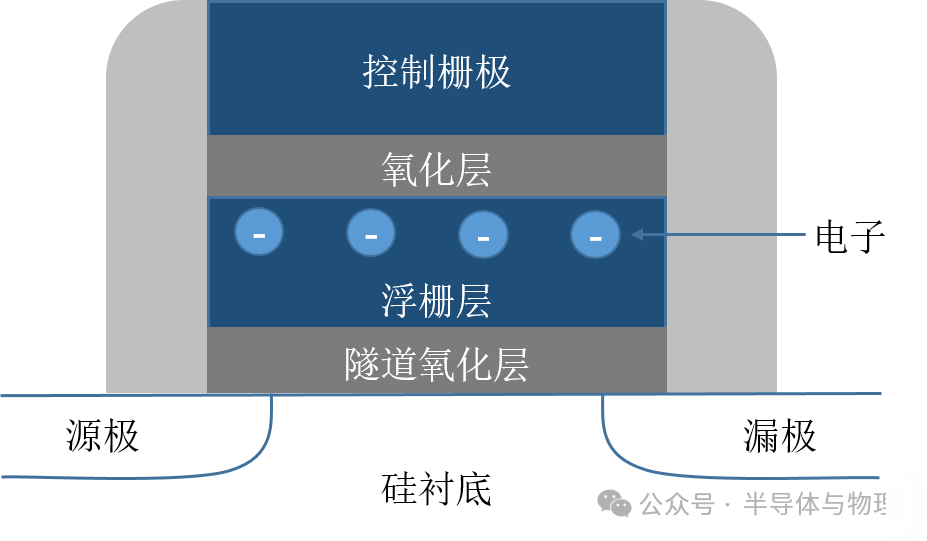

VS-CAT與傳統DRAM有所區別,其采用雙硅晶圓設計,外圍設備和邏輯/存儲單元獨立連接。若將外圍設備直接連接至單元層,會導致表面積過大。

因此,外圍設備通常在另一片晶圓上制造,再與存儲單元通過鍵合方式連接。預計3D DRAM將采用晶圓對晶圓(wafer-to-wafer)等混合鍵合技術進行生產,此項技術已廣泛運用于NAND和CMOS圖像傳感器的制造過程。

此外,三星還計劃將背面供電網絡(BSPDN)技術引入3D DRAM領域。

同時,三星亦在研究垂直溝道晶體管(VCT)。VCT又稱4F2,較之先前的6F2技術,可大幅降低晶粒表面積,最高可達30%。據悉,原型產品有望于明年問世。

-

DRAM

+關注

關注

40文章

2342瀏覽量

185165 -

硅晶圓

+關注

關注

4文章

274瀏覽量

21165 -

三星

+關注

關注

1文章

1685瀏覽量

32360

發布評論請先 登錄

預期提前,鎧俠再次加速,3D NAND準備沖擊1000層

三星在4nm邏輯芯片上實現40%以上的測試良率

三星電子否認1b DRAM重新設計報道

三星否認重新設計1b DRAM

【半導體存儲】關于NAND Flash的一些小知識

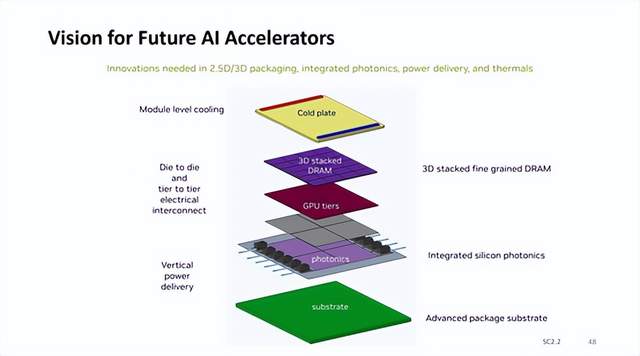

英偉達AI加速器新藍圖:集成硅光子I/O,3D垂直堆疊 DRAM 內存

三星電子研發16層3D DRAM芯片及垂直堆疊單元晶體管

三星電子研發16層3D DRAM芯片及垂直堆疊單元晶體管

評論