一、引言

隨著信息技術(shù)的飛速發(fā)展,高速數(shù)據(jù)傳輸已成為現(xiàn)代通信和數(shù)據(jù)處理系統(tǒng)的核心。高速串行收發(fā)器(High-Speed Serial Transceiver)作為實(shí)現(xiàn)高速數(shù)據(jù)傳輸?shù)年P(guān)鍵部件,其性能優(yōu)劣直接影響到整個(gè)系統(tǒng)的性能。本文將對(duì)高速串行收發(fā)器的原理進(jìn)行詳細(xì)介紹,并探討其芯片設(shè)計(jì)的關(guān)鍵技術(shù)和挑戰(zhàn)。

二、高速串行收發(fā)器原理

高速串行收發(fā)器是一種用于在數(shù)字系統(tǒng)中進(jìn)行高速數(shù)據(jù)傳輸?shù)碾娐贰K饕砂l(fā)送器(Transmitter)、接收器(Receiver)和時(shí)鐘恢復(fù)電路(Clock Recovery Circuit)三個(gè)部分組成。

發(fā)送器

發(fā)送器的主要功能是將并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù),并通過高速串行鏈路進(jìn)行傳輸。具體實(shí)現(xiàn)過程如下:

(1)數(shù)據(jù)編碼:發(fā)送器首先將輸入的并行數(shù)據(jù)進(jìn)行編碼,通常采用的編碼方式有8B/10B編碼、64B/66B編碼等。編碼的目的是為了增加數(shù)據(jù)的冗余度,提高數(shù)據(jù)的抗干擾能力和傳輸可靠性。

(2)串行化:編碼后的數(shù)據(jù)被送入串行化器(Serializer),將數(shù)據(jù)從并行形式轉(zhuǎn)換為串行形式。串行化器通常由多個(gè)移位寄存器組成,每個(gè)移位寄存器對(duì)應(yīng)一個(gè)數(shù)據(jù)位。在時(shí)鐘信號(hào)的控制下,移位寄存器將數(shù)據(jù)按位依次輸出,形成串行數(shù)據(jù)流。

(3)差分驅(qū)動(dòng):為了提高信號(hào)的傳輸距離和抗干擾能力,發(fā)送器通常采用差分驅(qū)動(dòng)方式將串行數(shù)據(jù)流轉(zhuǎn)換為差分信號(hào)。差分信號(hào)由一對(duì)相位相反、幅度相等的信號(hào)組成,可以有效地抑制共模噪聲和電磁干擾。

接收器

接收器的主要功能是將接收到的串行差分信號(hào)轉(zhuǎn)換為并行數(shù)據(jù),并進(jìn)行數(shù)據(jù)解碼和校驗(yàn)。具體實(shí)現(xiàn)過程如下:

(1)差分接收:接收器首先通過差分接收器(Differential Receiver)將接收到的差分信號(hào)轉(zhuǎn)換為單端信號(hào)。差分接收器利用差分信號(hào)的相位差和幅度差來抑制共模噪聲和電磁干擾,提高信號(hào)的信噪比。

(2)解串行化:解串行化器(Deserializer)將接收到的單端信號(hào)從串行形式轉(zhuǎn)換為并行形式。解串行化器通常由多個(gè)移位寄存器組成,每個(gè)移位寄存器對(duì)應(yīng)一個(gè)數(shù)據(jù)位。在時(shí)鐘信號(hào)的控制下,移位寄存器將數(shù)據(jù)按位依次讀取,形成并行數(shù)據(jù)流。

(3)數(shù)據(jù)解碼和校驗(yàn):解碼器將并行數(shù)據(jù)流進(jìn)行解碼,還原出原始數(shù)據(jù)。同時(shí),接收器還會(huì)對(duì)數(shù)據(jù)進(jìn)行校驗(yàn),以檢測(cè)數(shù)據(jù)傳輸過程中是否出現(xiàn)錯(cuò)誤。如果檢測(cè)到錯(cuò)誤,接收器會(huì)采取相應(yīng)的措施進(jìn)行糾正或報(bào)告給上層系統(tǒng)。

時(shí)鐘恢復(fù)電路

時(shí)鐘恢復(fù)電路是高速串行收發(fā)器中的重要組成部分,它負(fù)責(zé)從接收到的串行數(shù)據(jù)流中提取出發(fā)送端的時(shí)鐘信號(hào),并將其同步到接收端的時(shí)鐘域中。時(shí)鐘恢復(fù)電路的實(shí)現(xiàn)方式有多種,如基于相位鎖定環(huán)(PLL)的時(shí)鐘恢復(fù)電路、基于延遲線(DLL)的時(shí)鐘恢復(fù)電路等。時(shí)鐘恢復(fù)電路的性能直接影響到高速串行收發(fā)器的數(shù)據(jù)傳輸速率和誤碼率。

三、高速串行收發(fā)器芯片設(shè)計(jì)

高速串行收發(fā)器的芯片設(shè)計(jì)是一個(gè)復(fù)雜而精細(xì)的過程,需要考慮到信號(hào)的傳輸速率、功耗、抗噪聲干擾能力、芯片面積等多個(gè)方面。下面將介紹高速串行收發(fā)器芯片設(shè)計(jì)的一些關(guān)鍵技術(shù)和挑戰(zhàn)。

高速數(shù)字電路設(shè)計(jì)技術(shù)

高速串行收發(fā)器的芯片設(shè)計(jì)需要采用高速數(shù)字電路設(shè)計(jì)技術(shù),以實(shí)現(xiàn)高速、低功耗和高抗干擾的性能要求。這包括優(yōu)化電路結(jié)構(gòu)、選擇合適的器件類型、降低電路噪聲和功耗等方面。同時(shí),還需要考慮到芯片面積和成本等因素,進(jìn)行合理的電路和布局設(shè)計(jì)。

時(shí)鐘設(shè)計(jì)

時(shí)鐘設(shè)計(jì)是高速串行收發(fā)器芯片設(shè)計(jì)中的關(guān)鍵環(huán)節(jié)之一。時(shí)鐘信號(hào)的穩(wěn)定性和精度直接影響到數(shù)據(jù)傳輸?shù)乃俾屎驼`碼率。在時(shí)鐘設(shè)計(jì)中,需要選擇合適的時(shí)鐘源、設(shè)計(jì)穩(wěn)定的時(shí)鐘電路、優(yōu)化時(shí)鐘信號(hào)的傳輸路徑等方面。同時(shí),還需要考慮到時(shí)鐘信號(hào)的抖動(dòng)和相位噪聲等因素,以提高時(shí)鐘信號(hào)的穩(wěn)定性和精度。

差分驅(qū)動(dòng)和接收技術(shù)

差分驅(qū)動(dòng)和接收技術(shù)是高速串行收發(fā)器中的關(guān)鍵技術(shù)之一。差分驅(qū)動(dòng)器通過將串行數(shù)據(jù)轉(zhuǎn)換為差分信號(hào),并通過差分線路發(fā)送到傳輸介質(zhì)上,可以提高信號(hào)的傳輸距離和抗干擾能力。差分接收器則通過差分線路接收差分信號(hào),并將其轉(zhuǎn)換為單端信號(hào)進(jìn)行處理。在差分驅(qū)動(dòng)和接收技術(shù)中,需要優(yōu)化差分信號(hào)的幅度、相位和傳輸路徑等方面,以提高信號(hào)的傳輸質(zhì)量和穩(wěn)定性。

功耗管理

功耗管理是高速串行收發(fā)器芯片設(shè)計(jì)中需要重點(diǎn)考慮的問題之一。為了降低功耗,可以采用多種技術(shù)手段,如降低電源電壓、優(yōu)化電路結(jié)構(gòu)、采用低功耗器件等。同時(shí),還需要考慮到功耗與性能之間的平衡關(guān)系,以實(shí)現(xiàn)低功耗下的高性能傳輸。

可靠性設(shè)計(jì)

可靠性設(shè)計(jì)是高速串行收發(fā)器芯片設(shè)計(jì)中不可或缺的一部分。為了提高芯片的可靠性,可以采用多種技術(shù)手段,如冗余設(shè)計(jì)、熱備份設(shè)計(jì)、故障檢測(cè)與恢復(fù)機(jī)制等。這些技術(shù)手段可以在芯片出現(xiàn)故障或異常情況時(shí),提供有效的保障措施,確保數(shù)據(jù)傳輸?shù)姆€(wěn)定性和可靠性。

測(cè)試與驗(yàn)證

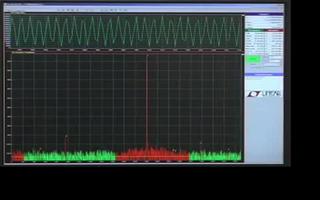

高速串行收發(fā)器的測(cè)試與驗(yàn)證是芯片設(shè)計(jì)流程中不可或缺的一部分。測(cè)試和驗(yàn)證過程旨在確保芯片在各種工作條件下都能正常工作,并滿足設(shè)計(jì)規(guī)格和要求。這包括單元測(cè)試、集成測(cè)試、系統(tǒng)測(cè)試等多個(gè)階段。在測(cè)試過程中,需要使用各種測(cè)試設(shè)備和工具,如示波器、信號(hào)發(fā)生器、誤碼率測(cè)試儀等,對(duì)芯片的性能進(jìn)行全面的評(píng)估和驗(yàn)證。

協(xié)議支持

高速串行收發(fā)器通常需要支持多種通信協(xié)議,如PCI Express、SerDes、Ethernet等。因此,在芯片設(shè)計(jì)中,需要考慮到不同協(xié)議之間的兼容性和互操作性。這包括設(shè)計(jì)靈活的接口電路、實(shí)現(xiàn)多種協(xié)議之間的切換和配置等。通過支持多種協(xié)議,高速串行收發(fā)器可以適應(yīng)更廣泛的應(yīng)用場(chǎng)景,提高芯片的通用性和市場(chǎng)競(jìng)爭(zhēng)力。

四、高速串行收發(fā)器芯片設(shè)計(jì)的挑戰(zhàn)

在高速串行收發(fā)器芯片設(shè)計(jì)中,面臨著一系列挑戰(zhàn)。首先,隨著數(shù)據(jù)傳輸速率的不斷提高,對(duì)芯片的帶寬和信號(hào)處理能力提出了更高的要求。這要求設(shè)計(jì)人員在電路結(jié)構(gòu)、器件選型、時(shí)鐘設(shè)計(jì)等方面進(jìn)行深入研究和優(yōu)化。其次,隨著應(yīng)用領(lǐng)域的不斷擴(kuò)展,對(duì)芯片的功耗、可靠性、抗干擾能力等方面也提出了更高的要求。這要求設(shè)計(jì)人員在功耗管理、可靠性設(shè)計(jì)、差分驅(qū)動(dòng)和接收技術(shù)等方面進(jìn)行深入研究和改進(jìn)。此外,隨著市場(chǎng)競(jìng)爭(zhēng)的加劇,對(duì)芯片的成本和上市時(shí)間也提出了更高的要求。這要求設(shè)計(jì)團(tuán)隊(duì)在保持高性能的同時(shí),還需要注重成本控制和項(xiàng)目管理。

五、結(jié)論

高速串行收發(fā)器作為現(xiàn)代通信和數(shù)據(jù)處理系統(tǒng)的核心部件,其性能優(yōu)劣直接影響到整個(gè)系統(tǒng)的性能。本文對(duì)高速串行收發(fā)器的原理和芯片設(shè)計(jì)進(jìn)行了詳細(xì)介紹,并探討了其面臨的關(guān)鍵技術(shù)和挑戰(zhàn)。通過深入研究和優(yōu)化電路結(jié)構(gòu)、時(shí)鐘設(shè)計(jì)、差分驅(qū)動(dòng)和接收技術(shù)等方面,可以實(shí)現(xiàn)高速、低功耗、高可靠性的傳輸性能,滿足不斷增長的數(shù)據(jù)傳輸需求。同時(shí),通過支持多種通信協(xié)議和考慮成本和時(shí)間因素,可以提高芯片的通用性和市場(chǎng)競(jìng)爭(zhēng)力。未來,隨著技術(shù)的不斷進(jìn)步和應(yīng)用領(lǐng)域的不斷擴(kuò)展,高速串行收發(fā)器將繼續(xù)發(fā)揮重要作用,為現(xiàn)代通信和數(shù)據(jù)處理系統(tǒng)提供強(qiáng)有力的支持。

-

接收器

+關(guān)注

關(guān)注

15文章

2557瀏覽量

73242 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1058瀏覽量

55435 -

串行收發(fā)器

+關(guān)注

關(guān)注

0文章

14瀏覽量

9582

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA設(shè)計(jì)之GTP、GTX、GTH以及GTZ四種串行高速收發(fā)器

求助FPGA高速串行收發(fā)器,輸出12.5Gbps的信號(hào)要用什么電平 ...

FPGA高速收發(fā)器設(shè)計(jì)要遵循哪些原則?

具有高速CAN收發(fā)器的MC33907電源系統(tǒng)基礎(chǔ)芯片的應(yīng)用

FPGA高速收發(fā)器的設(shè)計(jì)原則有哪些?

串行異步收發(fā)器相關(guān)資料推薦

FPGA高速收發(fā)器設(shè)計(jì)原則

通用串行總線收發(fā)器MIC2550及其應(yīng)用

高速ADC與高速串行收發(fā)器

Xilinx 7系列FPGA GTZ高速串行收發(fā)器性能與兼容性演示

Virtex-7 2000T GTX收發(fā)器實(shí)現(xiàn)高速串行性能

基于Virtex-5 RocketI0TM GTP收發(fā)器實(shí)現(xiàn)串行高速接口的開發(fā)應(yīng)用

高速串行收發(fā)器的重要概念和注意事項(xiàng)

Logos系列FPGA高速串行收發(fā)器(HSST)用戶指南

高速串行收發(fā)器原理及芯片設(shè)計(jì)

高速串行收發(fā)器原理及芯片設(shè)計(jì)

評(píng)論