系統(tǒng)設計領域充滿變數(shù),確保信號完好無損地到達目的地還只是冰山一角。隨著封裝密度不斷提高、PCB 線路不斷細化以及頻率不斷飆升,這些錯綜復雜的問題也在不斷演變,需要綜合運用電氣、機械、電磁和熱動力學方面的專業(yè)知識。

為了應對日益增長的復雜性和細微差別,系統(tǒng)需要達到最佳性能。而要實現(xiàn)這一目標,設計人員在發(fā)揮聰明才智的同時,還要借助機器的計算能力。遺憾的是,不同學科猶如一個個孤島彼此分離,阻礙了專家之間的有效合作。要滿足這些激增的需求,系統(tǒng)級優(yōu)化已不再是一種“奢侈選項”,而是“必不可少”。

手動工作流程包括構(gòu)建、測試、原型驗證、改進和最終制造,這給設計優(yōu)化造成了很大的阻礙。目前的設計優(yōu)化方法在很大程度上依賴于設計人員的直覺,他們通過創(chuàng)建原型和運行仿真來評估設計是否符合目標。然而,如今的電子設計開始追求更強的性能、更高的復雜性和更緊湊的外形,單憑人類的直覺已經(jīng)難以應對優(yōu)化挑戰(zhàn)。我們需要先進的優(yōu)化方法來實現(xiàn)日益復雜的現(xiàn)代設計。

基于 AI 的優(yōu)化

Cadence 推出了 Optimality Intelligent System Explorer,這是一項全新的優(yōu)化技術,利用 AI 幫助設計人員應對現(xiàn)代設計挑戰(zhàn)。該技術具有多學科設計分析優(yōu)化 (MDAO) 功能,可無縫執(zhí)行從集成電路到封裝,乃至電路板的系統(tǒng)級優(yōu)化。將多物理場分析工具與 Optimality Explorer 集成,確保了預期結(jié)果萬無一失。自動化大大加快了優(yōu)化過程,工程師和設計師可以更輕松、更高效地實現(xiàn)目標。

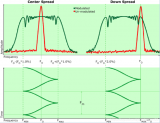

Optimality Explorer 工作流程可指定輸入?yún)?shù),優(yōu)化系統(tǒng)標準,并使用多物理場分析工具進行仿真。它能自動完成優(yōu)化過程,生成優(yōu)化設計和最終曲線。用戶可以優(yōu)化回波損耗、插入損耗、串擾隔離等參數(shù)以及眼圖、抖動和比特誤碼率 (BER) 等系統(tǒng)標準。

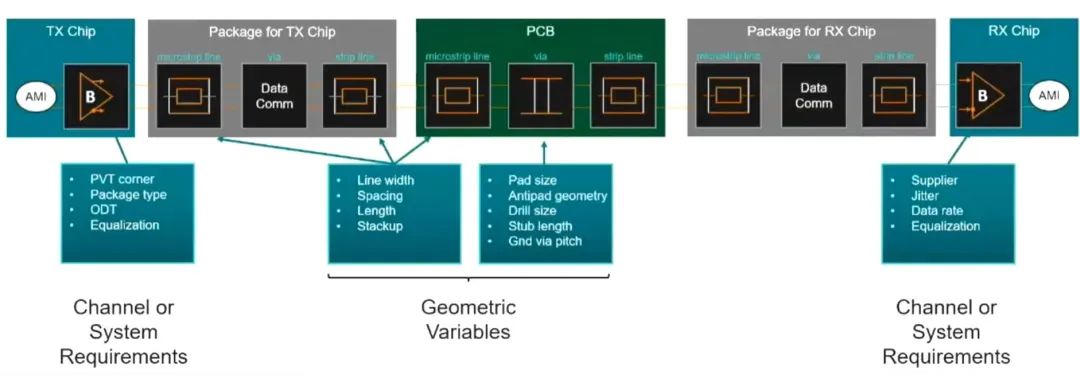

為實現(xiàn)有效優(yōu)化,設計人員必須考慮線寬、間距、線長、走線堆疊、焊盤尺寸、隔離焊盤幾何形狀、鉆孔尺寸和過孔 stub 長度等幾何變量。在創(chuàng)建模型時,還必須考慮制程 (Process)、電壓 (Voltage) 和溫度 (Temperature) 組合,片內(nèi)端接 (on-die termination, ODT),抖動均衡等參數(shù)。

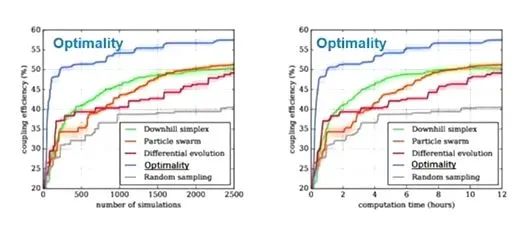

Optimality Explorer 旨在幫助設計人員進行無縫的設計優(yōu)化,無需用戶干預。其算法實現(xiàn)了優(yōu)化過程的自動化,可提供流暢、便捷的用戶體驗。與傳統(tǒng)方法相比,它能在不到 500 次的迭代中實現(xiàn)顯著優(yōu)化,加快設計收斂。Optimality Explorer 被稱為 AI 驅(qū)動的設計同步多學科分析與優(yōu)化工具。

Optimality Explorer 可高效、準確地仿真和優(yōu)化復雜的 3D layout,處理傳統(tǒng)上被認為具有挑戰(zhàn)性的優(yōu)化方案。該工具中包含用于 PC 封裝互連的場求解器,可處理各種通常被視為具有挑戰(zhàn)性的優(yōu)化方案,如最大化交叉網(wǎng)格覆銅。

優(yōu)化參數(shù)和注意事項

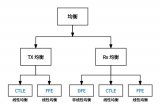

例如,在系統(tǒng)通信信道中,有發(fā)射器、接收器、PCB 互連、封裝和中介層。這些器件經(jīng)過抽象化,用作發(fā)射器-接收器的 IBIS-AMI 模型,發(fā)射器-接收器之間是走線和過孔。

為確保最佳信道性能,必須考慮各種幾何變量,如線寬、間距、線長、走線堆疊、焊盤尺寸、隔離焊盤幾何形狀、鉆孔尺寸和過孔 stub 長度。創(chuàng)建模型時還應考慮 制程 (Process)、電壓 (Voltage) 和溫度 (Temperature) 組,片內(nèi)端接 (on-die termination, ODT) 和抖動均衡等參數(shù)。

在優(yōu)化過程中,必須指定需要優(yōu)化的設計參數(shù)和想達到的優(yōu)化目標。此外,還必須創(chuàng)建額外的代理模型 (surrogate model),以有效優(yōu)化這些參數(shù)。

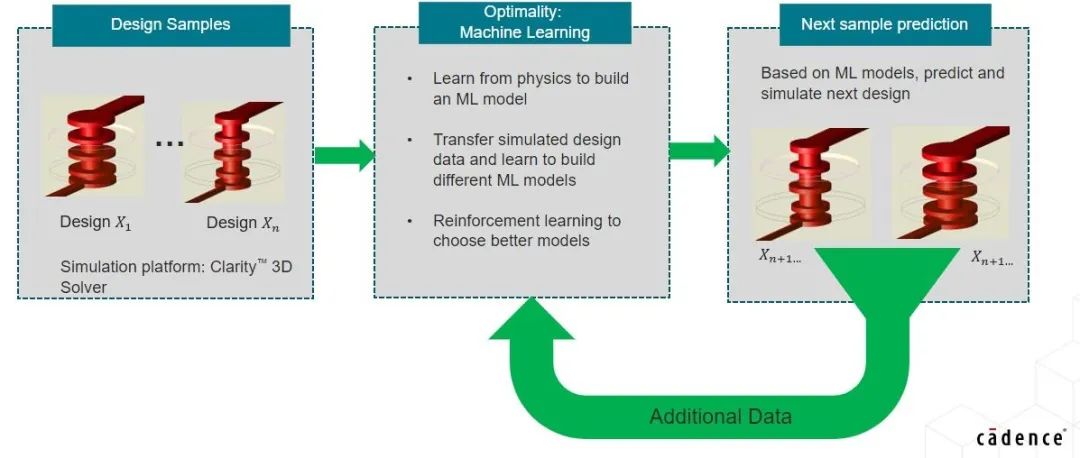

Optimality Explorer 基于隨機搜索生成的初始數(shù)據(jù)集,構(gòu)建并訓練機器學習模型。它會不斷分析仿真結(jié)果,更新設計變量,計算目標函數(shù)和約束條件,直到達到停止標準和收斂為止。

Optimality Explorer 旨在簡化設計人員的優(yōu)化過程,尤其是在需要考慮許多可調(diào)參數(shù)的情況下。其算法實現(xiàn)了優(yōu)化過程的自動化,無需用戶干預,并且易于使用。

傳統(tǒng)方法需要 2500 次以上的迭代才能獲得相當?shù)慕Y(jié)果,與之相比,Optimality Explorer 只需不到 500 次的迭代就能實現(xiàn)顯著優(yōu)化,可加快設計收斂。

利用 Optimality Explorer 提高效率

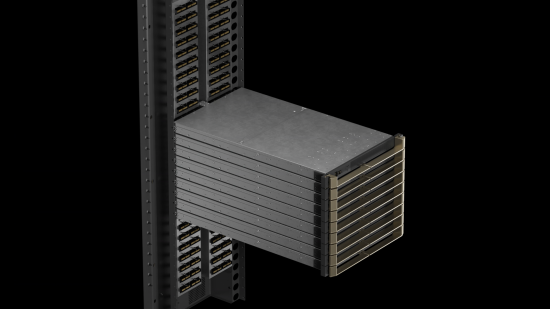

在復雜的電路 layout 中,僅使用單獨的走線和過孔是不夠的。需要將這些器件組合起來,創(chuàng)建互連設計,其中每個器件都會影響到其他器件的行為。

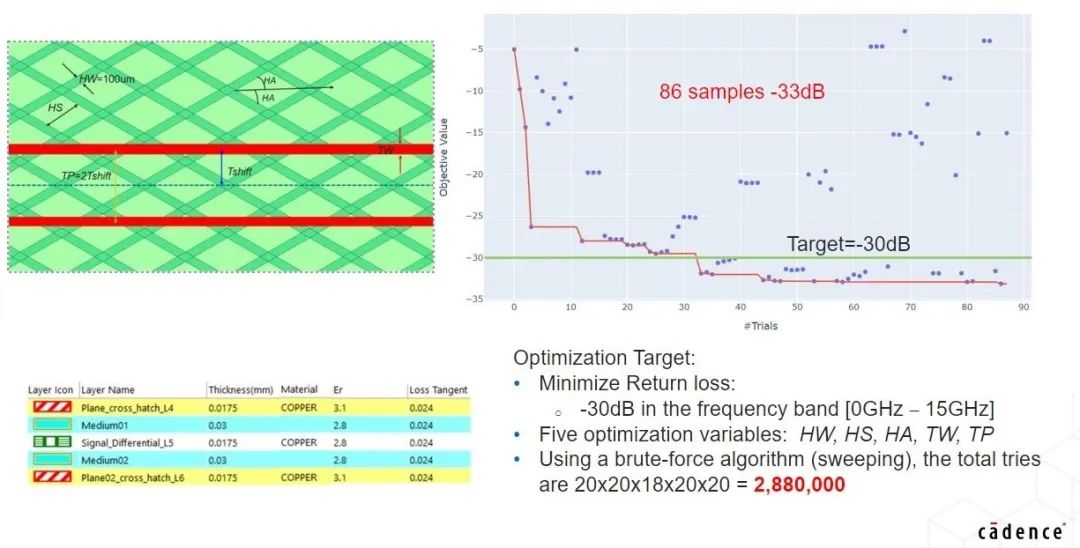

兩個交叉網(wǎng)格覆銅平面之間的差分對

Optimality Explorer 可高效、準確地仿真和優(yōu)化復雜的 3D layout,處理傳統(tǒng)上難以優(yōu)化的方案。該工具中包含用于 PC 封裝互連的場求解器,可處理各種通常被視為具有挑戰(zhàn)性的優(yōu)化方案。例如,它可以最大限度地優(yōu)化差分對設計中的交叉網(wǎng)格覆銅圖案,從而獲得更好的結(jié)果。Optimality Explorer 還能減少詳盡掃描所需的仿真次數(shù),更快地達到目標。

Optimality Explorer 可以優(yōu)化布局前和布局后設計。例如,Optimality Explorer 對 RF 功率分配器進行優(yōu)化,僅用 46 次仿真就達到了目標,而窮舉法則需要 300 多萬次仿真。Optimality Explorer 的多功能性還可擴展到處理具有許多參數(shù)的設計,例如,優(yōu)化具有 16 個參數(shù)的微帶貼片天線只需 71 次迭代。

展望未來:擴展 Optimality 平臺

Optimality Explorer 工具背后的團隊目前正在努力擴展該平臺的適用范圍,使之可以涵蓋熱學和流體動力學領域。這包括集成 Celsius 3D Solver 用于熱分析,集成 CFD 工具用于流體動力學領域。此外,電氣約束將被集成到 Allegro X Design Platform 現(xiàn)有的約束管理器中,為用戶提供更全面的解決方案。開發(fā)團隊將不斷報告這些功能改進的最新進展。

推動電子系統(tǒng)的多物理場分析

解決現(xiàn)代系統(tǒng)中的高速信號優(yōu)化問題是一項涉及多個維度的挑戰(zhàn)。Optimality Explorer 突破了傳統(tǒng)上極為消耗人力的優(yōu)化流程的限制,以 AI 驅(qū)動技術取代了“設計-測試-改進”循環(huán)的傳統(tǒng)交互流程,提供了一套更好的系統(tǒng)設計解決方案。Optimality Explorer 是電子設計領域的燈塔,指引設計人員自信穿梭于錯綜復雜的環(huán)境,在提供自動化技術的同時提高設計效率,為未來的綜合設計解決方案鋪平道路。

-

AI

+關注

關注

87文章

34294瀏覽量

275485 -

電子設計

+關注

關注

41文章

825瀏覽量

49038 -

高速信號

+關注

關注

1文章

240瀏覽量

17994

發(fā)布評論請先 登錄

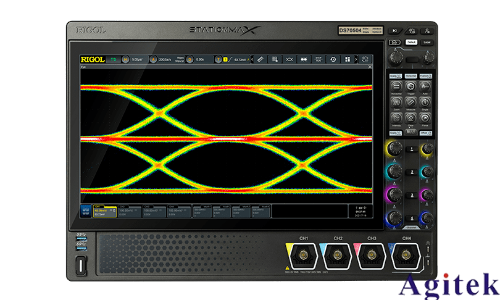

普源DS70000示波器高速信號測量優(yōu)化技巧

首創(chuàng)開源架構(gòu),天璣AI開發(fā)套件讓端側(cè)AI模型接入得心應手

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測......

高速信號如何判定?常見的高速信號有哪些?

高速信號線走線規(guī)則有哪些

高速信號走線越短越好嗎為什么

不是!讓高速先生給個過孔優(yōu)化方案就那么難嗎?

擴頻時鐘技術分享:SSC技術是什么、SSC對測試高速總線信號的影響

利用基于 AI 的優(yōu)化技術讓高速信號問題迎刃而解

利用基于 AI 的優(yōu)化技術讓高速信號問題迎刃而解

評論