RDL 技術是先進封裝異質集成的基礎,廣泛應用扇出封裝、扇出基板上芯片、扇出層疊封裝、硅光子學和 2.5D/3D 集成方法,實現了更小、更快和更高效的芯片設計。OSAT、 IDM和代工廠在這條道上的競爭日益激烈。如今RDL L/S 擴展到最先進 2μm及以下。未來三年將進入亞微米,賦能扇出封裝更高效能集成。本文為各位看官匯報了相關趨勢展望與企業技術進展。

隨著先進封裝的深入進展,重新分布層(RDL)技術獲得了巨大的關注。這種革命性的封裝技術改變了我們封裝 IC 的方式。

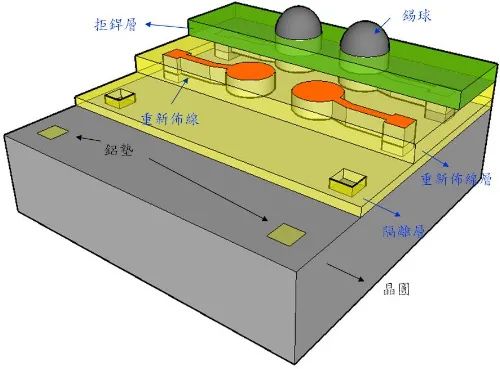

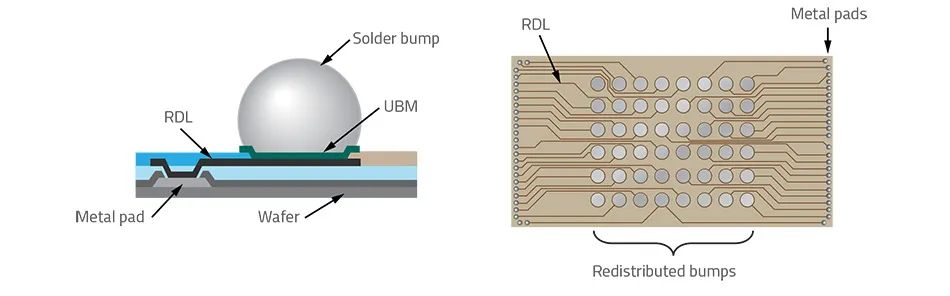

再分布層,RDL(Re-distributed layer),是實現芯片水平方向電氣延伸和互連,面向 3D/2.5D 封裝集成以及FOWLP的關鍵技術。它在芯片表面沉積金屬層和相應的介電層,形成金屬導線,并將IO端口重新設計到新的、更寬敞的區域,形成表面陣列布局。這項技術使得芯片間的鍵合更薄、工藝更簡單。RDL技術有助于設計人員能夠以緊湊且高效的方式放置芯片從而減少器件的整體占地面積。

CoWoS-R 插圖,CoWoS-R 是臺積電開發的一種 3D 集成技術,可在單個封裝中堆疊多個芯片圖源:TSMC

降低設備成本:RDL 技術消除了昂貴且耗時的引線鍵合和倒裝芯片鍵合工藝,減少了設備所需的元件數量,有助于降低設備成本。還用于創建需要小外形尺寸的高性能 IC。

減少占地面積:RDL將多個芯片集成到單個封裝中,從而減少器件的整體占地面積。這有助于打造更微型更緊湊的電子元件,這對智能手機、可穿戴設備和物聯網設備至關重要。

芯片上的重新分布層 (RDL) 圖源:Lam Research

最后的芯片扇出 WLP 相對于 FCBGA 和 PoP 架構將封裝厚度減少了 50%。圖源:三星

改善電氣性能:RDL 中介層因具有極小的信號通孔尺寸,而大幅改善了 SerDes 信號完整性 (SI),并且因 RDL 金屬厚度而改善了內存 SI。此外,采用的低損耗介電材料有助于降低介電損耗。

提高設計靈活:RDL 介質層利用精細的線路寬度和間距減少了路由干繞,提供了一種在 IC 內路由信號和電源的方法,支持更多的引腳數量。I/O觸點間距更靈活、凸點面積更大。

封裝應用廣泛:廣泛用于MEMS器件、傳感器、功率器件、存儲器、微處理器和圖形處理器的封裝。

技術趨勢與挑戰

RDL的技術進步對先進封裝意義非常。如今,4層RDL已經成熟,良率已達到99%的水平,約85%的封裝需求可以通過4層 RDL 來滿足,未來幾年,布線層數從4層增加到8層以上。頭部廠商封裝業務 RDL L/S 將從2023/2024年的2/2μm發展到2025/2026的1/1μm,再跨入到2027年以后的0.5/0.5μm。

RDL技術是一個復雜的過程,通常涉及半加成工藝,包括電介質沉積、濕法或干法蝕刻、阻擋層和籽晶層沉積以及鍍銅。需要掩膜設備、涂膠機、濺射臺、光刻機、刻蝕機以及其他配套工藝。

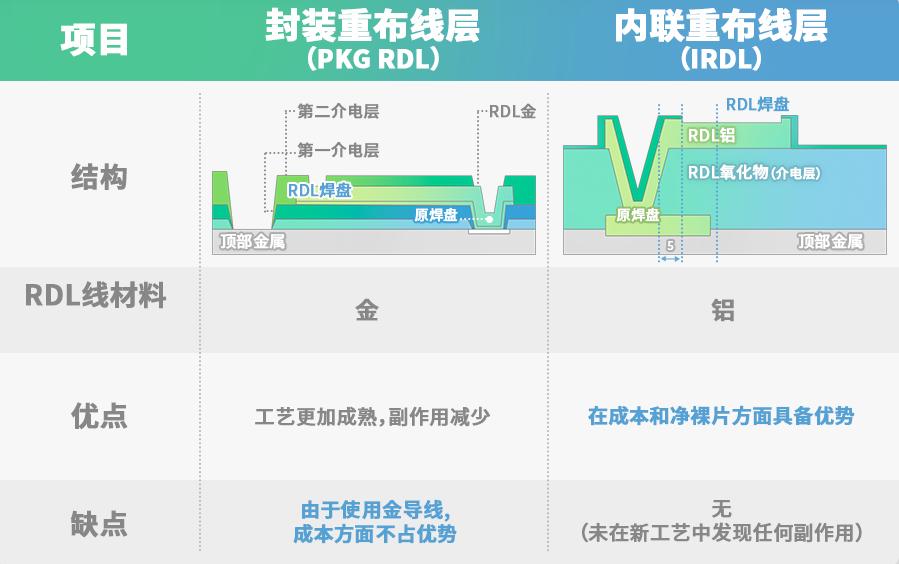

內聯重布線(IRDL)層是一種先進的FAB技術,能夠降低流程成本,可以在不損害現有芯片架構的前提下,將IO焊盤重新放置到封裝所需的位置。這項技術可以縮減成品厚度,有力地推動SK海力士成為移動市場技術領導者。圖源:SK海力士

先進扇出和異構封裝中的問題包括芯片移位、芯片翹曲、芯片間應力以及 RDL 走線損壞的風險。RDL 工藝涉及在有機聚酰亞胺 (PI) 或聚苯并惡唑 (PBO) 薄膜的狹窄跡線內鍍銅。新工藝旨在提高 RDL 粘附力,同時減少熱循環過程中的機械應力和熱應力。為了管理復雜的相互作用,先進的建模、材料工程和晶圓工藝正在投入使用,以確保穩健的 RDL 制造。

為了實現高密度、高帶寬的芯片互連,推動RDL 技術的進步,國內同仁仍需要在L/S 1/1μm 細線條光刻、實現RDL 高 I/O 密度和精細 I/O 間距的微孔加加工技術、低介電常數和低耗損因子的介電材料上和半加成法上,實現設備工藝的精細化。

從國產設備端,封裝內部 L/S 往更細方向發展,給國產光刻步進機提出更高要求;高端應用的封裝尺寸普遍大于 1 reticle size,需引入更大尺寸 reticle size的光刻設備;2μm 以下 L/S 布線檢測的國產 AOI 設備仍有很大發展空間。

| 企業 | FC | WLP | 2.5/3D | Chiplet | RDL |

| 日月光 | √ | √ | √ | √ | >6層L/S 1-1.5 μm |

| 安靠 | √ | √ | √ | √ | >4層 L/S 1-2 μm |

| 臺積電 | √ | √ | √ | √ | 6-14層 L/S 2 μm及以下 |

| 三星 | √ | √ | √ | √ | >4層 L/S 2 μm |

| 長電科技 | √ | √ | √ | √ | 5層L/S2μm |

| 通富微電 | √ | √ | √ | √ | 5層L/S2μm |

| 華天科技 | √ | √ | √ | √ | >4層 L/S 2 μm |

頭部企業封裝品種RDL現有技術對比來源:未來半導體

廠商技術方案進展

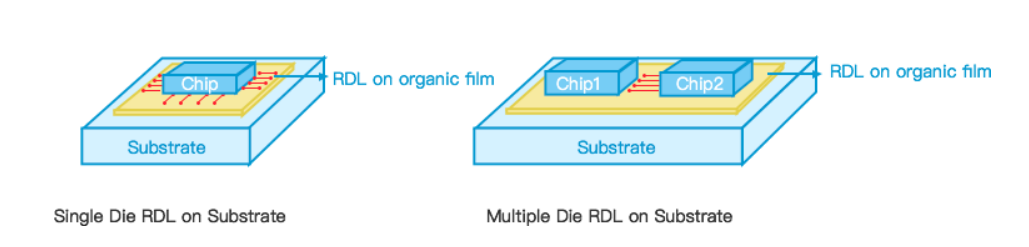

扇出型晶圓級封裝(FOWLP)作為新的異構集成技術,與傳統的2.5D/3D 結構相比,可以實現薄、高密度和低成本的封裝。其中就體現了RDL成本低的優勢,也是RDL最關鍵的技術,可用于創建具有小外形尺寸的高性能封裝。

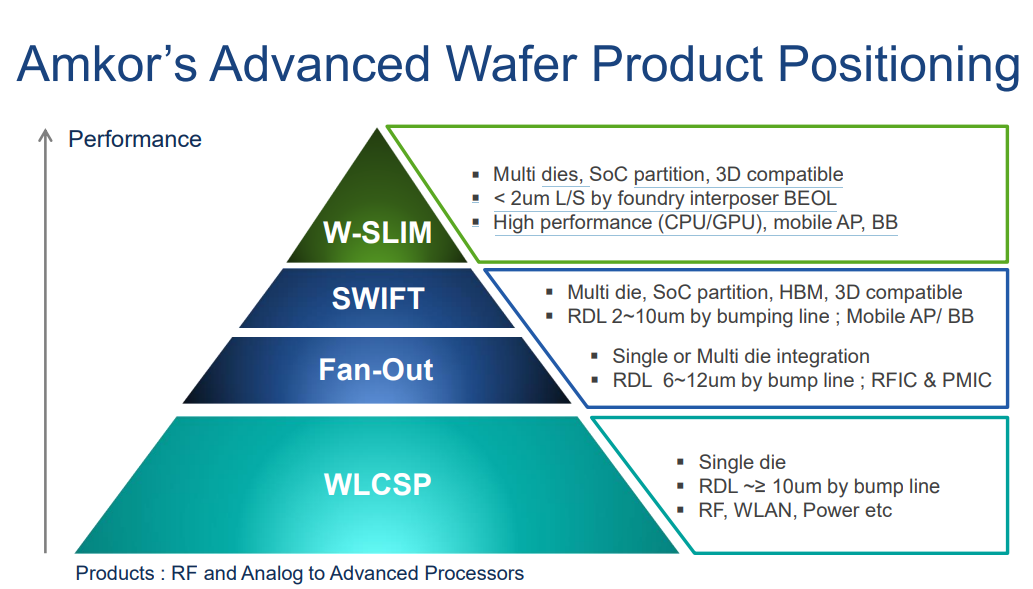

FOWLP受到一線公司的封裝技術支持,并以各自的產品命名,如臺積電的 InFo-Wlp,英飛凌/日月光/STATS ChipPAC的eWLB、安靠的SWIFT、Deca的M-Series,JCAP的ECP,Nepes的RCP,SPIL的TPI-FO等。

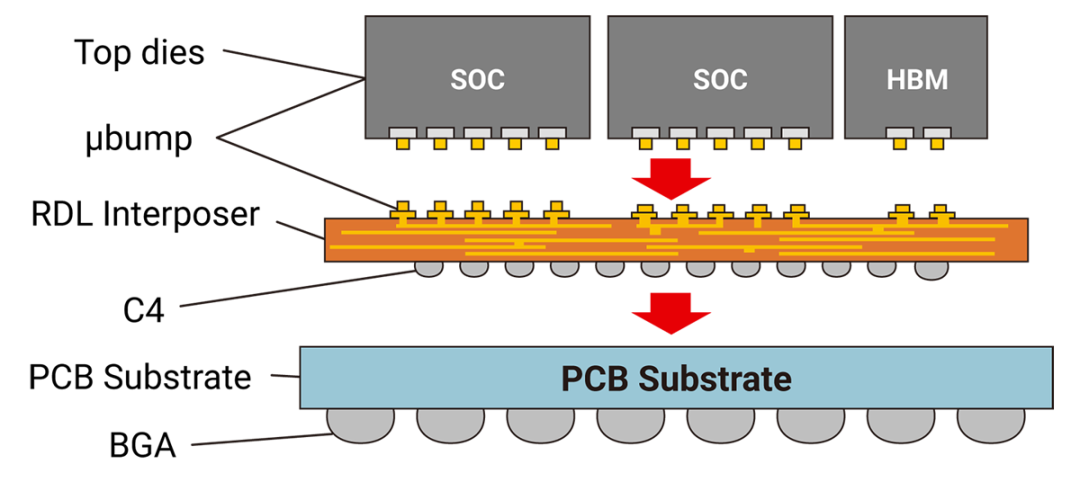

臺積電為片上系統 (SoC)、存儲器件和功率器件等各種應用提供廣泛的 RDL 技術解決方案,一個人寂寞狂奔。臺積電面向HPC應用應用的是CoWoS應用。其中CoWoS-R利用InFO技術和RDL中介層實現HBM和SoC集成,也是低成本方案。CoWoS-L結合了CoWoS-S和InFO技術的優點,使用夾層與LSI(局部硅互連)芯片進行互連,使用 RDL層進行電源和信號傳輸,提供靈活的集成。

臺積電目前向包括 NVIDIA 和 AMD 在內的一系列客戶提供 CoWoS 服務,用于其當前和即將推出的 AI GPU。半導體設計的轉變和對先進封裝的依賴促使臺積電擴大其 CoWoS 設施以滿足不斷增長的需求。

InFO是一個創新的晶圓級系統集成技術平臺,具有高密度RDL,可實現移動、高性能計算等各種應用的高密度互連和性能。相較于CoWoS方案,InFO則采用RDL代替硅中介層,無須TSV,性價比更高。

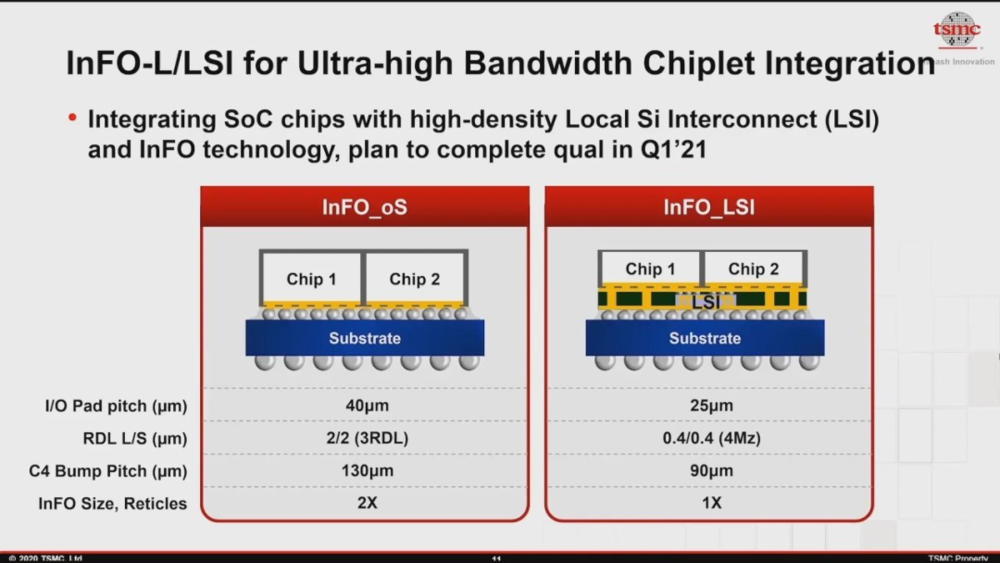

圖源:臺積電

標準封裝具有核心基板,先進集成扇出每側都有 2 至 5 層重新分布層 (RDL),臺積電的InFO_oS 將這一概念提升到了一個新的水平。InFO_oS 利用 InFO 技術具有更高密度的 2/2μm RDL 線寬/間距,它提供多達 14 個重新分布層 ,可實現芯片之間非常復雜的布線。在芯片附近的基板上還有一層更高密度的布線層。Info_LSI技術是InFO_oS的升級版,此種封裝使用硅橋(RDL L/S:0.4/0.4μm)以及RDL層代替整塊硅達到了性能與成本的平衡。

InFO 用在了蘋果 iPhone和Mac系列產品、在特斯拉的Dojo超算以及AMD巨獸級芯片MI300上。iPhone 15 Pro 搭載 A17 Pro APL1V02 應用處理器即采用鋁作為再分布層 (RDL)。Tesla D1 小芯片包含3個窄RDL層和 3個厚RDL層。

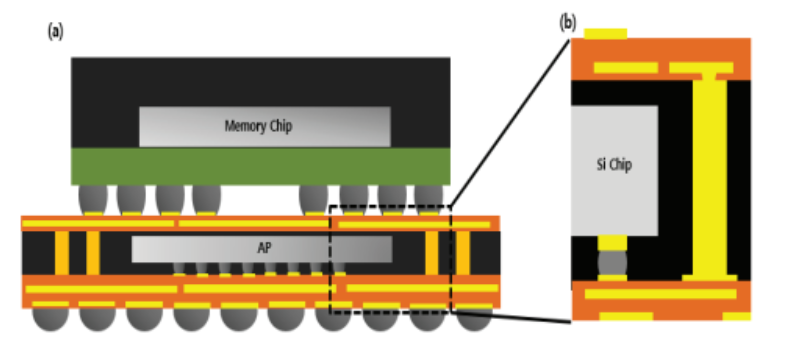

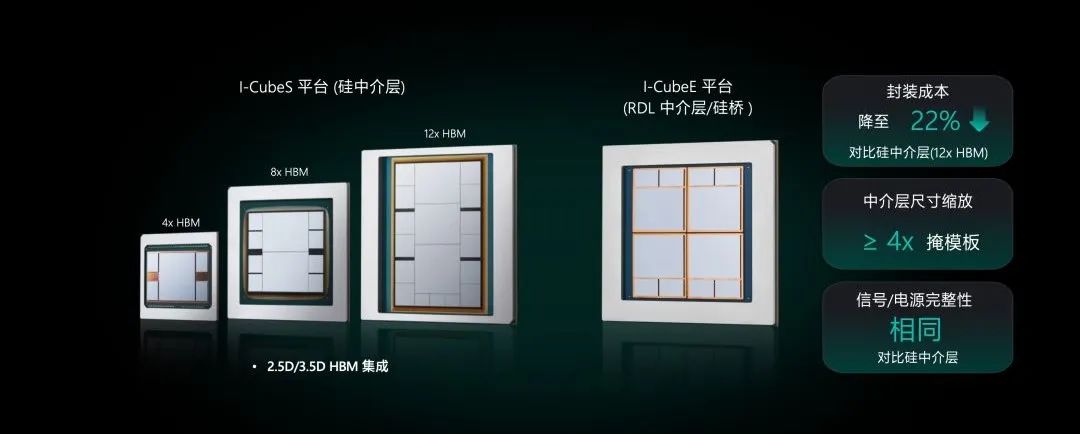

在這個全球加速轉變的時代,同時應對惡霸的步步蠶食,三星正在針對AI、5G及HPC的成本/算力/性能/延遲/帶寬/功能迭代集成解決方案。其中 I-CubeE采用集成硅橋的RDL中介層,對比現有硅中介層降低22%封裝成本,且能夠利用嵌入 FO-PLP 中間并用作接口的硅橋的小 L/S 優勢硅芯片之間。除了提供信號與電源完整性,支持大于掩模板(Reticle)4倍以上的大尺寸封裝。

圖源:三星

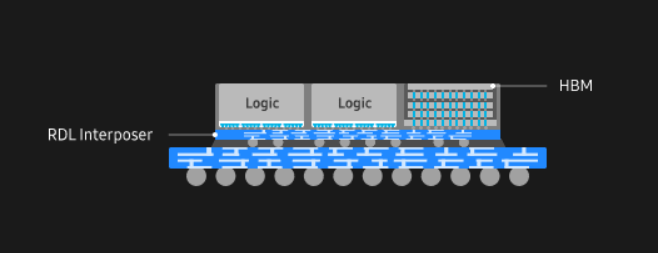

R-Cube是三星電子的低成本 2.5D RDL 中介層技術,該技術通過高密度 RDL實現邏輯到邏輯和邏輯到 HBM(高帶寬內存)模塊的連接,相比H-Cube/X-Cube,更具備成本低、快速的周轉時間、設計靈活性和信號完整性。Samsung Foundry 正在開發一款 2.5D 無硅通孔 RDL 中介層技術,配備 2/2um 的L/S,以及集成了 4 個 HBM 模塊的大型中介層(約為 1600mm2)。

三星半導體半導體先進封裝(AVP)業務團隊正在致力于開發基于RDL、硅中介層/硅橋接和TSV堆疊技術的下一代2.5D和3D高級封裝解決方案。據悉,三星計劃明年推出其解決方案,并將其稱為SAINT的高級互連技術(SAINT S、SAINT D、SAINT L),以與臺積電廣受歡迎的CoWoS封裝技術競爭。

當前,三星正在爭奪大量 HBM 內存訂單,這些訂單將繼續為NVIDIA 的下一代 Blackwell AI GPU提供動力。還贏得了 AMD 下一代 Instinct 加速器的訂單,但與臺積電深度綁定的 NVIDIA 控制90%人工智能市場相比,該訂單比例不足為傲。

正是這項技術的興起,使得封裝廠能夠在扇出封裝技術方面與頭部晶圓代工廠展開競爭。包括 ASE、Amkor 和JCET在內的 OSAT提供多種具有先進 RDL 工藝的封裝類型。

ASE 集團為內存、微處理器和圖形處理器等各種應用提供廣泛的 RDL 技術解決方案。其 VIPack 先進封裝平臺,利用先進的重布線層制程、嵌入式整合以及2.5D/3D 封裝技術實現超高密度和性能設計的三維異質封裝結構。其中FOCoS-CF 和 FOCoS-CL解決方案具備高層數(>6 層)和細線/間距(L /S = 1μm/1μm),適用于需要高密度芯片間連接、高輸入/輸出計數和高速信號傳輸的應用。

圖源:ASE

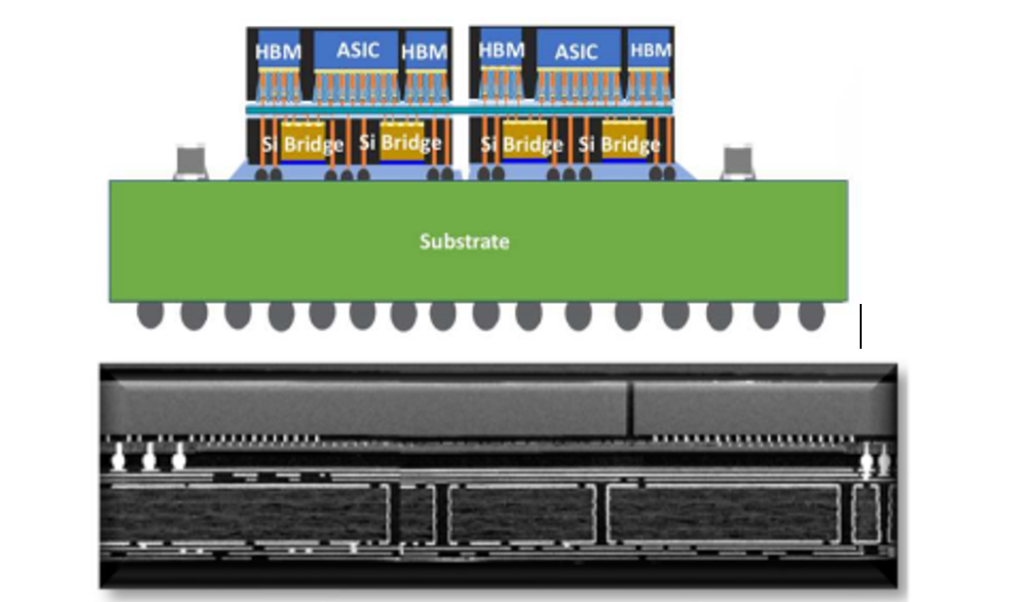

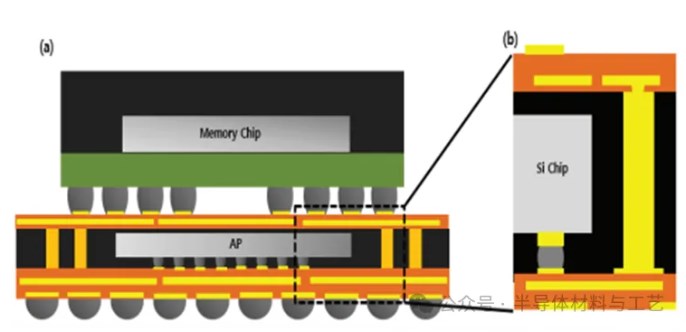

FOCoS(Fan-Out Chip on Substrate)封裝技術可實現小芯片與多達五層的多個 RDL 互連、1.5/1.5μm 的較小 RDL L/S 以及 34x50mm2的大扇出模塊尺寸的集成。它還提供廣泛的產品組合集成,例如具有高帶寬內存 (HBM) 的專用集成電路 (ASIC) 和具有 Serdes 的 ASIC,涵蓋 HPC、網絡、人工智能/機器學習 (AI/ML) 和云端。此外,由于消除了硅中介層并降低了寄生電容,FOCoS 比 2.5D Si TSV 表現出更好的電氣性能和更低的成本。

FOCoS-CF 由兩個面朝下的 ASIC 小芯片組成,通過 Cu 過孔直接與 RDL 連接,并且 Si 芯片和扇出 RDL (L/S 2/2 um) 之間沒有微凸塊;FOCoS-CL 由并排配置的三個小芯片(1 個 ASIC 芯片和 2 個 HBM)構建而成。ASIC 芯片和 2 個 HBM 通過 RDL (L/S 2/2 um) 和 Cu 微凸塊連接。

FOCoS-Bridge是一種 2.5D 封裝,它具有 ASIC和 HBM 兩個芯片,兩者通過嵌入 RDL 的硅橋芯片實現超細間距互連,硅橋芯片 (L/S 0.6/0.6 um) 嵌入扇出 RDL 層 (L/S 10/10 um),用于在 ASIC 和 HBM 之間建立連接。

扇出基板橋接芯片 (FOCoS-B) 原理圖(上圖)和橫截面圖(下圖)可實現比 RDL 更小的芯片到芯片連接 (0.8μm)。資料來源:ASE/IEDM

日月光看好人工智能驅動的長期半導體需求,正在擴大馬來西亞檳城工廠的產能。到今年底,日月光將有46座智能工廠,占全球半導體后段專業封測代工(OSAT)產業出貨量比重約32%,占臺灣地區OSAT出貨量比重超過50%。

安靠科技是一家全球半導體封裝和測試服務提供商。Amkor Technology 為傳感器、MEMS 器件和功率器件等各種應用提供廣泛的 RDL 技術解決方案。

圖源:安靠

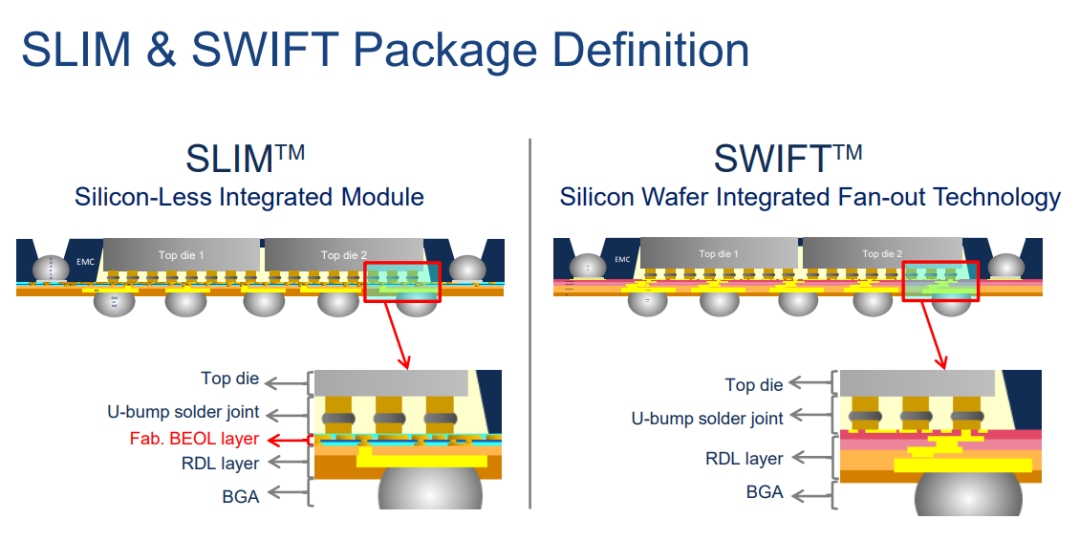

安靠的硅片集成扇出技術 ( SWIFT /HDFO) 旨在在更小的占地面積內提供更高的 I/O 和電路密度。SLIM及SWIFT方案均采用TSV-less工藝,其中SWIFT是Amkor的最先進的高密度扇出結構,可以實現 2/2 μm 線/間距特性,從而實現通常使用2.5D TSV 的SoC 分區和網絡應用所需的非常高密度的芯片到芯片連接。細間距芯片微凸塊為應用處理器和基帶設備等先進產品提供高密度互連。SLIM利用前道代工,在硅片表面的無機介質層上制作1μm,甚至亞微米金屬布線,L/S小于 2um。

圖源:安靠

HDFO高密度扇出性封裝是基于SWIFT開發而成的異構芯片封裝方案, 先將有微凸塊的芯片貼合至RDL預布線的介質層,也就是中段組裝流程,切單后再倒裝至FCBGA 基板以完成異構芯片封裝。該技術保持了高密度連線,出色的信號質量,無需TSV,在GPU 和FPG、服務器市場上進一步降低封裝成本。

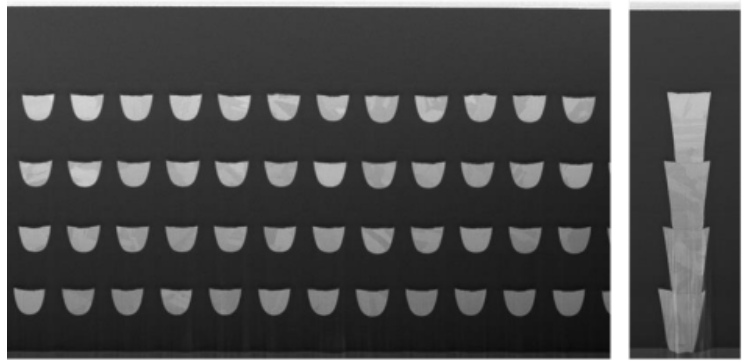

具有 2/1μm L/S 和 2μm 通孔堆疊的 4 層 RDL。圖源:Amkor

10月份,總投資16億美元的安靠越南芯片封測工廠開始運營。Amkor正在提高先進封裝生產能力,2023年初為3000晶圓/月,預計到2024年上半年,2.5D封裝量將達到5000個晶片/月。到2024年,英偉達預計將占安靠2.5D封裝產量的70-80%。

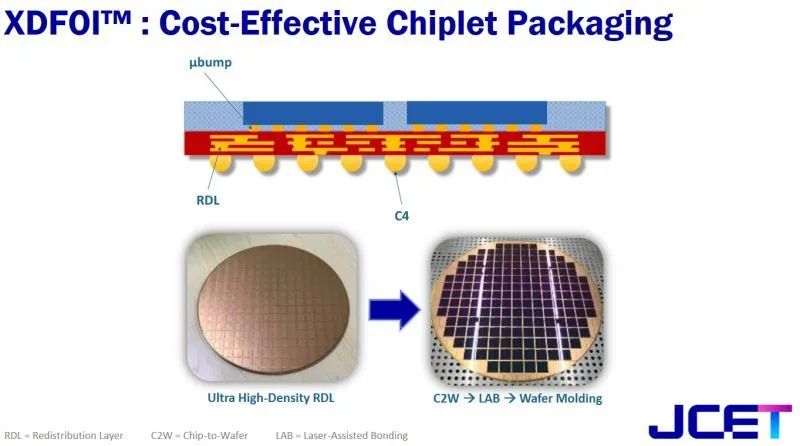

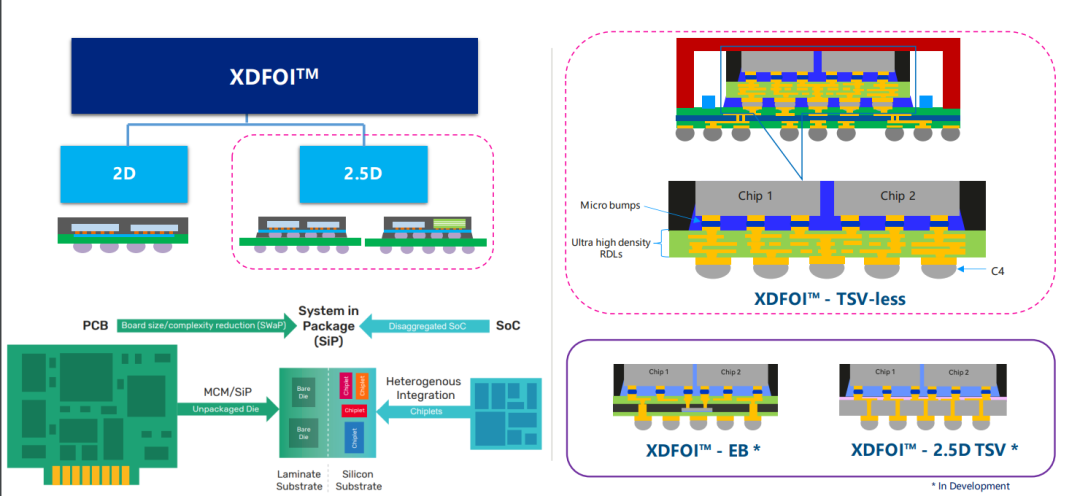

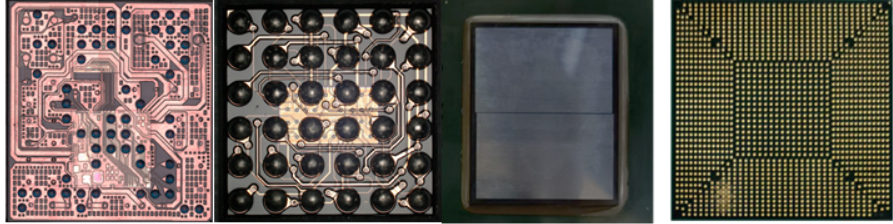

在RDL技術能力上,長電科技擁有國內領先的XDFOI平臺,該平臺是一種基于 RDL 的高性價比小芯片封裝解決方案,專為異構集成量身定制。可實現線寬和線距低至 2 微米的多個重新分布層 (RDL)。此外,極窄的凸點間距互連技術和大封裝尺寸允許集成多個芯片或小芯片、高帶寬存儲器和無源元件。

圖源:長電/linkedin

XDFOI將一個或多個邏輯芯片(CPU/GPU等)、I/O芯片和/或高帶寬內存芯片(HBM)放置在RDL堆棧中介層(RSI)上,形成高度集成的異構封裝。XDFOI可以將高密度fcBGA基板“小型化”,將部分分布層轉移到RSI基板上,利用RSI線寬和線距縮小至2微米的優勢,減少芯片互連間距,實現更高效率以及靈活的系統集成。另外,部分SoC互連可以轉移到RSI,實現基于Chiplet的結構創新和芯片的高性能和低成本。

目前長電科技XDFOI已有穩定量產的2.5D RDL高性能封裝方案,并持續推進多樣化方案的研發及量產,向國內外客戶提供面向小芯片架構的高性能先進封裝解決方案,在行業技術及量產經驗均居于領先。從產能布局,長電科技是國內最大參與者之一。長電科技臨港工廠是國內首個大規模專業生產車規級芯片成品的先進封裝基地。公司計劃在2025年上半年實現設備進廠,然后進入到量產的階段。

圖源:長電/semi

通富微電有面向高性能計算研發和量產的 VisionS 2.5D/3D Chiplet方案,自建2.5D/3D產線全線通線,1+4產品及4層/8層堆疊產品研發穩步推進;基于ChipLast工藝的Fan-out技術,實現5層RDL超大尺寸封裝(65×65mm);超大多芯片FCBGA MCM技術,實現最高13顆芯片集成及100×100mm以上超大封裝。在FO系列中,提供Chip First和Chip last兩種方案, 重分布L/S為2/2um,應用于MIC、RF、CPU、GPU和網絡。

圖源:通富微電

公司通過在多芯片組件、集成扇出封裝、2.5D/3D等先進封裝技術方面的提前布局,并且完成高層數再布線技術開發,不斷強化與客戶的深度合作,滿足客戶AI算力等方面需求。

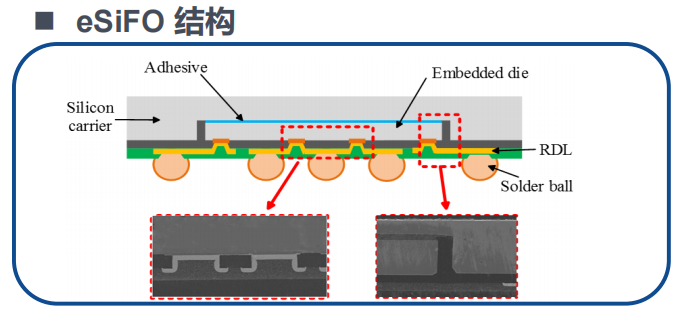

華天科技三維晶圓級封裝平臺3D Matrix 旗下有eSiFO和eSinC。在高密度晶圓級扇出型封裝技術L/S為2/2um,RDL Layer為 6 P5M,封裝尺寸15×15mm。eSiFO通過在硅基板上刻蝕凹槽,將芯片正面向上放置且固定于凹槽內,芯片表面和硅圓片表面構成了一個扇出面,在這個面上進行多層再布線,并制作引出端焊球,最后進行切割、分離和封裝。

圖源:華天科技/CSPT2023

eSinC將多顆芯片集成,用硅基取代塑封料,實現的封裝尺寸最大可以達到40mm×40mm,未來RDL線寬線距越來越小,層數會越來越多。eSinC技術結合fine pitch RDL、hybrid bond、高級基板等平臺技術,可以進一步提升封裝密度,建立完整的Chiplet封裝平臺。

華天科技正在大力發展高端芯片的晶圓和成品測試業務,積極擴充高端測試產能規模。華天上海華天南京華天江蘇三大工廠新封裝項目明年起將陸續迎來量產。

甬矽電子正在積極布局先進封裝相關領域,通過實施Bumping項目掌握的RDL及凸點加工能力,為公司后續開展晶圓級封裝、扇出式封裝及2.5D/3D封裝奠定了工藝基礎。公司致力于不斷縮小線寬,目前最小線寬可達5um,最小線間距可達5um。公司運用于量產產品上的細線寬為最小線寬8um,最小線間距8um。

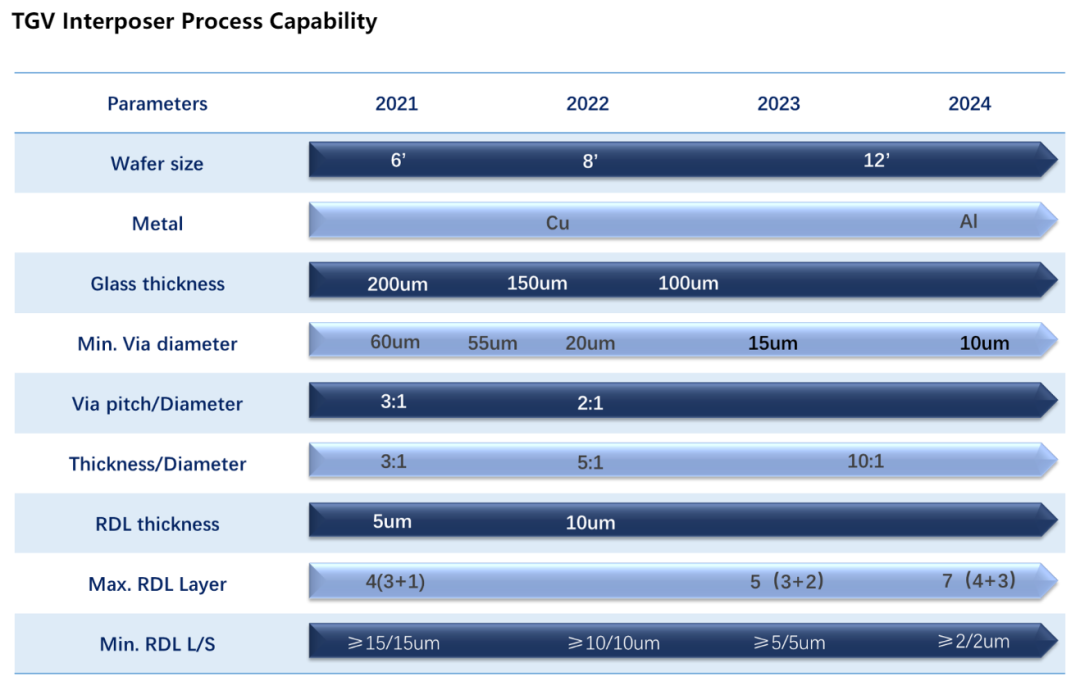

云天半導體開發了濾波器三維封裝、新型扇出封裝技術、玻璃通孔技術以及IPD技術,在玻璃通孔方向,用大馬士革工藝在玻璃基表面制備三層RDL堆疊;采用無機薄膜材料作為介質層進行制備;實現更細更高精度的金屬布線。2.5D TGV 將現有的5層 RDL L/S 5um 推進至 2024年的 7層 L/S 5um,廣泛應用在射頻組件、光電集成、MEMS。相關技術已經進入量產階段,為國內眾多合作企業和科研機構提供了高效代工服務。

圖源:廈門云天

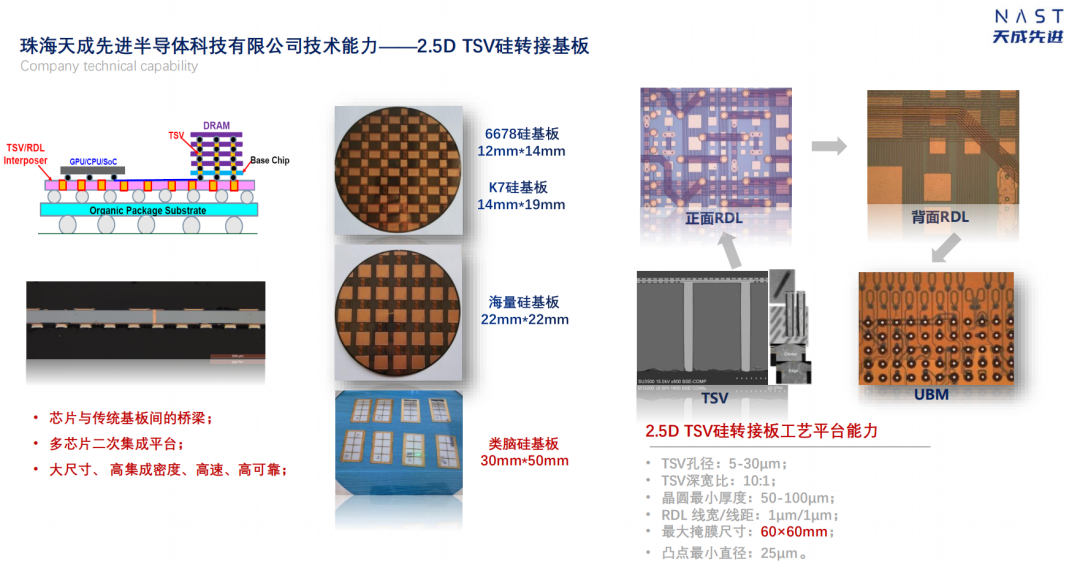

珠海天成先進半導體技術能力上,2.5D TSV硅轉接基板上,集成產品 RDL L/S可做到 3μm,正面4層RDL,硅基TSV轉接板最大尺寸30×50mm,可實現GPU、CPU、多層存儲器的高密度、高速、高可靠集成;在3D TSV 堆疊可實現8層RDL L/S 1μm;且可以實現芯片晶圓直接加工TSV互連、TSV硅轉接基板堆疊、多芯片TSV晶圓埋置堆疊。公司規劃總投資超30億元,其中一期總投資約16.5億元,可實現年產24萬片12英寸TSV立體集成晶圓產品,于2024年底實現通線。

圖源:天成先進

芯德科技是一家快速成長的半導體高端封測科技新銳。擁有高密度重布線扇出結構FOCT-R技術平臺,實現了同質異質芯片間的互連;并且可以整合兩種具有不同特點的基板:高層數的基板,更精密的再布線轉接板(RDL Interposer);還可以進一步實現更大的2.5D封裝,并降低基板層數。使用再布線和凸塊技術,實現最小2μm的線寬,2um間距的布線。芯德科技推出單芯片HPFO技術,采用Interposer來有效降低基板的制造層數。目前公司實現QFN、CSP、LGA/SIP、FCBGA、FCCS的量產。公司Chiplet揚州工廠預計2024年完工;10月份,芯德科技完成6元融資持續助力CHIPLET等高端封測領域布局。

青島新核芯 Hyper 2D是一種新封裝結構進行異質整合,優勢在于此結構無需制備TSV interposer可使成本更具競爭力,其線寬限距可達2/2 um以下。主要制程均制作于載體基板上,可以壓縮制作時間并控制其良率,大大提升生產效率。另有FOStrip 新型扇出型封裝技術,輕薄短小、性能好、散熱佳,封裝厚度減薄到0.6 mm以下,同時金屬線的跨距制作能力微縮到5um。

圖源:青島新核芯

中科智芯產品主要集中在晶圓凸點/芯片規模封裝(WLCSP,Bumping)、扇出型封裝(Fanout WLP)、系統集成、三維堆疊封裝以及晶圓測試等高端封測業務。一期規劃兩個廠的晶圓級封裝產能為月產>3萬片。實現重布線層與層、芯片之間高精度對位是公司晶圓級封裝的四大關鍵技術之一,晶圓級扇入封裝的重布線寬/線距 ≥ 5um/5um。

圖源:中科芯

中科芯晶圓級封裝解決方案上,針對RDL向內再布線,封裝體尺寸等于原來芯片尺寸,I/O數量一般小于200個;針對扇出型封裝RDL可以同時向內/向外布線,封裝體尺寸大于原芯片尺寸,I/O數量可達10000個左右。目前,中科芯初步具備CoWoS-R工藝能力,RDL First,4P5M布線,最小線寬線距10μm,5層RDL,已開始生產相關產品。擁有自主JY12英寸晶圓級扇出型先進封裝工藝線。從市場導入到產品交付,全周期質量管控,具備一站式先進封裝代工服務能力。

盛合晶微以先進的12英寸高密度凸塊和再布線加工起步,致力于提供中段硅片制造和測試服務,SmartAiP是世界首個超寬頻雙極化的5G毫米波天線芯片晶圓級集成封裝工藝,融合了多層雙面再布線(RDL)技術。3DFO是SmartPoser技術平臺衍生出的晶圓級系統集成技術,具有高密度RDL和TIV特性。公司實現了近存計算芯片大尺寸全RDL走線封裝結構的量產。成品尺寸達到1600mm2,采用了盛合晶微4層RDL再布線加工工藝。

審核編輯:劉清

-

傳感器

+關注

關注

2562文章

52560瀏覽量

763675 -

芯片設計

+關注

關注

15文章

1064瀏覽量

55465 -

IC封裝

+關注

關注

4文章

187瀏覽量

27129 -

MEMS器件

+關注

關注

2文章

47瀏覽量

13114 -

圖形處理器

+關注

關注

0文章

202瀏覽量

25975

原文標題:先進封裝技術之爭 | RDL線寬線距將破亞微米,賦能扇出封裝高效能低成本集成

文章出處:【微信號:封裝與高速技術前沿,微信公眾號:封裝與高速技術前沿】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

兩種高效能電源設計及拓撲分析

突破新興高效能電源要求上的限制

高效能V系列新品:鎖定1000流明以下商業與住宅照明市場

功率級低成本高效功率竊取設計方案

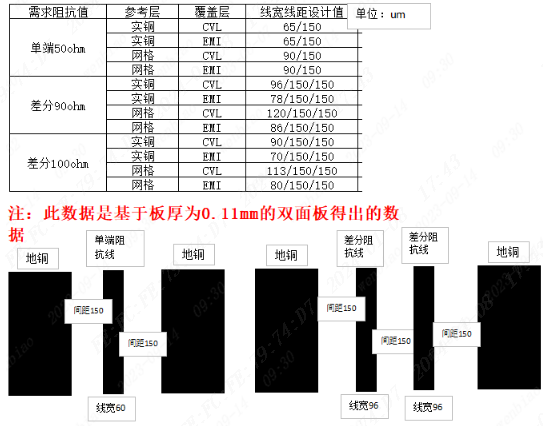

PCB設計線寬、線距規則設置多大?

PCB設計中線寬線距的重要性

Manz亞智科技RDL制程打造CoPoS板級封裝路線, 滿足FOPLP/TGV應用于下一代AI需求

Manz亞智科技RDL制程打造CoPoS板級封裝路線,滿足FOPLP/TGV應用于下一代AI需求

RDL線寬線距將破亞微米賦能扇出封裝高效能低成本集成

RDL線寬線距將破亞微米賦能扇出封裝高效能低成本集成

評論