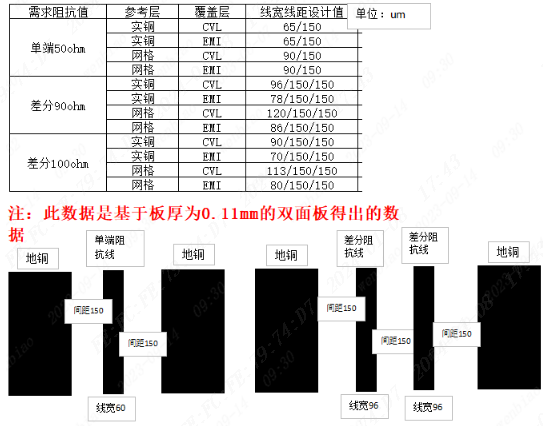

PCB一般板廠用SI9000來計算阻抗,但FPC我用SI9000模擬了幾次都不準,剛好*** FPC可以免費打樣了,后面就直接打樣,用TDR方式測出阻抗,再打切片測量銅厚,基材厚度,線寬線距,反推再修正的方式,整了3次才把阻抗線寬及線距整出來,結果如下:

注:CVL表示只貼了阻焊膜,EMI表示是貼了屏蔽膜的,另外屏蔽膜是接了地的,如果不接地會有影響

以上數據是基于FPC板厚0.11mm,基材PI厚度25um,銅厚12um(成品銅厚15-18um)的,不同基材會有所不同,數據僅供參考,需要打樣驗證!

審核編輯 黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

阻抗

+關注

關注

17文章

972瀏覽量

47352 -

FPC

+關注

關注

71文章

985瀏覽量

65291 -

PCB

+關注

關注

1文章

2097瀏覽量

13204

發布評論請先 登錄

相關推薦

熱點推薦

FPC如何重塑現代藍牙耳機設計與性能

日常使用中的沖擊與振動,提升連接可靠性和產品壽命。

5.簡化組裝,提高良率: FPC通常作為一個整體模塊進行安裝,減少了傳統飛線焊接的點位和復雜度,降低了組裝難度和潛在故障點,提高了生產效率和一致性

發表于 07-04 11:47

Allegro Skill布線功能之調整差分的線寬線距

在進行高速PCB設計的過程中,當PCB板的疊層結構發生變化時,為了保持信號的完整性,我們不得不對高速信號線的線寬進行相應的調整。那么這種調整是必要的,因為不同的疊層結構會對信號的阻抗產生影響。手動去

Allegro Skill布線功能之改變線寬介紹

會對信號的阻抗產生影響。手動去逐一更改這些高速信號線的線寬是一項非常繁瑣且耗時的工作,它不僅不能提高我們的設計效率,反而會因為工作量巨大而降低整體的設計效率。

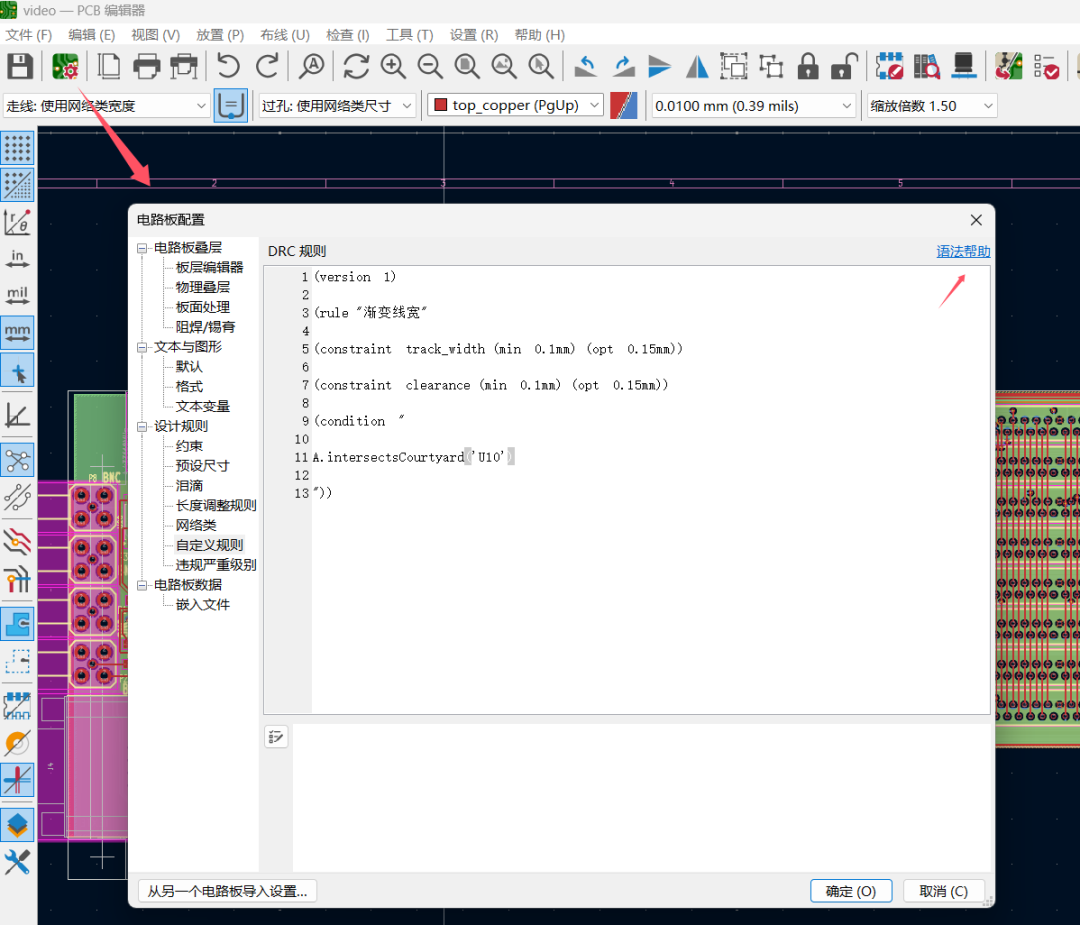

如何在特定區域設置線寬、線距規則

“ ?今天偷個懶,分享一個 Hayden 大佬提供的自定義規則,非常實用。可以在特定區域(如BGA器件范圍內)定義特殊的線寬、線距規則。? ” 就是下面這段自定義規則,表示 U10

PCB走線,盲目拉線,拉了也是白拉!

布置在阻抗控制層上,須避免其信號跨分割。

2、 布線竄擾控制

a) 3W原則釋義

線與線之間的距離保持3倍線寬。是為了減少線間串擾,應保證線間距足夠大,如果

發表于 03-06 13:53

從定位到質檢:傳感器如何重塑FPC裁切與AOI檢測的精度邊界?

生產效率和產品質量。憑借深厚的技術積累和創新能力,明治針對3C行業設備提出智能升級解決方案,旨在全面提升廠商自動化、智能化水平。↓隨著FPC線寬/線距向50μm以

把ADS850的數據接口和時鐘信號通過FPC線連接至FPGA,當FPC線纜大于5cm,會導致丟位,錯位現象,怎么處理?

之前把ADS850的數據接口和時鐘信號通過FPC線連接至FPGA,發現當FPC線纜大于5cm(10cm,12cm,15cm)時,采樣值為01 1111 1111 1111到10 0000 000

發表于 02-11 07:27

TUSB8041的阻抗怎么計算?

根據官網給的手冊畫好了pcb連線的時候,發現USB有些需要差分信號線,但是官網數據手冊上只是寫了必須設計阻抗在90歐姆左右,并不是很了解怎么計算,希望大佬給點提示,線寬和線

發表于 12-16 06:05

FPC設計與制造流程 FPC與傳統PCB的區別

設計與制造的基本流程: 1. 設計階段 需求分析 :根據產品的功能需求,確定FPC的尺寸、形狀、層數等參數。 布局設計 :使用專業的PCB設計軟件進行電路布局,包括元器件的放置和電路的走線。 走線設計 :確保電路的電氣性能,同時

技術資訊 I 如何使用 Allegro X PCB Editor 優化RF布線和阻抗

走線寬度、走線厚度以及在z軸上將走線與參考平面分隔開的介質高度。信號層下方的連續參考平面對于保持最佳阻抗也至關重要。在同一層上保持適當的走線

FPC連接器0.3間距高1.0mm掀蓋式圖紙

常用連接器產品有:FPC連接器0.3間距高1.0mm掀蓋式,SIM卡座、SIM卡座帶卡托、TF卡座、SD卡座、耳機座,DC電源座,CR2032電池座CR1220電池座,MINI PCIE連接器

發表于 08-01 17:15

?0次下載

FPC阻抗線寬線距參考

FPC阻抗線寬線距參考

評論