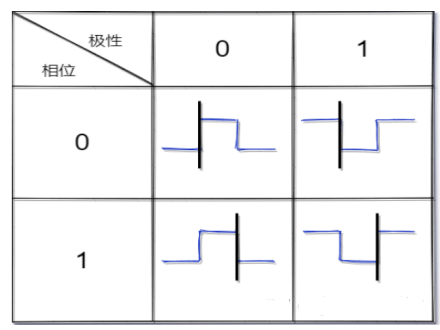

SPI有四種工作模式

SPI(Serial Peripheral Interface)總線有四種工作模式,這些模式通過配置時鐘極性(CPOL)和時鐘相位(CPHA)來確定數(shù)據(jù)傳輸?shù)臅r機和方式。以下是這四種工作模式:

1. 模式0(CPOL = 0,CPHA = 0):時鐘空閑狀態(tài)為低電平(0),數(shù)據(jù)在時鐘的下降沿采樣和/或輸出。這意味著數(shù)據(jù)在時鐘的上升沿進行采樣,數(shù)據(jù)在時鐘的下降沿進行輸出。

2. 模式1(CPOL = 0,CPHA = 1):時鐘空閑狀態(tài)為低電平(0),數(shù)據(jù)在時鐘的上升沿采樣和/或輸出。這意味著數(shù)據(jù)在時鐘的下降沿進行采樣,數(shù)據(jù)在時鐘的上升沿進行輸出。

3. 模式2(CPOL = 1,CPHA = 0):時鐘空閑狀態(tài)為高電平(1),數(shù)據(jù)在時鐘的上升沿采樣和/或輸出。這意味著數(shù)據(jù)在時鐘的下降沿進行輸出,數(shù)據(jù)在時鐘的上升沿進行采樣。

4. 模式3(CPOL = 1,CPHA = 1):時鐘空閑狀態(tài)為高電平(1),數(shù)據(jù)在時鐘的下降沿采樣和/或輸出。這意味著數(shù)據(jù)在時鐘的上升沿進行輸出,數(shù)據(jù)在時鐘的下降沿進行采樣。

這些模式允許SPI設(shè)備和主設(shè)備在不同的時鐘極性和時鐘相位條件下進行數(shù)據(jù)傳輸。根據(jù)特定的SPI設(shè)備和應(yīng)用需求,可以根據(jù)其規(guī)范配置適當(dāng)?shù)墓ぷ髂J健?/p>

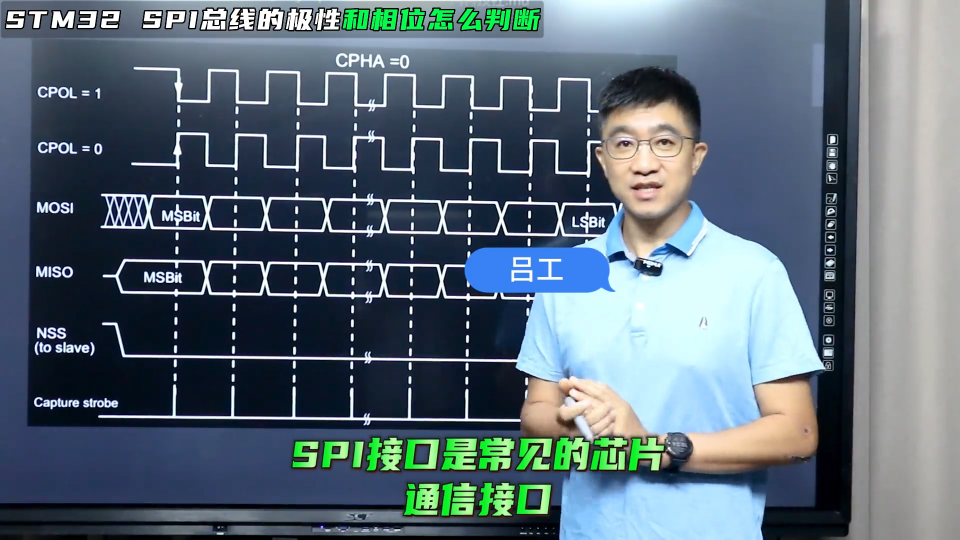

SPI相位和極性

SPI有四種工作模式,取決于相位(CPHL)和極性(CPOL)兩個因素。CPOL表示時鐘線在空閑時候的狀態(tài)

CPOL=0: SCLK在空閑時屬于低電平狀態(tài)CPOL=1: SCLK在空閑時屬于高電平狀態(tài)CPHA表示采樣時刻

CPHA=0:表示每個周期的第一個時鐘沿采樣

CPHA=1:表示每個周期的第二個時鐘沿采樣

優(yōu)點:相比于IIC而言,傳輸速率快,且數(shù)據(jù)傳輸靈活,擁有獨立的數(shù)據(jù)線,雙方可以同時收發(fā)數(shù)據(jù)。缺點:需要占用更多的硬件資源,沒有應(yīng)答信號,不能對傳輸?shù)臄?shù)據(jù)做檢查。

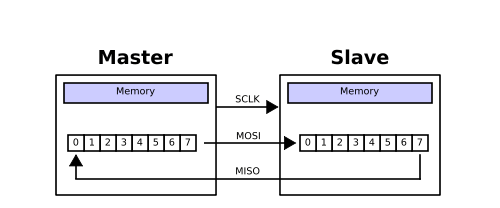

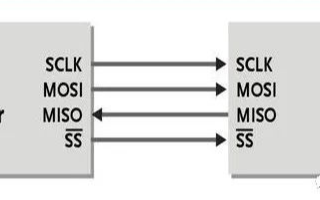

spi總線一般使用幾條線分別是什么

SPI(Serial Peripheral Interface)總線通常使用4條線進行連接,這些線分別是:

1. 主時鐘線(SCK):主設(shè)備通過該線發(fā)送時鐘信號,用于同步數(shù)據(jù)傳輸。

2. 主輸出/從輸入線(MOSI):主設(shè)備通過該線發(fā)送數(shù)據(jù)給從設(shè)備。

3. 主輸入/從輸出線(MISO):從設(shè)備通過該線將數(shù)據(jù)發(fā)送給主設(shè)備。

4. 片選線(SS):用于選擇和啟用與主設(shè)備通信的特定從設(shè)備。片選線為每個從設(shè)備提供一個獨立的信號線。

SPI總線可以靈活配置,可以根據(jù)具體需要增加或減少信號線的數(shù)量。例如,一些SPI設(shè)備可能不需要使用片選線(SS),因為它們只與一個主設(shè)備通信,而其他設(shè)備可能需要使用多個片選線以支持與多個主設(shè)備的通信。

審核編輯:黃飛

-

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

2003瀏覽量

65678 -

SPI

+關(guān)注

關(guān)注

17文章

1782瀏覽量

94707 -

總線

+關(guān)注

關(guān)注

10文章

2948瀏覽量

89343 -

SPI總線

+關(guān)注

關(guān)注

4文章

104瀏覽量

27940

發(fā)布評論請先 登錄

SPI總線小結(jié)

SPI中的極性CPOL和相位CPHA介紹

SPI總線概述

淺談SPI總線

AD7606 SPI通信的時鐘極性和時鐘相位要求是什么?

如何設(shè)置SPI中的極性CPOL和相位CPHA

STM32單片機SPI極性和相位的設(shè)置方法

SPI總線接口與簡單配置

SPI時鐘極性和時鐘相位

SPI總線的相位和極性

SPI總線的相位和極性

評論