共讀好書(shū)

潘浩東 盧桃 陳曉東 何驍 鄒雅冰

(工業(yè)和信息化部電子第五研究所)

摘要:

采用有限元數(shù)值模擬方法,建立金氧半場(chǎng)效晶體管(MOSFET)三維有限元模型,定義不同大小和位置的粘接層空洞模型,對(duì)器件通電狀態(tài)下的溫度場(chǎng)進(jìn)行計(jì)算,討論空洞對(duì)于熱阻的影響。有限元仿真結(jié)果表明,隨著芯片粘接層空洞越大,器件熱阻隨之增大,在低空洞率下,熱阻增加緩慢,高空洞率下,熱阻增加更明顯;總空洞率一致時(shí),不同位置空洞對(duì)應(yīng)器件熱阻的關(guān)系為中心空洞>拐角空洞>陣列空洞。采用雙界面法對(duì)含有空洞缺陷的器件進(jìn)行了熱阻測(cè)試,將試驗(yàn)數(shù)據(jù)修正仿真結(jié)果,獲得準(zhǔn)確的空洞-熱阻曲線,對(duì)于芯片粘接空洞工藝控制提供理論參考。

0 引言

在電子行業(yè),功率器件應(yīng)用廣泛,國(guó)內(nèi)外學(xué)者對(duì)于功率器件的可靠性做了大量的研究,其中對(duì)于功率器件的散熱性能尤為關(guān)注。研究表明,溫度的上升會(huì)大大提高芯片失效的概率,溫升每達(dá)到10 ℃,失效概率能提升一倍 [1] 。對(duì)功率器件的散熱影響最為關(guān)鍵的結(jié)構(gòu)是芯片粘接界面,粘接界面空洞的存在會(huì)提高器件的熱阻,降低器件的散熱性能。

謝鑫鵬等利用有限元法研究了功率芯片粘接層空洞對(duì)器件溫度場(chǎng)和應(yīng)力場(chǎng)的影響,分析了芯片粘貼工藝中空洞成型的機(jī)理。Katsis D C等對(duì)功率循環(huán)后的芯片熱阻進(jìn)行了研究,在經(jīng)歷了7 000個(gè)循環(huán)后,芯片熱阻增加了一半,在多次循環(huán)后芯片粘接層的空洞達(dá)到了50% [2] ;Fleischer A S等對(duì)粘接層空洞與器件熱阻的關(guān)系進(jìn)行研究,發(fā)現(xiàn)熱阻隨空洞體積增大而增大 [3] ;章蕾等人采用有限元方法進(jìn)行了空洞對(duì)器件封裝溫度影響的研究,為提高封裝的可靠性提供了理論依據(jù) [4-5] 。采取有限元數(shù)值模擬仿真的方法對(duì)芯片粘接層空洞進(jìn)行相關(guān)研究,優(yōu)點(diǎn)是建立模型簡(jiǎn)單,相較于制備試驗(yàn)樣品,能節(jié)省大量人力機(jī)時(shí),但是由于數(shù)值模擬難以模擬所有試驗(yàn)環(huán)境,因此所得到的結(jié)果往往有所失真,需要通過(guò)部分真實(shí)的試驗(yàn)數(shù)據(jù)來(lái)校核修正。

本文將采用有限元數(shù)值模擬仿真的方法對(duì)芯片粘接空洞,研究不同位置和不同大小的空洞對(duì)于器件溫度場(chǎng)影響,并計(jì)算器件結(jié)殼熱阻;同時(shí)對(duì)涵蓋不同空洞缺陷的試驗(yàn)樣品進(jìn)行熱阻測(cè)試,并以試驗(yàn)數(shù)據(jù)修正仿真結(jié)果,建立準(zhǔn)確的熱阻-空洞率曲線,為實(shí)際工藝提供理論指導(dǎo)。

1 熱分析理論及測(cè)試原理

1.1 熱分析理論

有限元熱分析是將所研究對(duì)象劃分成有限個(gè)單元,通過(guò)熱平衡和能量守恒定律,計(jì)算各單元節(jié)點(diǎn)的溫度或者其他熱相關(guān)的物理參數(shù)。針對(duì)機(jī)械電子領(lǐng)域的很多復(fù)雜的熱-力學(xué)工程問(wèn)題,采用有限元熱分析法是一種有效的求解方法。在熱分析中,常涉及的傳熱方式一般有三種,分別是熱傳導(dǎo)、熱對(duì)流和熱輻射。針對(duì)不同的傳熱方式,設(shè)置不同的分析參數(shù)進(jìn)行求解計(jì)算 [6] 。

在進(jìn)行熱分析仿真計(jì)算時(shí),可選擇采取穩(wěn)態(tài)分析或者瞬態(tài)分析兩種方式,當(dāng)所研究系統(tǒng)各點(diǎn)的溫度僅隨位置的變化而變化,不隨時(shí)間變化而變化,即可采取穩(wěn)態(tài)分析;而當(dāng)系統(tǒng)的溫度變化除了與位置有關(guān),還與時(shí)間相關(guān),此時(shí)應(yīng)采用瞬態(tài)分析。穩(wěn)態(tài)熱分析的能量平衡方程以矩陣方式表示為 [7] :

式中:[ K ]代表的是傳導(dǎo)矩陣,其中包括熱系數(shù)、對(duì)流系數(shù)及輻射和形狀系數(shù)等物理量;{ T }表示的是節(jié)點(diǎn)溫度向量;{ Q }是節(jié)點(diǎn)熱流率向量,熱生成也包含在內(nèi)。

瞬態(tài)熱分析公式 [8] 表示為:

式中:{ Q }表示的是節(jié)點(diǎn)熱流率向量,包括熱生成;[ K ]代表的是傳導(dǎo)矩陣,其中包括包含熱系數(shù)、對(duì)流系數(shù)及輻射和形狀系數(shù)等物理量;[ C ]表示的是比熱矩陣,包括系統(tǒng)內(nèi)能的增加情況;{ T }為節(jié)點(diǎn)溫度向量;{ T 0 }為溫度對(duì)時(shí)間的導(dǎo)數(shù)。

瞬態(tài)分析相較于穩(wěn)態(tài)分析能夠得到隨時(shí)間變化的一些物理參數(shù),在一些熱-力學(xué)問(wèn)題求解過(guò)程中往往需用瞬態(tài)熱分析求解溫度場(chǎng),再將之作為熱載荷進(jìn)行應(yīng)力分析,瞬態(tài)熱分析需要定義熱傳導(dǎo)系數(shù)、比熱容和密度。對(duì)于一些熱學(xué)問(wèn)題,若僅僅關(guān)注達(dá)到熱平衡狀態(tài)時(shí)的溫度場(chǎng)分布,而不關(guān)注中間時(shí)刻的溫度變化,則選用穩(wěn)態(tài)熱分析計(jì)算更加簡(jiǎn)單高效,穩(wěn)態(tài)熱分析只需要輸入材料的熱傳導(dǎo)系數(shù)。

1.2 熱阻測(cè)試

根據(jù) JESD51-1規(guī)定,半導(dǎo)體器件結(jié)到某參考點(diǎn)的熱阻值 [9] :

式中: T J 是半導(dǎo)體結(jié)溫; T X 是參考點(diǎn)溫度; P H是半導(dǎo)體的熱功耗。根據(jù)實(shí)際需要選擇的不同的參考點(diǎn),可以定義不同的熱阻。功率器件規(guī)格書(shū)上最常見(jiàn)的熱阻參數(shù)是結(jié)殼熱阻 R θJC 和結(jié)到環(huán)境的熱阻R θJA 。所謂 R θJC 就是從半導(dǎo)體芯片的工作部位到距離芯片最近處的封裝體外表面(殼)的熱阻,類似的R θJA 是芯片工作部位到器件周圍的自然對(duì)流(靜止空氣)環(huán)境的熱阻。

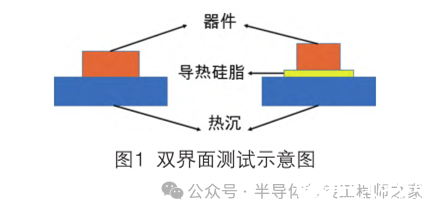

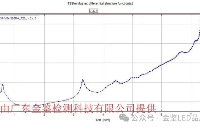

關(guān)于熱阻測(cè)試的方法有很多,本文對(duì)于一些具有空洞缺陷的器件進(jìn)行熱阻測(cè)試,如圖1所示,測(cè)試方法參考JESD51-14標(biāo)準(zhǔn),使用雙界面法,使用D-S間寄生二極管壓降作為熱敏參數(shù)。雙界面法分兩次測(cè)試:第一次測(cè)試是直接將器件接觸到熱沉上,第二次測(cè)試在器件和熱沉之間放置一層導(dǎo)熱硅脂。由于兩次測(cè)試中器件的散熱路徑的改變僅僅發(fā)生在封裝殼體之外,因此兩條熱阻抗曲線的重合部分對(duì)應(yīng)的熱阻抗為熱量在器件內(nèi)部熱阻抗,即結(jié)殼熱阻。

2 試驗(yàn)過(guò)程

2.1 仿真模型建立與計(jì)算

本文研究以某MOSFET器件為研究對(duì)象,對(duì)其通電狀態(tài)下的溫度場(chǎng)進(jìn)行計(jì)算,再通過(guò)器件結(jié)殼溫差計(jì)算熱阻。為了獲得收斂和定性結(jié)果,對(duì)仿真模型進(jìn)行適當(dāng)簡(jiǎn)化,同時(shí)假定各材料間的界面為完全連接的理想狀態(tài)。

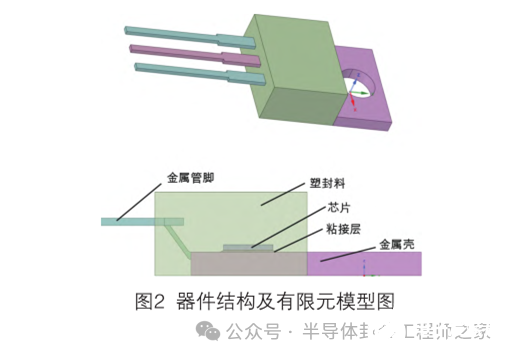

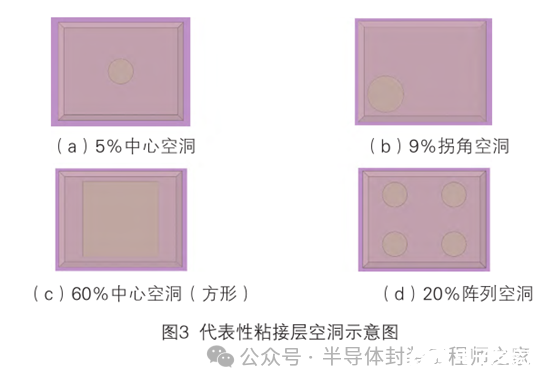

器件幾何模型如圖2所示,結(jié)構(gòu)包括芯片、粘接層、塑封料、金屬殼和金屬管腳,對(duì)粘接層不同空洞率和不同空洞位置定義如圖3所示,空洞位置包括中心、邊角和陣列分布,所有空洞均定義為貫穿型空洞。

在定義材料屬性的時(shí)候,賦予模型各結(jié)構(gòu)材料的熱傳導(dǎo)系數(shù),具體材料屬性見(jiàn)表1。

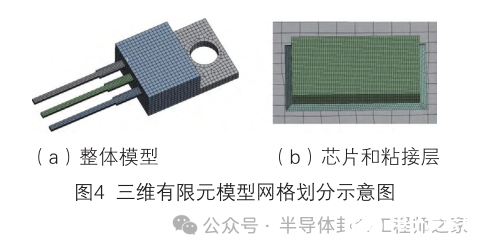

模型劃分網(wǎng)格采用掃掠方式為主、多區(qū)域?yàn)檩o的劃分方式,生成六面體單元,在網(wǎng)格劃分的時(shí)候考慮計(jì)算收斂性和結(jié)果的準(zhǔn)確性,對(duì)芯片和粘接界面的網(wǎng)格進(jìn)行細(xì)化,器件網(wǎng)格劃分結(jié)果如圖4所示。

在進(jìn)行有限元分析時(shí),對(duì)幾何模型做出假設(shè):

1)認(rèn)為芯片為主要的發(fā)熱器件,忽略通電時(shí)其他結(jié)構(gòu)產(chǎn)生的熱量;

2)除去預(yù)先設(shè)定的空洞缺陷之外,認(rèn)為燒結(jié)界面層其他部位結(jié)構(gòu)均勻,沒(méi)有間隙,無(wú)其他缺陷存在;

3)認(rèn)為器件產(chǎn)生的熱量完全由與其接觸的粘接層和塑封料導(dǎo)出;

4)認(rèn)為主要熱交換方式為熱傳導(dǎo)和熱對(duì)流,忽略熱輻射的影響。

針對(duì)應(yīng)用工況,設(shè)置邊界條件為:對(duì)芯片施加10 W的功率,環(huán)境溫度設(shè)定為25 ℃,器件與空氣對(duì)流換熱系數(shù)為5 W/(m 2 ·℃),器件下端與散熱臺(tái)相接觸,給定一個(gè)換熱系數(shù)3 000 W/(m 2 ·℃)作為邊界條件,采用穩(wěn)態(tài)熱分析方式。

2.2 試驗(yàn)樣品制備與測(cè)試條件

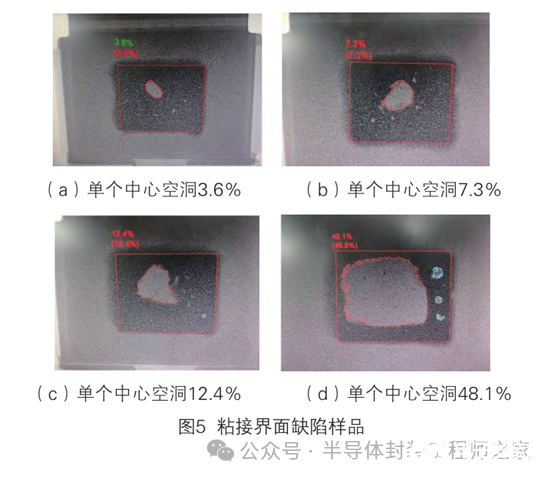

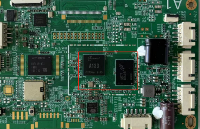

經(jīng)過(guò)工藝調(diào)整之后制備特定位置、一定比例空洞的缺陷樣品,由于缺陷樣品制備具有一定隨機(jī)性,僅以單一中心空洞(忽略大面積空洞周圍的小空洞)缺陷品為試驗(yàn)樣品進(jìn)行熱阻測(cè)試,并與仿真結(jié)果進(jìn)行對(duì)比,代表性圖片空洞分布情況如圖5所示。

對(duì)含有特定缺陷的MOSFET器件進(jìn)行熱阻測(cè)試,通過(guò)改變電子器件的輸入功率,使得器件產(chǎn)生溫度變化,在變化過(guò)程中,測(cè)試出芯片的瞬態(tài)溫度響應(yīng)曲線。具體測(cè)試參數(shù)為:測(cè)試電流50 mA,加熱電流10 A,加熱時(shí)間30 s,降溫時(shí)間60 s。

3 結(jié)果與討論

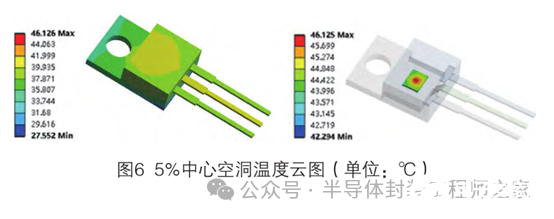

對(duì)不同空洞缺陷的模型分別進(jìn)行熱仿真計(jì)算,圖6為中心5%空洞模型計(jì)算結(jié)果溫度云圖,從圖中可見(jiàn)器件整體及芯片的的溫度分布,在設(shè)定的環(huán)境溫度和功率下,器件芯片作為熱源,只能通過(guò)與塑封料和粘接層的熱傳導(dǎo)才能與外界進(jìn)行熱交換,該部位溫度最高。

從芯片溫度云圖上能看出,溫度分布和粘接層缺陷特征相互對(duì)應(yīng),器件的最高溫度位于芯片中心處,形成了中央溫度高且向四周方向逐漸遞減的溫度分布趨勢(shì),器件溫度最低的區(qū)域?yàn)榕c散熱臺(tái)接觸的金屬面,與散熱臺(tái)的快速熱交換使其溫度快速下降,在熱穩(wěn)定狀態(tài)下,其溫度接近于室溫,但由于器件殼體表面溫度相差太大,任意取一個(gè)節(jié)點(diǎn)的溫度無(wú)法完全代表殼體溫度,因此以有限元計(jì)算所得的殼體單元平均溫度為殼溫,通過(guò)給定功率和結(jié)殼溫差計(jì)算結(jié)殼熱阻,對(duì)比粘接層不同空洞缺陷對(duì)應(yīng)器件結(jié)殼熱阻的差異。

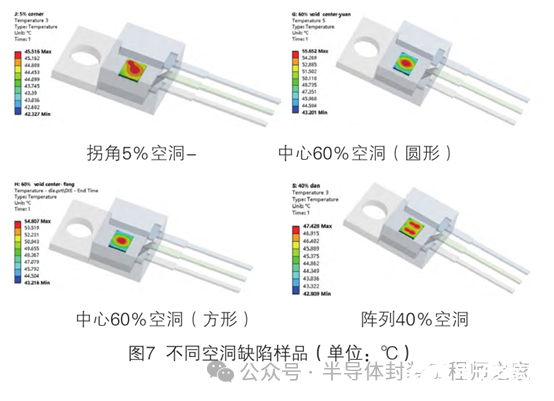

圖7為不同空洞缺陷燒結(jié)界面對(duì)應(yīng)的和芯片溫度分布云圖,從云圖溫度分布形態(tài)一定程度上反映了空洞的缺陷類型,相較于粘接層,空洞的導(dǎo)熱率很低,隨著空洞面積增大,溫度傳導(dǎo)熱阻越大,芯片散熱性能越差,對(duì)應(yīng)的芯片結(jié)溫越高。

不同空洞率的燒結(jié)界面缺陷計(jì)算的芯片溫度和殼體溫度數(shù)據(jù)及計(jì)算得出的熱阻值見(jiàn)表2。

對(duì)比相同空洞率但空洞位置不同器件的熱阻大小,發(fā)現(xiàn)當(dāng)空洞處于拐角處時(shí),器件熱阻更小。

由于芯片的發(fā)熱由中心四周散開(kāi),當(dāng)空洞位于中心時(shí),芯片中心熱量有兩種傳遞方式:一種是沿空洞垂直傳導(dǎo),一種是先水平傳導(dǎo)至無(wú)空洞區(qū),再沿著粘接界面垂直傳導(dǎo)于器件底部。由于空洞熱導(dǎo)率小,顯然第一種傳導(dǎo)方式熱阻大;而當(dāng)空洞位于拐角處時(shí),芯片中心熱量則可直接沿著中心垂直傳導(dǎo),而拐角處熱量較少,沿著空洞傳導(dǎo)。綜上所述空洞在中心處時(shí)熱量傳導(dǎo)效率比空洞在拐角處要低,器件熱阻較大。

分析不同陣列空洞仿真結(jié)果可知,隨著陣列空洞占比增大,器件熱阻增大,規(guī)律與單一空洞一致,空洞范圍越大,熱量傳導(dǎo)越困難。與單一空洞相比,陣列空洞將大空洞分成了四個(gè)對(duì)稱的小空洞,通過(guò)表2中數(shù)據(jù)對(duì)比可知,總空洞率一致時(shí),大空洞器件熱阻要比多個(gè)小空洞器件熱阻大,在各個(gè)小空洞之間存在完整的粘接層,熱量可通過(guò)空洞之間的粘接層垂直傳熱,熱量傳導(dǎo)效率更高。

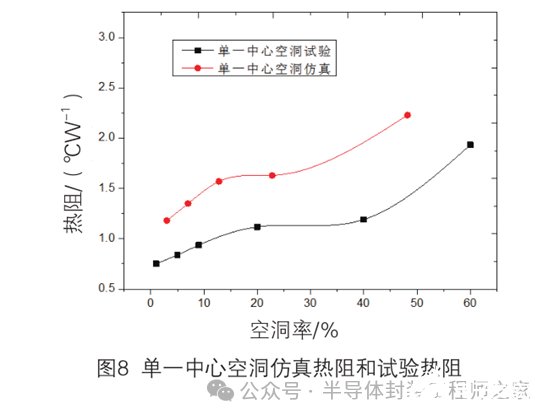

針對(duì)具有中心單一空洞的缺陷器件,熱阻測(cè)試結(jié)果見(jiàn)表3,將中心空洞對(duì)應(yīng)仿真計(jì)算結(jié)果與試驗(yàn)數(shù)據(jù)進(jìn)行對(duì)比,擬合如圖8所示,從圖中可以看出仿真與試驗(yàn)趨勢(shì)基本吻合,但由于仿真處于完全理想化的狀態(tài),試驗(yàn)又無(wú)法避免一定的環(huán)境與設(shè)備誤差,二者在量值上存在一定的差異。

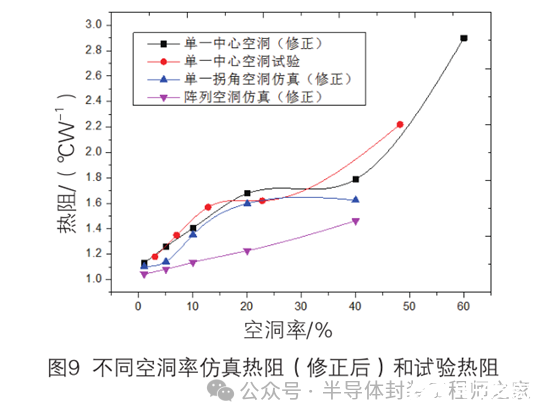

依據(jù)試驗(yàn)數(shù)據(jù),將仿真數(shù)據(jù)曲線逼近于試驗(yàn)數(shù)據(jù)曲線,修正仿真曲線,修正后曲線如圖9所示。從圖中中心單一空洞曲線圖可知,仿真與試驗(yàn)趨勢(shì)基本吻合;對(duì)于其他空洞分布類型,由于缺陷試驗(yàn)樣品的梯度不充分,僅展示仿真結(jié)果,通過(guò)中心單一空洞這一分布類型進(jìn)行類比修正仿真曲線。

伴隨著空洞率的增大,器件熱阻整體呈現(xiàn)隨之增大的趨勢(shì),空洞率在20%以下和40%以上時(shí),熱阻增大趨勢(shì)很明顯,空洞率在20%~40%之間時(shí),熱阻增大的趨勢(shì)則不明顯。當(dāng)空洞率在20%以內(nèi)時(shí),器件的熱阻隨著空洞率增大而增大,當(dāng)空洞率在20%~40%之間時(shí),器件熱阻隨空洞率增大而減少;當(dāng)空洞率在40%以上,器件熱阻隨空洞率增大而增大,當(dāng)燒結(jié)界面空洞率達(dá)到一定值時(shí),器件的熱阻將會(huì)有一個(gè)非常急劇的升高,嚴(yán)重影響芯片的散熱性能。

對(duì)于單一中心空洞,修正后的仿真和試驗(yàn)曲線吻合度較高,同時(shí)可以直觀地看出中心空洞、拐角空洞、陣列空洞對(duì)于熱阻影響的不同。對(duì)于相同空洞率,器件熱阻呈現(xiàn)的規(guī)律為中心空洞>拐角空洞>陣列空洞。一般來(lái)說(shuō),器件本身對(duì)于熱阻的上限是有規(guī)定的,通過(guò)修正后的曲線能夠?qū)⒄辰用婵斩春推骷嶙杞⑤^準(zhǔn)確的關(guān)系,對(duì)于控制器件的熱阻具有很好的指導(dǎo)意義。

4 結(jié)論

本研究對(duì)缺陷MOSFET器件進(jìn)行了熱分析模擬和熱阻測(cè)試,得出器件結(jié)溫和殼溫,并結(jié)合功率計(jì)算MOSFET器件的熱阻值,主要研究結(jié)果為:

1)芯片粘接界面的空洞占比越大,器件的結(jié)殼溫差越大,器件的熱阻值越大。

2)相同空洞率時(shí),空洞位置在中心相較于在拐角處,器件熱阻更大,單一空洞相較于陣列空洞器件熱阻更大。

3)通過(guò)熱阻實(shí)測(cè)數(shù)據(jù)修正仿真曲線,二者吻合度較高,根據(jù)修正后的曲線可以預(yù)測(cè)不同位置空洞和空洞率不合格的器件熱阻,并提供一定工藝指導(dǎo)。

審核編輯 黃宇

-

熱阻

+關(guān)注

關(guān)注

1文章

114瀏覽量

16855 -

功率芯片

+關(guān)注

關(guān)注

0文章

112瀏覽量

15647

發(fā)布評(píng)論請(qǐng)先 登錄

LED封裝器件熱阻測(cè)試與散熱能力評(píng)估

粘接聚酰亞胺PI膜除了使用PI膜專用UV膠粘接,還可以使用熱固化環(huán)氧膠來(lái)解決!

精通芯片粘接工藝:提升半導(dǎo)體封裝可靠性

濕度大揭秘!如何影響功率半導(dǎo)體器件芯片焊料熱阻?

功率器件熱設(shè)計(jì)基礎(chǔ)知識(shí)

無(wú)鉛錫膏焊接空洞對(duì)倒裝LED的影響

功率器件熱設(shè)計(jì)基礎(chǔ)(九)——功率半導(dǎo)體模塊的熱擴(kuò)散

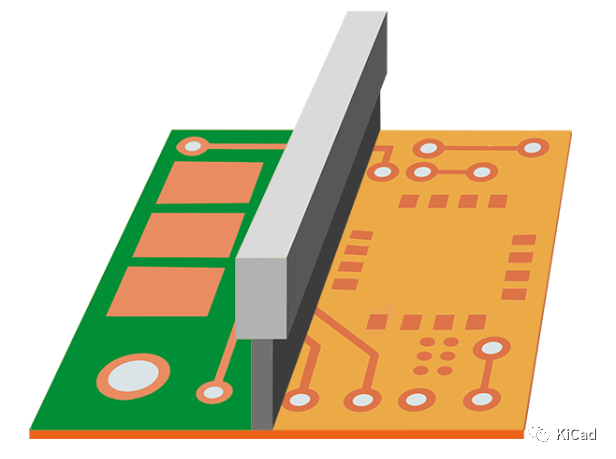

KiCad中的阻焊層及其應(yīng)用

導(dǎo)熱界面材料對(duì)降低接觸熱阻的影響分析

功率器件的熱設(shè)計(jì)基礎(chǔ)(二)——熱阻的串聯(lián)和并聯(lián)

功率器件熱設(shè)計(jì)基礎(chǔ)(一)——功率半導(dǎo)體的熱阻

阻焊層解析:PCB的“保護(hù)傘”是什么?

干貨!PCB Layout 熱設(shè)計(jì)指導(dǎo)

了解具有集成功率MOSFET的直流/直流轉(zhuǎn)換器熱阻規(guī)格

粘接層空洞對(duì)功率芯片熱阻的影響

粘接層空洞對(duì)功率芯片熱阻的影響

評(píng)論