AD9361是一款高性能的射頻前端芯片,廣泛應用于無線通信系統中。其中一個重要特性是其具有靈活可調的ADC采樣率。本文將詳細介紹AD9361的ADC采樣率設置范圍,包括其相關特性、設置方法以及在實際應用中的注意事項等。

- ADC采樣率簡介

ADC(Analog-to-Digital Converter)即模數轉換器,是一種將模擬信號轉換為數字信號的設備。在無線通信系統中,ADC常用于將射頻信號轉換為數字信號,以便進行數字信號處理和分析等操作。ADC的采樣率是指每秒鐘采集的樣本數,通常以Hz為單位。較高的采樣率可以提供更準確和詳細的信號表示,但同時也需要更大的計算和存儲資源。 - AD9361芯片簡介

AD9361是ADI(Analog Devices Inc.)推出的一款集成了大量無線通信功能的射頻前端芯片。它支持多種無線通信標準,如GSM、WCDMA、LTE等,并且擁有極高的性能和靈活性。在AD9361芯片中,ADC是用于將射頻信號轉換為數字信號的關鍵部件。 - AD9361的ADC采樣率設置范圍

AD9361芯片具有非常靈活的ADC采樣率設置范圍,可以根據實際需求進行調整。其最小采樣率約為520 ksps(千樣本每秒),最大采樣率約為61.44 Msps(兆樣本每秒)。用戶可以通過編程配置AD9361的寄存器來設置所需的采樣率。具體的設置方法可以參考AD9361的數據手冊和編程指南。 - ADC采樣率的選擇

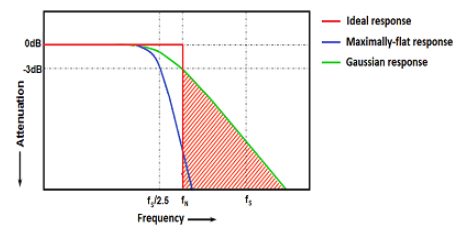

在選擇ADC采樣率時,需要綜合考慮系統的要求和資源限制。較高的采樣率可以提供更高的精度和細節,但同時也會增加數據處理和存儲的負擔。因此,在實際應用中,需要根據信號的帶寬和系統的要求來選擇合適的采樣率。一般來說,采樣率應該大于信號帶寬的兩倍,以滿足尼奎斯特定理的要求。 - ADC采樣率設置的注意事項

在進行ADC采樣率設置時,需要注意以下幾個方面:

- AD9361的ADC采樣率設置需要與數字信號處理系統的其他參數相匹配,如處理器的計算能力和存儲資源等。否則,可能導致數據處理能力不足或者資源浪費。

- 需要根據射頻信號的帶寬和調制方式來選擇合適的ADC采樣率。較高的采樣率可以提供更好的信號還原效果,但同時也會增加功耗和計算負擔。

- 在進行高速采樣時,需要注意時鐘和同步的穩定性。AD9361對于時鐘和同步信號的質量要求比較高,需要采取相應的措施來避免時鐘抖動和時鐘偏差等問題。

綜上所述,AD9361是一款具有靈活可調的ADC采樣率的射頻前端芯片。其采樣率設置范圍廣泛,用戶可以根據實際需求進行配置。在設置時,需要綜合考慮系統的要求和資源限制,并注意時鐘和同步的穩定性。通過合理設置ADC采樣率,可以提高無線通信系統的性能和靈活性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

459文章

52160瀏覽量

436070 -

adc

+關注

關注

99文章

6635瀏覽量

548233 -

無線通信

+關注

關注

58文章

4706瀏覽量

144849 -

射頻前端

+關注

關注

5文章

257瀏覽量

24670

發布評論請先 登錄

相關推薦

熱點推薦

請問AD9361 ADC的采樣率是多少?

把基帶接收到的信號存儲起來做頻譜分析,但不確定數據的采樣率是多少?有個122.88MHz,還有個30.72MHz,到底哪個是采樣率呢?它們有什么關系?希望有人能回答一下,謝謝!

發表于 09-19 10:08

請問AD9361的DATA_CLK和ADC COLCK RATE的關系是什么?

@@最近在調試AD9361的BBPLL,目前BB PLL 已經鎖定。但不知道DATA_CLK這個時鐘怎么配置?和ADC 的采樣率有什么關系?參考時鐘為40MHz,配置的ADC CLK

發表于 10-16 10:28

請問AD9361最大的AD和DA采樣率是多少?

從AD9361手冊上看到DATA_clock是最大速率是61.44M,但是在的adfcomms2的說明文檔overview中顯示的是顯示著AD采樣率是64MSPS。請問AD9361最大的AD和DA

發表于 12-12 09:37

請問AD9361的AD配置需要注意什么?

我在配置A9361的時候被難在了AD采樣上面。我按照給的寄存器配置順序配置的AD9361,發射已經OK。接收可以接收到信號,但是接收在沒有信號的時候總是有很大的一個干擾信號在里面。我的基帶采樣

發表于 03-01 10:10

基于ADI AD9361模塊AD-FMCOMMS3-EBZ搭建的AD9361 RF收發測試平臺案例

AD9361芯片工作頻率范圍為70 MHz至6 GHz,涵蓋大部分特許執照和免執照頻段,通過對AD9361自身可編程改變采樣速率、數字濾波器和抽取參數,使該芯片支持的通道帶寬

adc采樣率和帶寬的關系

adc采樣率和帶寬的關系 ADC(Analog-to-Digital Converter),即模擬轉數字轉換器,是將模擬信號轉換成數字信號的重要器件。其中,采樣率和帶寬是

如何優化adc的采樣率

在數字信號處理領域,ADC是將模擬信號轉換為數字信號的關鍵組件。采樣率,即ADC每秒采集樣本的次數,對信號的準確性和系統的整體性能有著直接的影響。 ADC

ad9361 ADC采樣率設置范圍

ad9361 ADC采樣率設置范圍

評論