在進行布局約束前,通常會對現有設計進行設計實現(Implementation)編譯。在完成第一次設計實現編譯后,工程設計通常會不斷更新迭代,此時對于設計中一些固定不變的邏輯,設計者希望它們的編譯結果能夠保持穩定不變,使用增量式編譯是一種選擇,而使用布局約束是另一種更靈活的選擇。此時的布局約束,通常不會針對用戶邏輯部分,而是針對一些相對固定的片內存儲器或乘法器,基于第一次編譯的結果進行固定布局約束的設計重用,保證后續每次新的編譯不再改變其布局位置,從而達到獲得相對穩定的編譯結果的目的。

這類基于設計重用的布局約束,簡單易用,可以減少一定的編譯時間,也無需設計者對底層器件結構非常了解。但也有其局限性,不適用于較大的設計變更,也不適合于固定太多的設計邏輯。因為這類設計重用,相當于為前期設計鎖定了資源,使其占據了先發優勢,而對于隨后的設計變更,則因為無法分配到較優的資源,可能引起時序違規。因此,在實際工程應用中,此類固定布局約束需要謹慎使用。

點擊OpenImplemented Design,進入Implemented頁面。

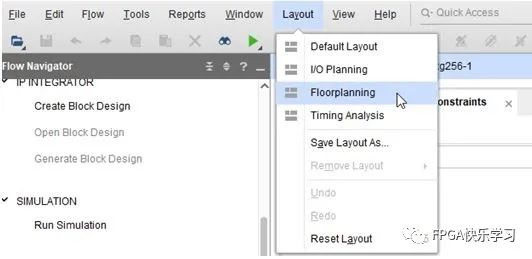

Implemented頁面下,如圖1所示,點擊菜單Layout->Floorplanning。

圖1Floorplanning菜單

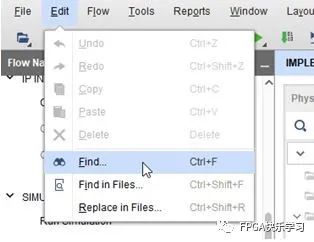

接著,如圖2所示,點擊菜單Edit->Find。

圖2 Find菜單

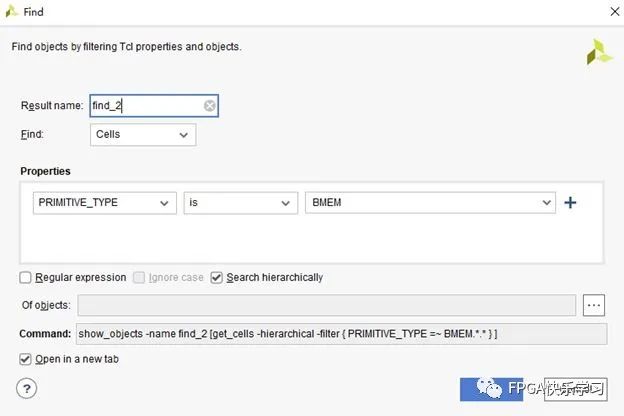

如圖3所示,在彈出的Find對話框中,設置Find為Cells,Properties為PRIMITIVE_TYPEis BMEM。即查找設計中已經布局的所有Block Memory(FPGA片內塊RAM)。

圖3 Find對話框

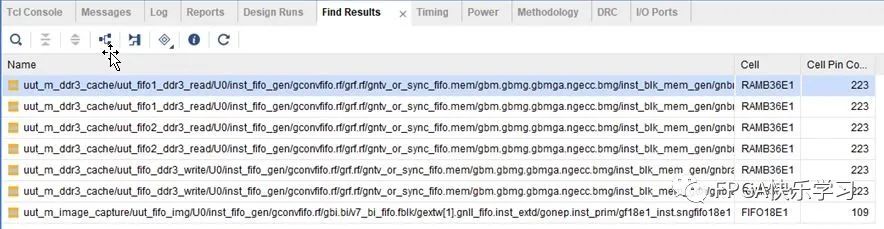

此時,如圖4所示,在FindResults列表中,出現了所有搜索到的設計中使用了BMEM的Cell。

圖4 FindResults列表

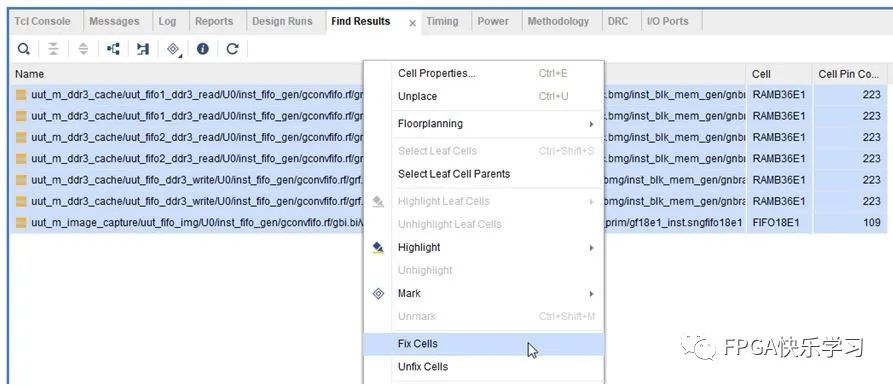

如圖5所示,選中所有搜索到的RAMB36E1,右鍵單擊,彈出菜單中點擊FixCells,將所有已布局的BMEM的位置固定,使其在下一次編譯時不被移動。

圖5 FixCells菜單

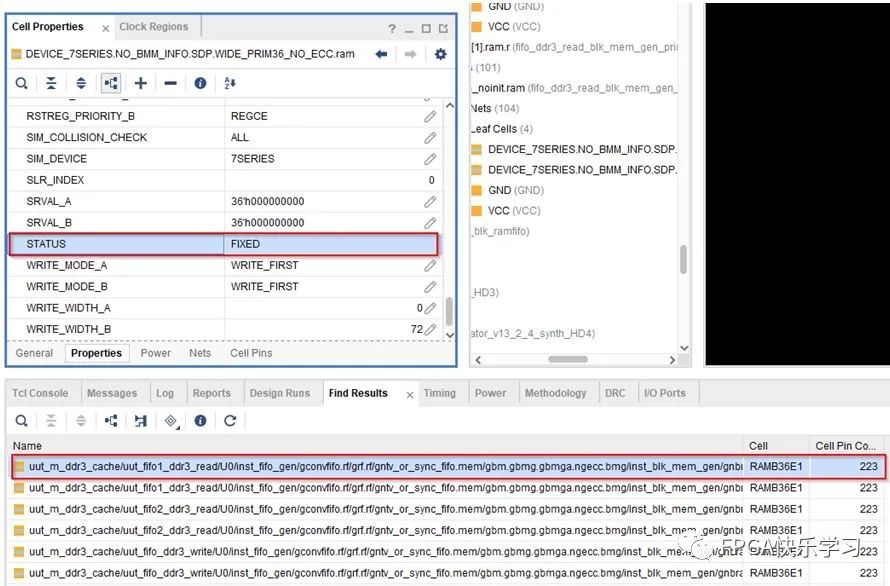

如圖6所示,可以選擇FindResults中的任意一個Cell,查看其Cell Properties,其STATUS項都已被修改為了FIXED。

圖6查看BMEM屬性

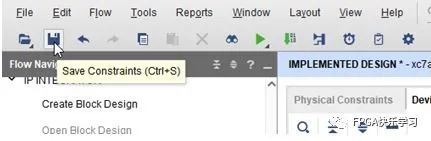

如圖7所示,可以直接點擊保存按鈕,覆蓋到當前的xdc文件中。

圖7SaveConstraints按鈕

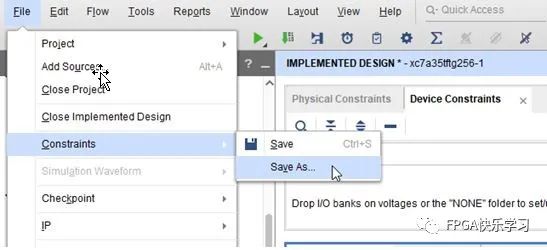

如圖8所示,也可以點擊菜單File->Constraints->SaveAs創建新方案存儲約束腳本。

圖8SaveConstraints As菜單

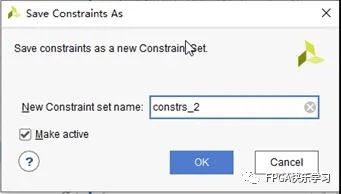

如圖9所示,新的約束設置將會另存到新創建的約束方案constrs_2中。

圖9SaveConstraints As對話框

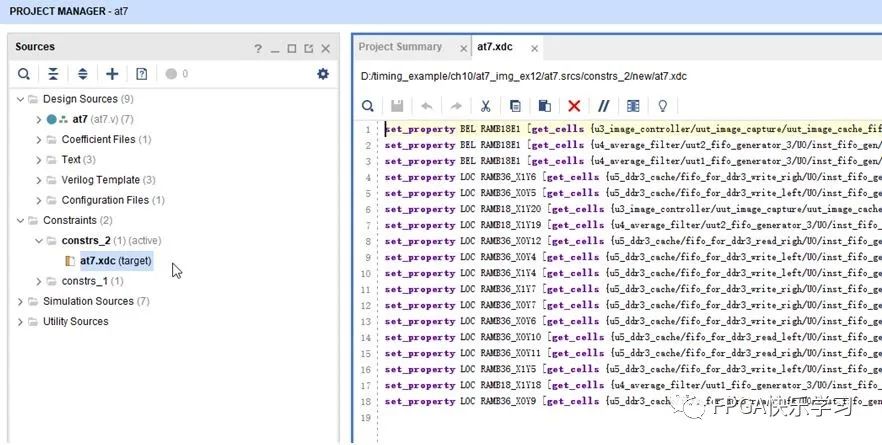

最后,如圖10所示,在Source面板中可以看到,新創建的約束方案constrs_2被高亮為active狀態,同時打開其下的約束文件at7.xdc,set_property BEL或set_property LOC腳本即剛添加的布局約束。重新編譯后,約束將會生效。

圖10約束腳本文件

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618379 -

存儲器

+關注

關注

38文章

7651瀏覽量

167376 -

約束

+關注

關注

0文章

82瀏覽量

12969 -

編譯

+關注

關注

0文章

679瀏覽量

33983

原文標題:物理約束實踐:基于設計重用的布局約束

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA時序約束之建立時間和保持時間

FPGA物理約束之布線約束

FPGA時序約束的幾種方法

FPGA時序約束的幾種方法

物理約束之布局約束

【MiniStar FPGA開發板】配套視頻教程——Gowin進行物理和時序約束

基于FPGA 和 SoC創建時序和布局約束以及其使用

FPGA設計約束技巧之XDC約束之I/O篇(下)

FPGA物理約束之布局約束

FPGA物理約束之布局約束

評論