AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統(tǒng)外設(shè)上生成特定序列(流量)。它根據(jù)IP的編程和選擇的操作模式生成各種類型的AXI事務(wù)。是一個比較好用的AXI4協(xié)議測試源或者AXI外設(shè)的初始化配置接口。

ATG(AXI Traffic Generator)IP的GUI如下圖所示。

AXI Traffic Generator是一個完全可綜合的符合AXI4標(biāo)準(zhǔn)的核心,具有以下特點:

- 可根據(jù)不同的流量配置選項生成和接受數(shù)據(jù)。

- 可配置的主AXI4接口地址寬度。

- 支持讀/寫主端口之間的相關(guān)/獨立事務(wù),并具有可配置的延遲。

- 可編程的重復(fù)計數(shù),對于每個事務(wù)可以使用恒定/遞增/隨機地址。

- 在AXI接口上為預(yù)定義的協(xié)議生成特定IP流量。

該IP的主要特性為:

- AXI4 接口適用于寄存器訪問和數(shù)據(jù)傳輸;

- 支持多種模式工作(AXI4 Master,AXI4-Lite Master, and AXI4-Stream Master);

- 高度靈活的數(shù)據(jù)位寬:32/64/128/256/512 axistream:8-1024;

- 高度靈活的地址位寬:32-64;

- 可為處理器資源較少系統(tǒng)中的系統(tǒng)初始化提供 AXI4-Lite 主接口支持;

- 中斷引腳,指示內(nèi)核已完成流量生成;

- 錯誤中斷引腳,指示內(nèi)核工作期間出現(xiàn)的錯誤。可通過讀取錯誤寄存器,了解所出現(xiàn)的錯誤;

- 內(nèi)部 RAM(CMDRAM、PARAMRAM 和 MSTRAM)的初始化支持允許用戶針對所需的流量特性分析初始化所有 RAM 的內(nèi)容;

它支持6種工作模式:

如下圖所示,在IP生成的時候可以在AXI4選項下選擇Advanced、Basic、Static三種模式;

AXI4-Stream模式如下圖所示:

如下圖所示,在IP生成的時候AXI4-Lite選項可以選擇System Init和Test Mode兩種模式;

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613989 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123300 -

接口

+關(guān)注

關(guān)注

33文章

8932瀏覽量

153189 -

Xilinx

+關(guān)注

關(guān)注

73文章

2181瀏覽量

124326 -

AXI

+關(guān)注

關(guān)注

1文章

134瀏覽量

17089

發(fā)布評論請先 登錄

Xilinx zynq AXI總線全面解讀

ARM+FPGA開發(fā):基于AXI總線的GPIO IP創(chuàng)建

XILINX FPGA IP之Clocking Wizard詳解

XILINX FPGA IP之MMCM PLL DRP時鐘動態(tài)重配詳解

Xilinx FPGA IP之Block Memory Generator功能概述

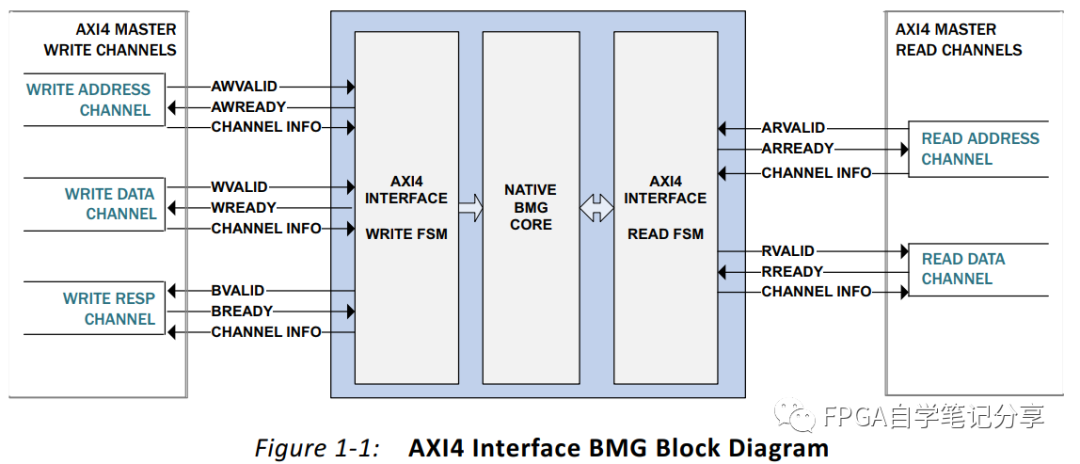

Xilinx FPGA IP之Block Memory Generator AXI接口說明

Xilinx FPGA片內(nèi)ROM實例之ROM配置

AXI 代碼 不通過 AXI Protocol Checker IP 的檢測

Xilinx的LogiCORE IP Video In to AXI4

FPGA開發(fā)之算法開發(fā)System Generator

如何使用Xilinx AXI進行驗證和調(diào)試

FPGA AXI4協(xié)議學(xué)習(xí)筆記(二)

FPGA AXI4協(xié)議學(xué)習(xí)筆記(三)

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

XILINX FPGA IP之AXI Traffic Generator

XILINX FPGA IP之AXI Traffic Generator

評論