概述

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于EMIF通信,也可方便地實現 PL (FPGA)和 PS (MicroBlaze或者ARM)之間的數據交互功能。

本文主要介紹一下該IP核的使用,以及創建Vivado工程對EMIF通信功能進行板上測試。

軟硬件平臺

軟件平臺 :Vivado 2017.4;

硬件平臺 :xc7a35tftg256-1;

AXI-EMC

功能特性

AXI-EMC IP核是一種可以支持各種型號內存的控制器,和EMIF接口類似,利用它可以實現數據的交互和通信。該IP核有以下功能特性:

- 接口采用AXI4 Slave Memory Map,位寬支持32、64bits;

- 支持AXI4增量和包傳輸,支持窄帶和非對其傳輸;

- 最多支持4個外部存儲器;

- 支持奇偶校驗和流水線級同步SRAM等;

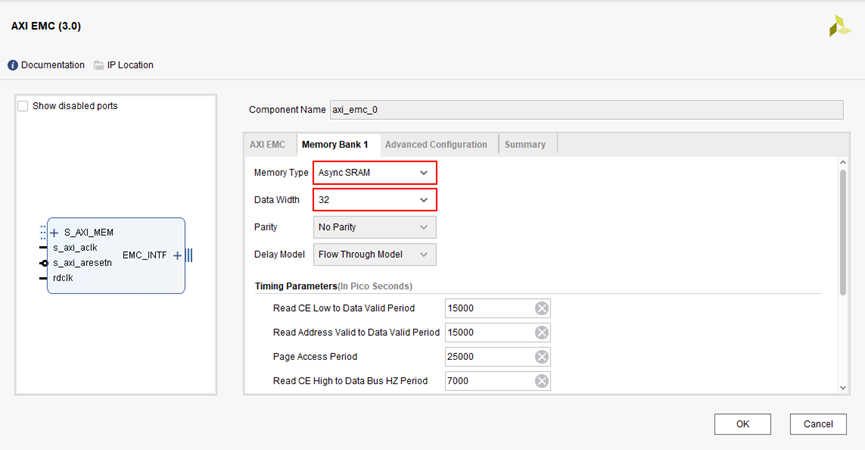

參數配置

- AXI Data Width:AXI總線位寬選擇32位;

- Number of Memory Banks:存儲器個數這里選擇1即可;

- AXI ID位寬和存儲空間地址選擇默認配置;

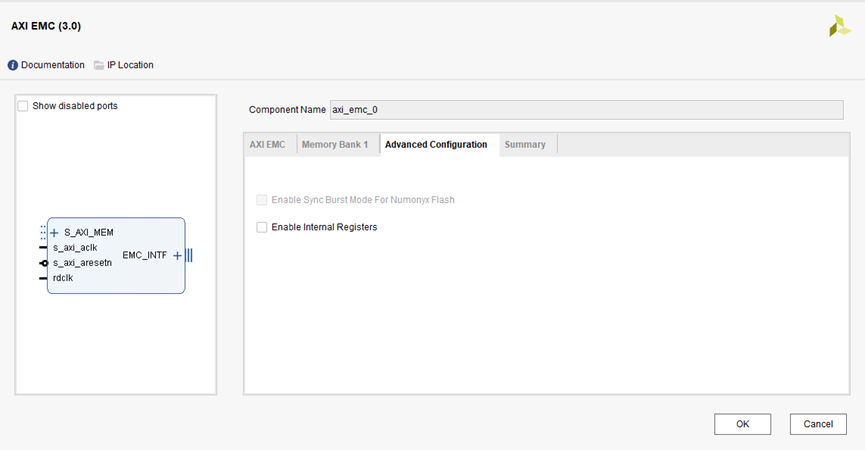

- Advanced Configuration:高級配置選項保持默認,不用配置IP核內部寄存器;

Vivado工程創建

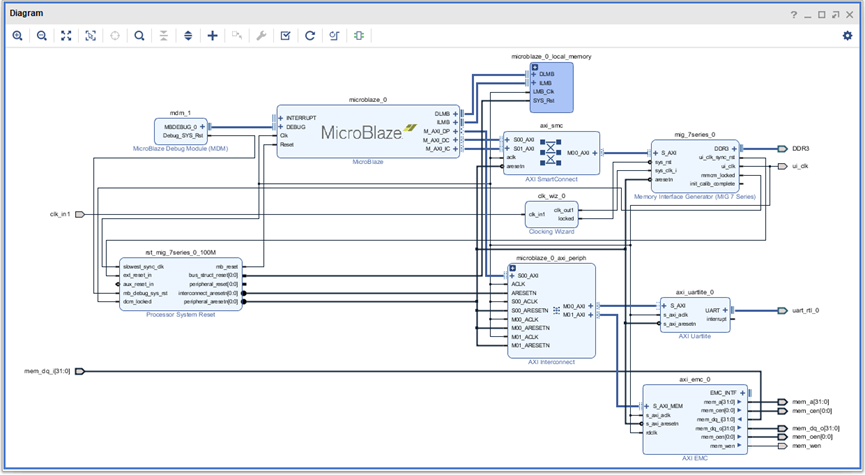

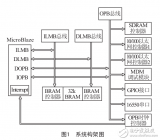

本工程是在MicroBlaze最小系統工程基礎上進行創建,利用AXI-EMC在MicroBlaze軟核端對FPGA端進行EMIF數據讀寫,進而實現PS和PL端數據交互功能。

搭建Block Design

- 在MicroBlaze最小系統的Block Design工程中添加AXI-EMC IP核,并對參數進行配置;

- 將IP核的 rdclk 接口以及 s_axi_aclk 接口與MIG IP提供的100MHZ用戶時鐘接口 ui_clk 進行連接;

- 將 mem_a (地址)、 mem_cen (片選)、 mem_dq_o (輸出數據)、 mem_dq_i (輸入數據)、 mem_oen (讀使能)、 mem_wen (寫使能)接口引出,在頂層文件中會進行調用。

最終搭建完成的Block Design如下圖所示:

修改頂層文件

在生成的頂層文件中添加以下代碼,用于實現FPGA端基本的EMIF通信功能,以及添加ILA模塊實現對EMIF接口信號的實時觀察。

reg [31:0] data_reg,mem_dq_i_reg;

reg [2:0] mem_wen_r,mem_oen_r;

assign mem_dq_i = mem_dq_i_reg;

always@(posedge ui_clk) begin

mem_wen_r <= {mem_wen_r[1:0],mem_wen};

mem_oen_r <= {mem_oen_r[1:0],mem_oen};

end

always@(posedge ui_clk)

if(mem_wen_r[2:1] == 2'b10) begin

case(mem_a[17:2])

16'h5555:

data_reg <= mem_dq_o;

default:

data_reg <= data_reg;

endcase

end

always@(posedge ui_clk)

if(mem_oen_r[2:1] == 2'b10) begin

case(mem_a[17:2])

16'haaaa:

mem_dq_i_reg <= data_reg;

default:

mem_dq_i_reg <= mem_dq_i_reg;

endcase

end

ila_0 ila_0_u0

(

.clk (ui_clk),

.probe0 (mem_a),

.probe1 (mem_cen),

.probe2 (mem_dq_i),

.probe3 (mem_dq_o),

.probe4 (mem_oen),

.probe5 (mem_wen),

.probe6 (uart_rtl_0_txd)

);

創建SDK工程

在SDK軟件中,采用Xilinx提供的Hello World工程,在helloworld.c文件中添加以下代碼,用于實現MicroBlaze軟核每隔一定時間在FPGA端0x55554地址下寫入32位十進制數據:111,并從0xaaaa4地址將該數據讀出。

#include < stdio.h >

#include "platform.h"

#include "xil_io.h"

#include "xparameters.h"

#include "xuartlite.h"

#include "xuartlite_l.h"

int ii,data;

int main()

{

init_platform();

print("EMIF TESTnr");

while(1)

{

Xil_Out32(XPAR_EMC_0_S_AXI_MEM0_BASEADDR+0x5555*4,111);

data=Xil_In32(XPAR_EMC_0_S_AXI_MEM0_BASEADDR+0xaaaa*4);

for(ii=0;ii< 100;ii++);

}

cleanup_platform();

return 0;

}

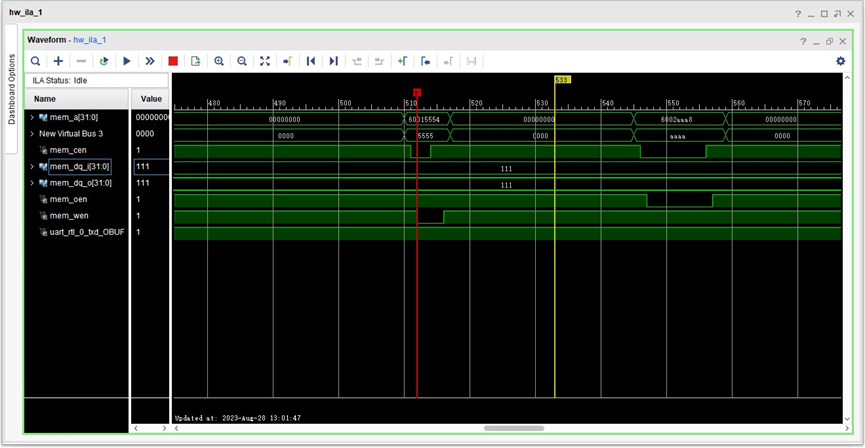

功能測試

該Vivado工程利用AXI-EMC IP核實現異步SRAM接口,在MicroBlaze軟核CPU和FPGA之間進行基礎的EMIF通信。該工程為實現PS和PL之間的數據交互功能提供一種很好的思路。

FPGA板上測試結果如上圖所示,MicroBlaze軟核往FPGA 0x55554地址下寫入32位十進制數據111,FPGA將該數據進行寄存,供軟核從0xaaaa4地址下讀出。

-

處理器

+關注

關注

68文章

19813瀏覽量

233614 -

dsp

+關注

關注

555文章

8144瀏覽量

355338 -

FPGA

+關注

關注

1643文章

21968瀏覽量

614295 -

存儲器

+關注

關注

38文章

7637瀏覽量

166453 -

通信

+關注

關注

18文章

6177瀏覽量

137384 -

Xilinx

+關注

關注

73文章

2182瀏覽量

124385

發布評論請先 登錄

Xilinx zynq AXI總線全面解讀

XILINX FPGA IP之AXI Traffic Generator

請教DSP的EMIF總線和ARM的AXI總線轉換的問題

請問KC705上的AXI EMC核心硬件測試例子哪里可以找到?

AXI 代碼 不通過 AXI Protocol Checker IP 的檢測

使用EMIF將Xilinx FPGA與TI DSP平臺接口

Xilinx的LogiCORE IP Video In to AXI4

基于TCP/IP通信技術在Xilinx FPGA上的實現

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

評論