什么是DFX技術?

DFX(Dynamic Function eXchange)的前身是PR(部分可重配置,Partial Reconfiguration)。使用DFX這個名字更能準確描述其功能,即在線切換設計中某個模塊的功能。我們把這個模塊對應的FPGA物理區域稱之為一個可重配置分區(RP,ReconfigurablePartition)。同一個RP下可動態切換的模塊稱之為可重配置模塊(RM,Reconfigurable Module)。一個RP下可以有一個或多個RM。每個RP要通過手工布局(畫Pblock)的方式指定其在FPGA中的具體位置和大小(位置約束+面積約束)。

DFX對RM有什么要求?

首先,同一個RP下的所有RM必須保證端口一致,即輸入/輸出方向一致、位寬一致。即使某個RM中使用的端口在另一個RM中未被使用,也要在該RM中進行端口聲明。其次,本身DFX設計對設計的層次化要求更高,對RM必須采用OOC綜合方式,因此,要避免在RM中使用Parameter(Verilog)或Generic(VHDL)。最后,RM的頂層必須是RTL代碼(可以是BD的wrapper文件),不能是IP或著網表文件,同時RM下不能包含EDIF或DCP等網表文件,但可以包含IP(.xci)文件。

需要對RP進行手工布局嗎?

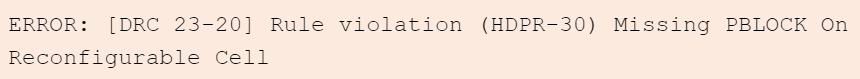

DFX設計要求必須對動態區也就是RP進行手工布局,即通過Pblock來約束RP的位置和大小,同時Pblock的形狀盡可能為規則的矩形,避免出現奇形怪狀,這會對布局布線帶來較大壓力。對于靜態區,則可以不用手工布局。如果對動態區沒有做Pblock約束,那么會報如下錯誤:

?

?

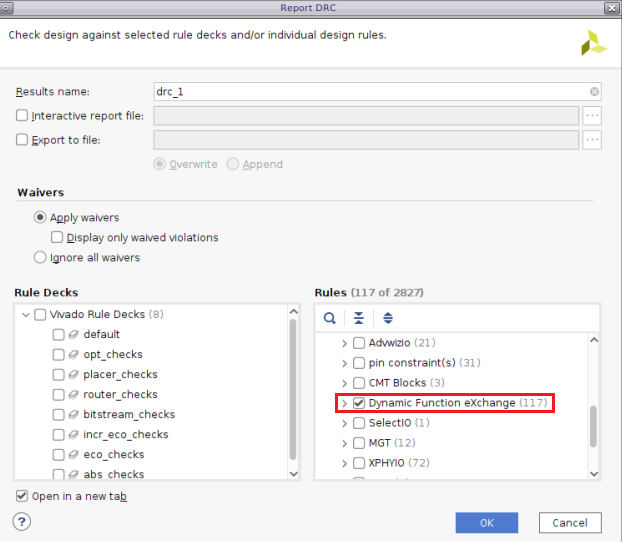

DFX設計一定要執行設計規則檢查嗎?

相比于傳統設計,DFX設計較為復雜,無論是從設計本身(RTL代碼的層次化、約束)的角度看還是工具的使用角度看,都是如此。因此,在綜合后,一定要執行設計規則檢查,如下圖所示。這樣能盡早發現設計可能存在的問題。這里并不需要對所有規則都做檢查,只需要檢查DFX相關的規則即可。這樣可以節省時間。

可以對同一RP下不同的RM添加不同的約束嗎?

假定RP1下有兩個RM,分別為RM1和RM2,由于RM1和RM2本身功能并不相同,因此可能就存在一些約束層面的差異。例如:在RM1里需要對某些路徑添加set_max_delay約束,在RM2里則需要對一些路徑添加set_false_path約束。這就要求對不同的RM施加不同的約束。對此,Vivado是支持的,無論是Project模式還是Non-Project模式。具體操作可閱讀這篇文章。

如何給每個RM添加約束?

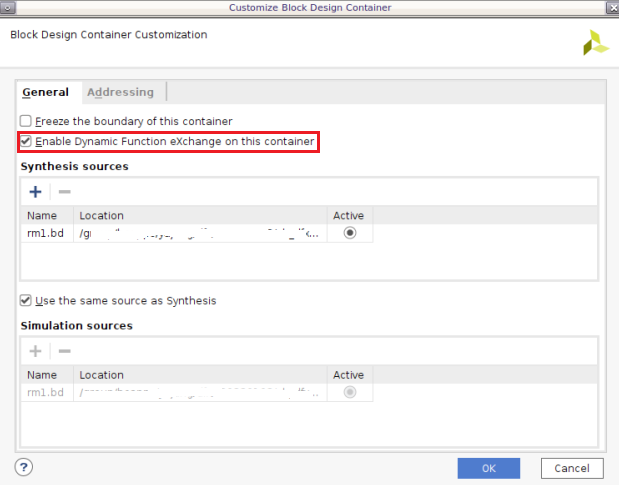

BD可以用作動態區的頂層嗎?

這個問題的本質是RM是否可以用BD創建。答案是肯定的。只是這時需要將BD設計轉換為BDC(Block Design Container),勾選下圖中的紅色方框所示內容即表明該模塊是一個RM。

除了上述幾個問題之外,我們還需要從以下角度來看待DFX設計。

DFX設計本質上是FPGA內嵌入了FPGA,也就是說RP可視為一個內嵌的FPGA,那么這個RP的可用邏輯資源、布線資源和IO也就固定了。正因此,RP的Pblock的大小和形狀對設計性能有較大影響,同時,RM的輸出/輸出端口個數應盡可能少,過多的IO個數大概率會導致布線擁塞。因此,同樣的設計,使用DFX和不使用DFX可能會有不同的時序結果。層次化設計在DFX設計中也非常重要,將直接影響合動態區和靜態區的分割。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21956瀏覽量

614016 -

VHDL語言

+關注

關注

1文章

113瀏覽量

18506 -

RTL

+關注

關注

1文章

388瀏覽量

60661 -

DCP

+關注

關注

0文章

30瀏覽量

17496 -

dfx設計

+關注

關注

0文章

6瀏覽量

168

原文標題:DFX設計中的常見問題

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DFX設計如何分析

招兼職dfx、dfm培訓講師

硬件電路設計中常見的DFX

硬件電路常見的DFX設計環節詳解

簡述DFX理念與產品研發(一)

簡要分析DFX實施流程

DFX極大地提高了Xilinx FPGA芯片的靈活性

2021華為開發者大會亮點 HarmonyOS架構演進與關鍵技術-HarmonyOS對DFX能力的要求是什么

HarmonyOS對DFX能力的要求

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

什么是DFX技術?DFX設計一定要執行設計規則檢查嗎?

什么是DFX技術?DFX設計一定要執行設計規則檢查嗎?

評論