相關(guān)閱讀:

RA2快速設(shè)計(jì)指南 [1] 電源與仿真器支持

RA2快速設(shè)計(jì)指南 [2] MCU工作模式和選項(xiàng)設(shè)置存儲(chǔ)器

RA2快速設(shè)計(jì)指南 [3] 時(shí)鐘電路

RA2快速設(shè)計(jì)指南 [4] 復(fù)位要求和復(fù)位電路

7. 存儲(chǔ)器

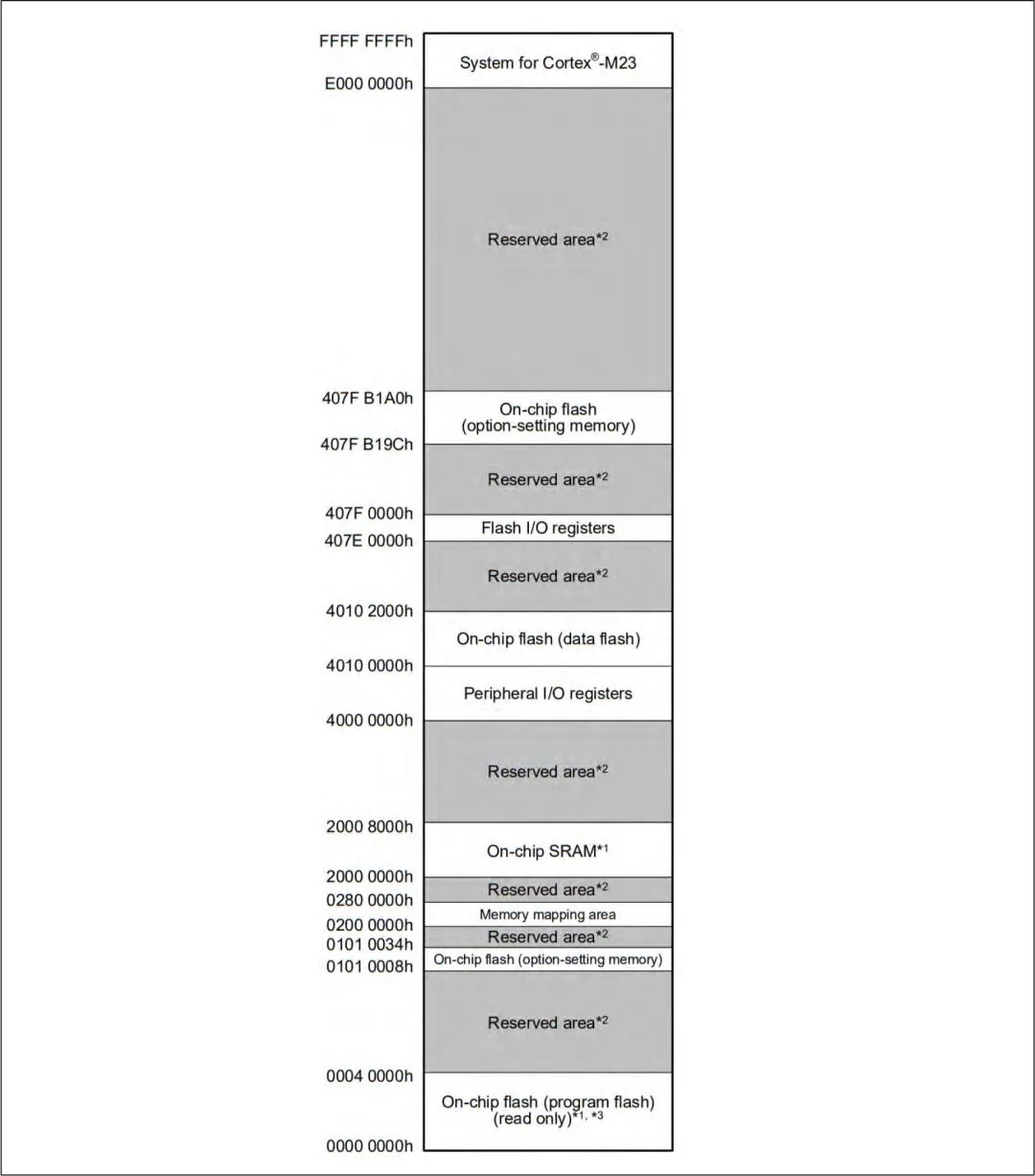

RA2 MCU支持4GB的線性地址空間,范圍為0000 0000h到FFFF FFFFh,其中可以包含程序、數(shù)據(jù)和外部存儲(chǔ)器總線。程序和數(shù)據(jù)存儲(chǔ)器共用地址空間;可使用單獨(dú)的總線分別訪問(wèn)這兩個(gè)存儲(chǔ)器,從而提高性能并允許在同一個(gè)周期訪問(wèn)程序和數(shù)據(jù)。存儲(chǔ)器映射中包含片上RAM、外設(shè)I/O寄存器、程序ROM、數(shù)據(jù)閃存和外部存儲(chǔ)器區(qū)域。

圖13. RA2A1存儲(chǔ)器映射

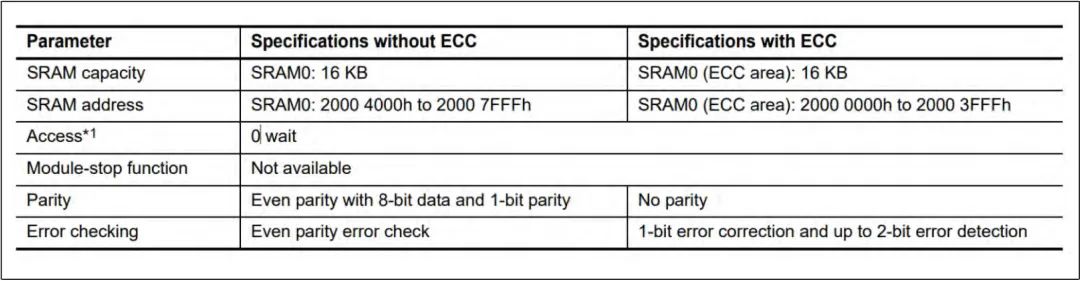

7.1 SRAM

RA2 MCU提供帶奇偶校驗(yàn)位或ECC(糾錯(cuò)碼)的片上高速SRAM模塊。SRAM0的前32 KB區(qū)域受ECC控制。奇偶校驗(yàn)在其他區(qū)域執(zhí)行。下表列出了SRAM規(guī)范。SRAM模塊的數(shù)量和容量因產(chǎn)品而異。有關(guān)詳細(xì)信息,請(qǐng)參見《硬件手冊(cè)》。

圖14. RA2A1 SRAM規(guī)格

7.2 外設(shè)I/O寄存器

外設(shè)I/O寄存器塊出現(xiàn)在存儲(chǔ)器映射中的不同位置,具體取決于設(shè)備和當(dāng)前的工作模式。大多數(shù)外設(shè)I/O寄存器占用的地址范圍為4000 0000h到400F FFFFh。但是,位置和大小可能會(huì)因產(chǎn)品而異。有關(guān)詳細(xì)信息,請(qǐng)參見《硬件手冊(cè)》。有關(guān)詳細(xì)信息,可參見“I/O寄存器”附錄,也可參見每個(gè)外設(shè)功能的寄存器說(shuō)明。該區(qū)域包含在所有工作模式下始終可用的寄存器。用于控制訪問(wèn)閃存的閃存I/O寄存器占據(jù)兩個(gè)區(qū)域,即4000 0000h至400F FFFFh和407E 0000h至407E FFFFh。

Renesas FSP包含采用CMSIS數(shù)據(jù)結(jié)構(gòu)的C頭文件,這些文件將特定器件的所有外設(shè)I/O寄存器映射到易于訪問(wèn)的I/O數(shù)據(jù)結(jié)構(gòu)。

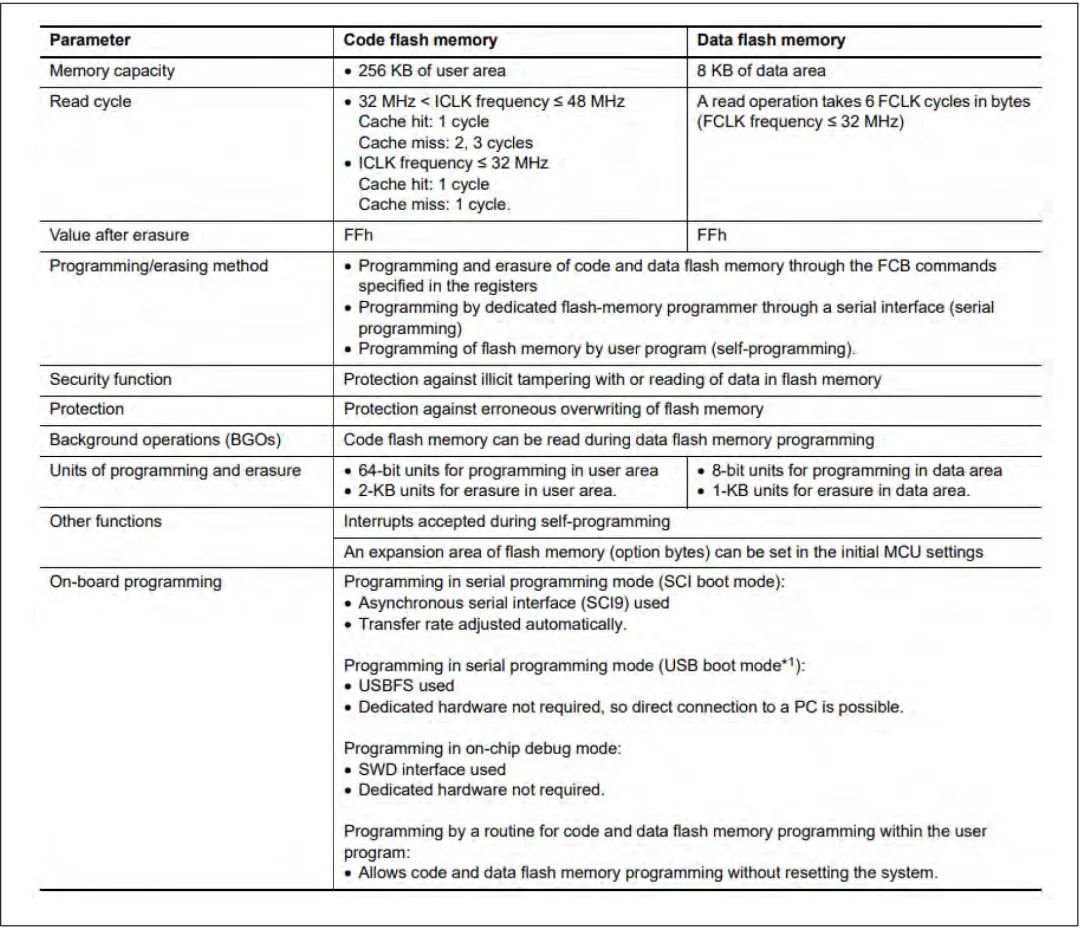

7.3 片上閃存

RA2 MCU具有兩個(gè)閃存部分:代碼閃存和數(shù)據(jù)閃存,各部分的大小和可編程周期容量因產(chǎn)品而異。閃存控制單元(FCU)控制閃存的編程和擦除。閃存應(yīng)用程序命令接口(FACI)根據(jù)指定的FACI命令控制FCU。

代碼閃存旨在存儲(chǔ)用戶應(yīng)用程序代碼和常量數(shù)據(jù)。數(shù)據(jù)閃存旨在存儲(chǔ)可能不時(shí)更新的信息,例如配置參數(shù)、用戶設(shè)置或記錄的數(shù)據(jù)。數(shù)據(jù)閃存區(qū)域中的編程和擦除單位遠(yuǎn)小于代碼閃存的單位。以RA2A1為例,代碼閃存以64-bit為單位進(jìn)行編程,以2-KB為單位進(jìn)行擦除;而數(shù)據(jù)閃存以8-bit為單位進(jìn)行編程,以1-KB為單位進(jìn)行擦除。單位大小因產(chǎn)品而已。具體請(qǐng)參見《硬件手冊(cè)》中的“數(shù)據(jù)閃存”的章節(jié)。

數(shù)據(jù)閃存和代碼閃存區(qū)域均可通過(guò)應(yīng)用程序代碼進(jìn)行編程或擦除。這樣,無(wú)需連接外部編程工具即可完成現(xiàn)場(chǎng)固件更新。

Renesas FSP為代碼閃存和數(shù)據(jù)閃存提供了HAL層驅(qū)動(dòng)程序。

下圖給出了代碼閃存和數(shù)據(jù)閃存的規(guī)格。

圖15. RA2A1 MCU上的代碼閃存和數(shù)據(jù)閃存規(guī)范

注:代碼閃存的擦除狀態(tài)為FFh,但數(shù)據(jù)閃存的擦除狀態(tài)未定義。

7.3.1 后臺(tái)操作

RA2 MCU支持通過(guò)后臺(tái)操作訪問(wèn)代碼閃存和數(shù)據(jù)閃存。這意味著當(dāng)開始執(zhí)行編程或擦除操作時(shí),用戶可以繼續(xù)從除正在操作的存儲(chǔ)區(qū)以外的存儲(chǔ)區(qū)中執(zhí)行和訪問(wèn)存儲(chǔ)器。例如,在對(duì)數(shù)據(jù)閃存進(jìn)行擦除或編程操作時(shí),CPU可以從代碼閃存執(zhí)行應(yīng)用程序代碼。同樣,在對(duì)代碼閃存進(jìn)行擦除或編程操作時(shí),CPU可以從SRAM執(zhí)行應(yīng)用程序代碼。這項(xiàng)規(guī)則的唯一例外是,在對(duì)代碼閃存進(jìn)行編程或擦除期間無(wú)法訪問(wèn)數(shù)據(jù)閃存。

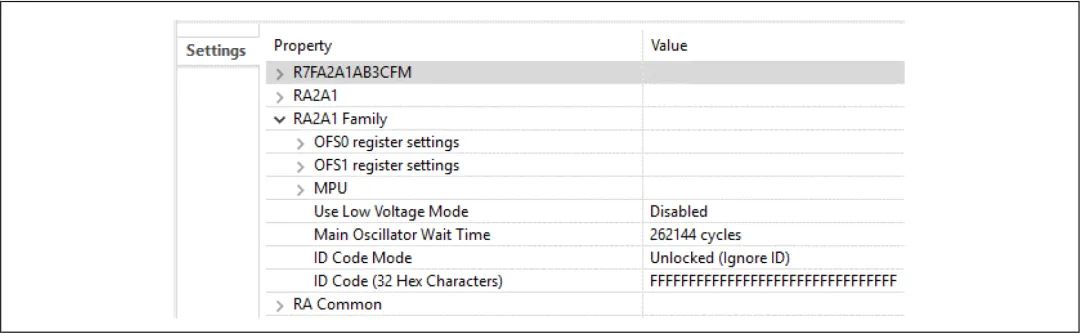

7.3.2 ID代碼保護(hù)

RA2 MCU在選項(xiàng)設(shè)置存儲(chǔ)區(qū)中有一個(gè)用作ID代碼的128位存儲(chǔ)器。如果此ID代碼保留為空(0xFF),則不會(huì)使能任何保護(hù),并且可以通過(guò)引導(dǎo)模式或使用片上調(diào)試器來(lái)訪問(wèn)MCU。如果設(shè)置了ID代碼,則用戶可以控制對(duì)這些模式的訪問(wèn)。用戶可以選擇始終禁止連接,或者可以選擇在輸入匹配的ID代碼時(shí)允許連接。有關(guān)更多信息,請(qǐng)參見“OCD/串行編程ID設(shè)置寄存器(OSIS)”和“ID代碼保護(hù)”以及《RA2 MCU硬件手冊(cè)》中的相關(guān)部分。

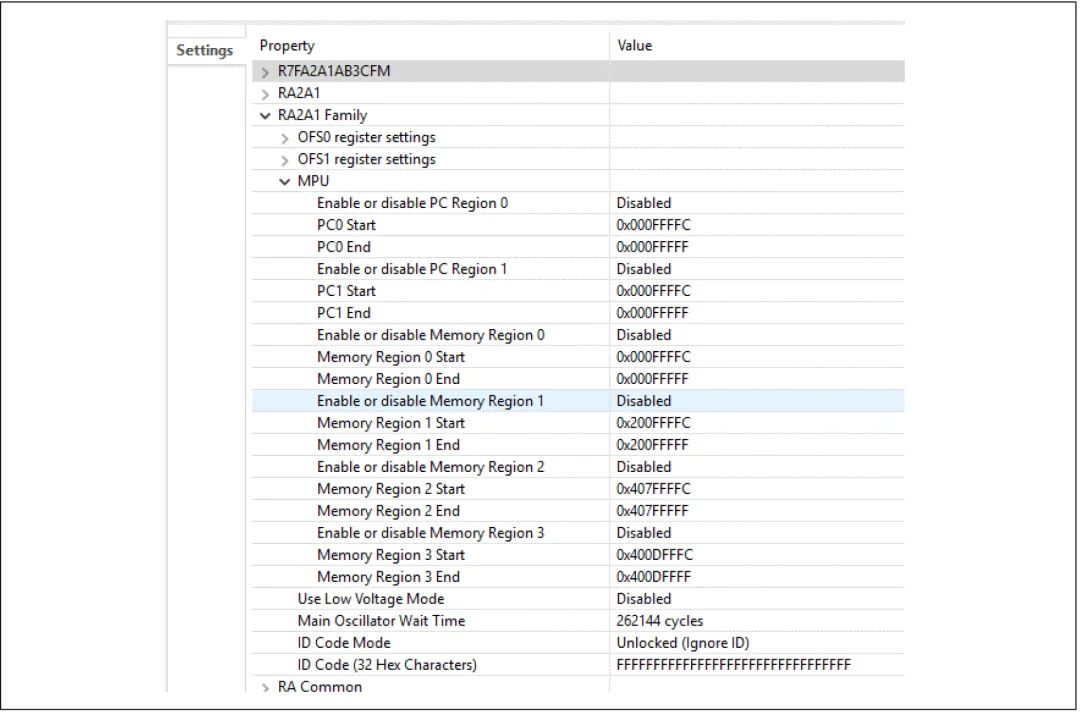

圖16 顯示了Renesas FSP配置器提供的用于設(shè)置ID代碼保護(hù)的選項(xiàng)。

圖16. 使用Renesas FSP配置器為RA2A1設(shè)置ID代碼

注:必須謹(jǐn)慎處理ID代碼保護(hù)設(shè)置,以避免發(fā)生可能導(dǎo)致阻止訪問(wèn)MCU的錯(cuò)誤。

7.3.3 存儲(chǔ)器保護(hù)單元

RA2微控制器具有存儲(chǔ)器保護(hù)單元(MPU)。這些單元能夠保護(hù)各種MCU區(qū)域免遭非法訪問(wèn)。具體選項(xiàng)包括允許讀寫、禁止寫入和禁止讀寫。通過(guò)在特定的存儲(chǔ)器地址上設(shè)置相應(yīng)的常數(shù)值可選擇這些選項(xiàng)之一。有關(guān)更多詳細(xì)信息,請(qǐng)參見《硬件手冊(cè)》中的“存儲(chǔ)器保護(hù)單元”部分。

圖17. 使用Renesas FSP配置器RA2A1設(shè)置MPU

注:必須謹(jǐn)慎處理MPU設(shè)置,以避免發(fā)生可能導(dǎo)致阻止訪問(wèn)MCU區(qū)域的錯(cuò)誤。

7.4 字節(jié)順序的限制

存儲(chǔ)器空間必須采用小端法才能在Cortex-M內(nèi)核上執(zhí)行代碼。

來(lái)源:瑞薩MCU小百科

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問(wèn)題,請(qǐng)聯(lián)系小編進(jìn)行處理

審核編輯 黃宇

-

mcu

+關(guān)注

關(guān)注

146文章

17839瀏覽量

360459 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123346 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166415

發(fā)布評(píng)論請(qǐng)先 登錄

瑞薩RA系列MCU FSP庫(kù)開發(fā)實(shí)戰(zhàn)指南(09)存儲(chǔ)器映射

閃速存儲(chǔ)器屬于RAM還是ROM,閃速存儲(chǔ)器一般用來(lái)做什么的

閃速存儲(chǔ)器的閃速是指什么,閃速存儲(chǔ)器的速度比內(nèi)存快嗎

EE-349:ADSP-2146xDDR2存儲(chǔ)器電路板設(shè)計(jì)指南

瑞薩RA家族精品RA2L1產(chǎn)品介紹

TMS320C6000 DSP外部存儲(chǔ)器接口(EMIF)參考指南

TMS320VC5503/5507/5509 DSP外部存儲(chǔ)器接口(EMIF)參考指南

TMS320C672x DSP外部存儲(chǔ)器接口(EMIF)用戶指南

MSP430存儲(chǔ)器編程用戶指南

RA2快速設(shè)計(jì)指南 [5] 存儲(chǔ)器

RA2快速設(shè)計(jì)指南 [5] 存儲(chǔ)器

評(píng)論