DRC介紹

在進行DFT Logic的設計和插入之前,DFT工程師會先使用EDA工具對原Design執行DRC(Design Rule Checking),即設計規則檢查。隨著芯片的復雜度升高,執行DRC可以顯著提高Design的可測性,同時也檢查Design的合理性。

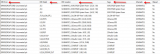

DRC案例

1

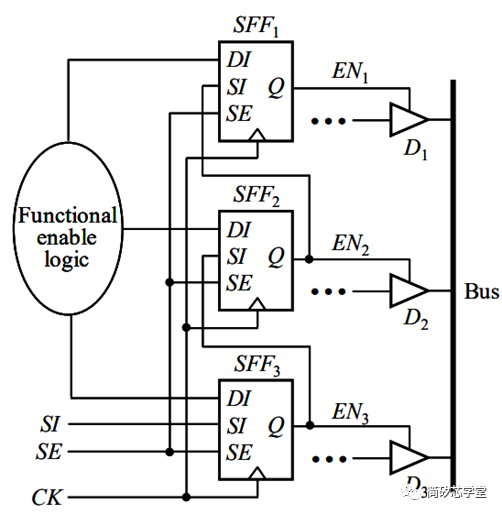

在Function模式下,由三態門嚴格控制,在同一總線上,同一時刻只允許一個設備向總線輸出。如圖1所示,三個寄存器的輸入是DI,由Functional Enable Logic控制,在同一時刻Driver D1、D2、D3只有一個被使能,可以向總線輸出數據。

但在測試模式下,Scan Shift期間三個寄存器SSF1、SSF2、SSF3連成一條Scan Chain,輸入由DI切換為SI,它們的值會根據測試pattern不停地變,無法保證3個Drivers在同一時刻只有一個驅動總線,這樣就可能會引起總線競爭的問題。

圖1

為了避免這個問題,我們加入如圖2所示的電路,當SE為1時,即Scan Shift期間,只有EN1為1,此時D1生效,D2和D3不生效。另外給總線加入Bus Keeper,使總線在3個Drivers均為高阻抗時保持總線上值不變。

圖2

但這樣的設計依舊存在一個問題:在Scan Capture期間如何避免總線競爭問題?實際上這里的解決辦法有好幾種,筆者僅提供其中一種思路:在Capture期間SE的值為0,但TE(Test Enable ,圖中未畫出)依舊為1,我們可以利用TE信號來設計邏輯使得在SE為0時依然最多只有一個Driver被使能。

2

芯片上存在一些雙向IO Pin,如圖3所示,由寄存器的輸出Q來控制IO方向,當Q=1時是Output Pin,當Q=0時是Input Pin。但在Scan Shift期間,該寄存器的值會由于測試pattern而不停地變,從而導致I/O方向不斷發生改變。

圖3

我們給原電路加入如圖4所示的邏輯,當處于Scan Shift期間,SE的值為1,無論寄存器的值是0還是1,與門的輸出均為0,這樣就保證了在Scan Shift期間該IO PIN一直是Input Pin。當然也可以換成或門的邏輯,使該IO Pin在Shift期間一直是Output Pin。

圖4

3

如圖5所示,這是一個非常簡單的時鐘門控電路,當enable為1時,gated clock與clock保持一致,當enable為0時,gated clock保持為1,即clock斷開狀態。但這樣的設計無法很好地解決hazard,具體如圖6波形圖所示。

圖5

圖6

Designer為了解決這一問題,會采取如圖7所示的設計:插入一個負沿觸發的觸發器,在時鐘下降沿對enable信號進行采樣,當enable為1時,將時鐘打開,當enable為0時,將時鐘關閉。這樣就大大降低了hazard風險,波形圖見圖8。

然而這樣做在測試中會引發另一個問題,那就是在Scan Shift期間該觸發器的值會不斷發生變化,我們也就無法控制時鐘開關了。

圖7

圖8

假設原始的Design電路如圖9所示,我們加入圖10所示的邏輯 ,當SE為1時,Clock始終保持打開的狀態,這樣就保證了Scan Shift期間Clock門控電路始終打開。

圖9

圖10

總結

本文所示案例在Function方面均屬合理的設計,但并不利于測試,這也是引入DRC的重要意義。目前市面上不同的EDA工具對于Design Rule有著不同的規則體系,但本質是一樣的,都是為了在插入DFT以及產ATPG Pattern之前消除潛在的風險并改善設計。

-

寄存器

+關注

關注

31文章

5421瀏覽量

123315 -

EDA工具

+關注

關注

4文章

271瀏覽量

32582 -

DRC

+關注

關注

2文章

153瀏覽量

36925 -

時鐘電路

+關注

關注

10文章

243瀏覽量

51242 -

DFT設計

+關注

關注

0文章

10瀏覽量

8968

發布評論請先 登錄

orcad的DRC檢測參數設置的含義是什么

orcad原理圖文件怎么進行DRC的檢測?

DRC分析和修復經驗分享

典型的DRC案例介紹

典型的DRC案例介紹

評論