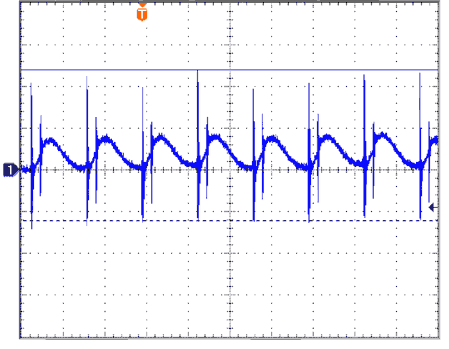

- 它們?cè)谳敵鲂盘?hào)上顯示為噪聲(包括時(shí)序噪聲和信號(hào)電平噪聲),可能導(dǎo)致邏輯電平的誤讀

- 它們產(chǎn)生的輻射EMI可以從電路板上測(cè)量,通常是從邊緣測(cè)量

|

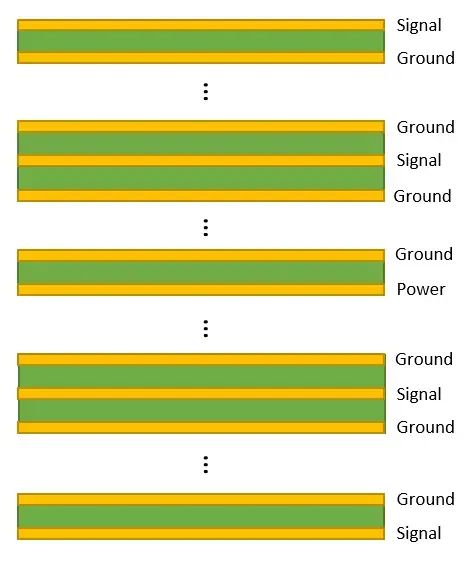

元素 |

對(duì)電源完整性的影響 |

|

電源和接地層對(duì) |

|

|

離散電容器 |

|

|

電容器封裝和過孔電感 |

|

|

嵌入式電容 |

|

|

封裝寄生效應(yīng) |

|

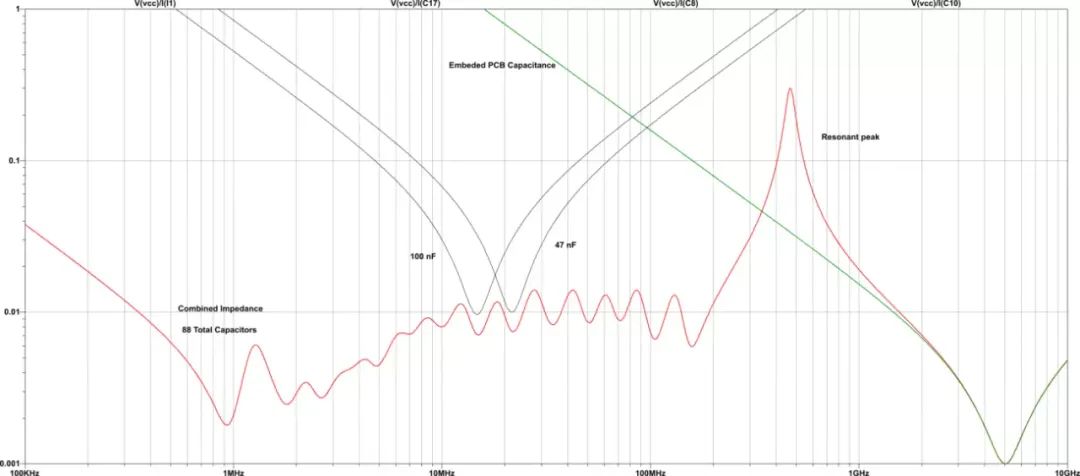

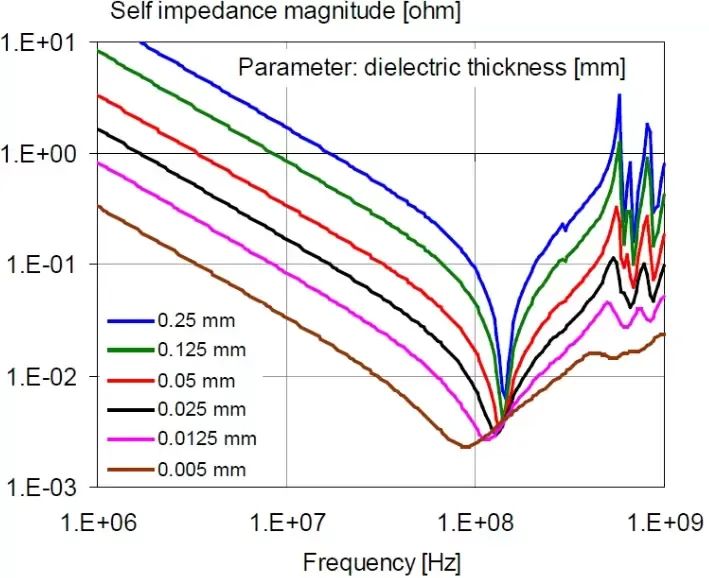

總的來說,這些元素將決定PDN的阻抗頻譜。PDN的各種貢獻(xiàn)因素如下圖所示,這些貢獻(xiàn)大致按頻率范圍劃定。此處顯示的阻抗譜由大量電容器構(gòu)成,這是以快速邊沿速率運(yùn)行的、具有高I/O計(jì)數(shù)的數(shù)字處理器的典型特征。

PDN拓?fù)?/span>

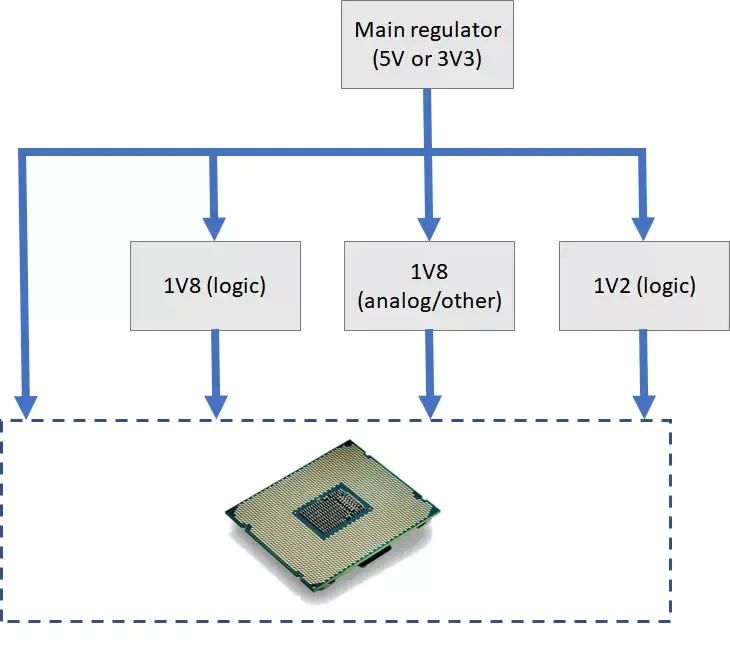

所有為高級(jí)處理器供電的PDN都是多端口網(wǎng)絡(luò)。它們需要多重穩(wěn)定電壓,從高值到低邏輯電平。在高引腳數(shù)處理器上,電壓從較高邏輯電平(5V0或3V3)下降到低至0V8是很常見的。

定義高級(jí)處理器PDN的電源樹如下所示。該示例旨在說明如何構(gòu)建不同的電源軌,這些軌道來自為整個(gè)系統(tǒng)供電的主電源或穩(wěn)壓器。

處理器的PDN拓?fù)涫纠枰膫€(gè)電壓逐漸降低的不同電源軌

處理器的PDN拓?fù)涫纠枰膫€(gè)電壓逐漸降低的不同電源軌

- 在中檔頻率下提供更高的電容,從而降低阻抗(高達(dá)1 GHz)

- 將與電源/接地層對(duì)相關(guān)的PDN諧振移至較低頻率

- 抑制與電源/接地層對(duì)相關(guān)的GHz范圍內(nèi)的PDN諧振峰值

- 將與平面電容相關(guān)的PDN阻抗谷值(從0.1到1 GHz)移至較低頻率

-

pcb

+關(guān)注

關(guān)注

4352文章

23417瀏覽量

406719

原文標(biāo)題:PCB電源完整性完整指南:從電路板到封裝

文章出處:【微信號(hào):FANYPCB,微信公眾號(hào):凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

電源完整性分析及其應(yīng)用

技術(shù)資訊 | 信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

高速PCB設(shè)計(jì)指南

高速電路PCB及其電源完整性設(shè)計(jì)

超常材料應(yīng)用于電路板進(jìn)行電源完整性、信號(hào)完整性、電磁兼容性研究

高速PCB的信號(hào)完整性、電源完整性和電磁兼容性研究

高速電路電源分配網(wǎng)絡(luò)設(shè)計(jì)與電源完整性分析

信號(hào)完整性與電源完整性-電源完整性分析

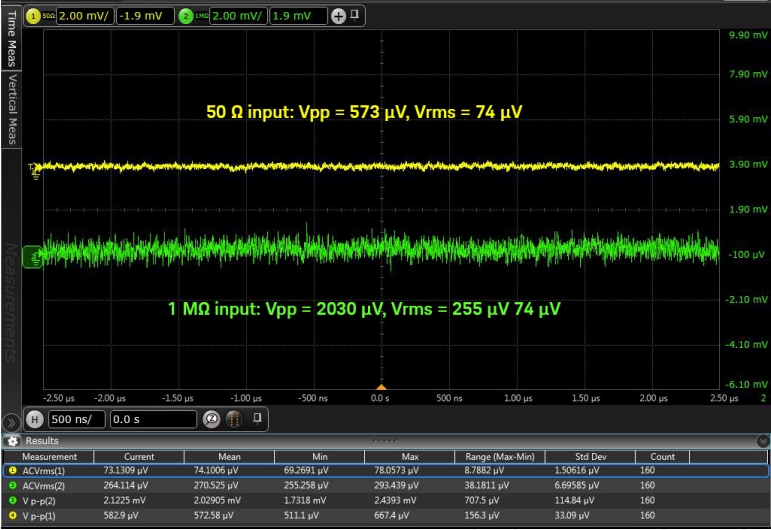

示波器探頭在電源完整性測(cè)量上的應(yīng)用

搞定電源完整性,不如先研究PDN

PCB電源完整性完整指南:從電路板到封裝

PCB電源完整性完整指南:從電路板到封裝

評(píng)論