內(nèi)存芯片制造工藝

內(nèi)存芯片在驅(qū)動ic市場和ic技術(shù)發(fā)展方面發(fā)揮了重要作用。市場上兩個(gè)主要的內(nèi)存產(chǎn)品分別是DRAM和NAND。對于一臺電腦,無論是臺式個(gè)人電腦還是筆記本電腦,產(chǎn)生的數(shù)據(jù)被寫入非揮發(fā)性存儲器件,如磁性硬盤存儲器(HDD)或固態(tài)硬盤存儲器(SSD)之前,總是首先存儲在DRAM中。臺式個(gè)人電腦或筆記本電腦的內(nèi)存容量短短幾年間成倍增長。1993年的個(gè)人電腦臺式機(jī)486僅有8兆字節(jié)(MB)的DRAM,這是從成本為100美元的4MB升級而成的。而在2009年,只需花費(fèi)30美元左右就可以購買4千兆字節(jié)(GB)的DRAM。隨著對圖形化特性的需求,特別是三維圖形需求不斷增加,一臺電腦的DRAM量需求將進(jìn)一步增加,并繼續(xù)推動DRAM制造技術(shù)的發(fā)展。

與保存數(shù)據(jù)一直需要電源供應(yīng)的DRAM不同,NAND是一種非揮發(fā)性存儲器,可以在無電源供應(yīng)下保存數(shù)據(jù)許多年。NAND閃存被廣泛應(yīng)用于移動數(shù)字電子產(chǎn)品,如MP3播放器、數(shù)碼相機(jī)、手機(jī)、高端筆記本電腦數(shù)據(jù)存儲。隨著移動電子設(shè)備應(yīng)用更多的圖形處理和視頻,對NAND的需求將進(jìn)一步增加。NAND也釆用混合形式,將固態(tài)硬盤存儲器(SSD)的數(shù)據(jù)快速存儲和磁性硬盤存儲器(HDD)的低成本結(jié)合起來。

DRAM工藝流程

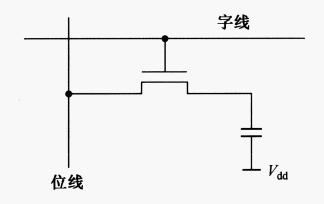

DRAM扮演著驅(qū)動IC市場和IC技術(shù)發(fā)展的重要作用。DRAM單元由一個(gè)NMOS和一個(gè)存儲電容組成(見下圖)。

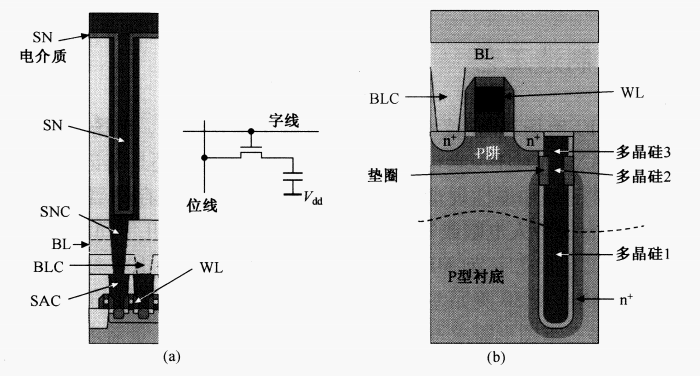

有兩種DRAM形成工藝:一種是堆疊DRAM,是將存儲電容堆疊在晶體管(NMOS)上;另一種是深溝槽DRAM,這種結(jié)構(gòu)是在NMOS旁邊的硅表面上形成深溝槽式存儲電容。

下圖(a)顯示了堆疊式DRAM。SAC代表自對準(zhǔn)接觸,BLC表示位線接觸,WL代表字線,BL代表位線,SNC表示存儲節(jié)點(diǎn)接觸,SN表示存儲節(jié)點(diǎn),就是存儲電容。下圖(b)所示為一個(gè)深溝槽DRAM。由于溝槽電容的長寬比超過50,所以圖示只是一部分。從圖中可以看到,深溝槽DRAM的硅表面金屬互連面積比較小,使得這種結(jié)構(gòu)更容易和普通的CMOS后端工藝兼容,并成為片上系統(tǒng)(SoC)應(yīng)用嵌入式DRAM的選擇。然而,由于這種結(jié)構(gòu)需要在有限的硅表面形成存儲電容,溝槽式DRAM的堆積密度與堆疊DRAM不同,因?yàn)檫@種結(jié)構(gòu)并不需要很大的硅表面構(gòu)建存儲電容。通用DRAM芯片對價(jià)格非常敏感。由于堆疊式DRAM比深溝槽DRAM成本低,所以它主導(dǎo)著DRAM市場。本章只討論堆疊式DRAM工藝流程。

堆疊式DRAM工藝流程

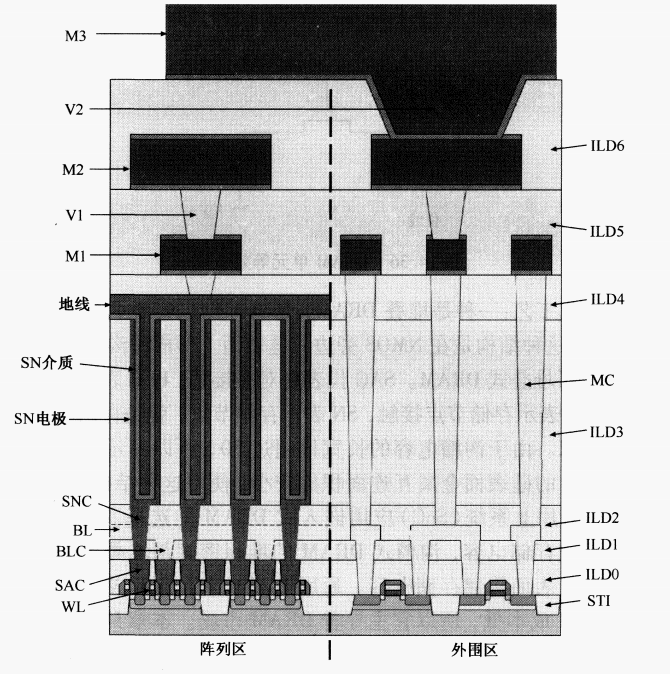

大多數(shù)電腦和其他數(shù)碼電子產(chǎn)品使用的DRAM芯片是堆疊式DRAM。下圖顯示了堆疊式DRAM芯片橫截面。下圖左側(cè)顯示了具有4個(gè)存儲單元的截面。3nm工藝技術(shù)的2GBDRAM芯片具有20億個(gè)這樣的單元。外圍邏輯電路用于控制寫入、讀出和DRAM芯片的輸入/輸出操作。外圍器件面積通常比陣列單元面積大,而且制作工藝與之前描述的CMOSI藝技術(shù)非常類似。后續(xù)將主要說明單元陣列的工藝流程。

審核編輯:劉清

-

存儲器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166449 -

內(nèi)存芯片

+關(guān)注

關(guān)注

0文章

127瀏覽量

22370 -

DRAM控制器

+關(guān)注

關(guān)注

0文章

11瀏覽量

7902 -

ICT技術(shù)

+關(guān)注

關(guān)注

0文章

44瀏覽量

10327 -

NMOS管

+關(guān)注

關(guān)注

2文章

123瀏覽量

5887

原文標(biāo)題:半導(dǎo)體行業(yè)(二百零一)之ICT技術(shù)(十一)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

內(nèi)存芯片制造工藝 DRAM工藝流程 堆疊式DRAM工藝流程

內(nèi)存芯片制造工藝 DRAM工藝流程 堆疊式DRAM工藝流程

評論