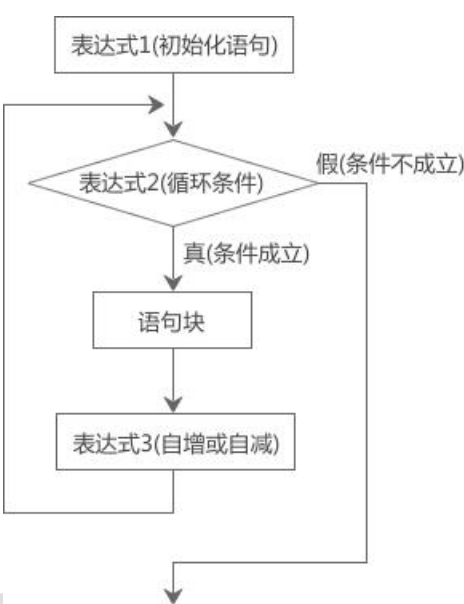

1、采用for(int*)實(shí)現(xiàn)不同信號(hào)賦值的循環(huán)

利用for循環(huán)實(shí)現(xiàn)對(duì)信號(hào)的賦值。

如下案例中,func_id_vld為512bit,需要根據(jù)func_mode_in[1024-1:0]給func_id_vld賦值,func_mode_in每2個(gè)bit對(duì)應(yīng)一個(gè)func_id_vld,即func_mode_in[1:0]對(duì)應(yīng)func_id_vld[0],func_mode_in[3:2]對(duì)應(yīng)func_id_vld[1],func_mode_in[1023:1022]對(duì)應(yīng)func_id_vld[511], 賦值規(guī)則為func_mode_in[1:0]為2‘b01時(shí),func_id_vld[0]為1,以此類推。

采用for(int*)類型格式,可以在一個(gè)else分支中使用,不需要使用generate,使用更加靈活,使用范圍更廣。

always@(posedge clk)

if(~rst_n) begin

func_id_vld <= 512'b0 ;

end else begin

for(int i=0; i<512;i=i+1) begin : func_id_vld_gen

func_id_vld[i] <= (func_mode_in[2*i+:2]==2'b01) ;

end

end

2、采用for(int*)實(shí)現(xiàn)同一個(gè)信號(hào)賦值的循環(huán)

下圖所示,采用for(int*)類型格式實(shí)現(xiàn)了一個(gè)16mux1的循環(huán)賦值語(yǔ)句,實(shí)現(xiàn)不同條件一下,對(duì)debug_test_16mux1的賦值操作,即16mux1的邏輯。

always@(*) begin

debug_test_16mux1 = 128'd0;

for(int i=0; i<16;i=i+1) begin : debug_test_16mux1_gen

if(cfg_16mux1_mode ==i) begin

debug_test_16mux1 = debug_test_in[128*i+:128] ;

break ;

end

end

end

always@(*) begin case(cfg_16mux1_mode) 0 : debug_test_16mux1 = debug_test_in[127 :0 ]; 1 : debug_test_16mux1 = debug_test_in[255 :128 ]; 2 : debug_test_16mux1 = debug_test_in[383 :256 ]; 3 : debug_test_16mux1 = debug_test_in[511 :384 ]; 4 : debug_test_16mux1 = debug_test_in[639 :512 ]; 5 : debug_test_16mux1 = debug_test_in[767 :640 ]; 6 : debug_test_16mux1 = debug_test_in[895 :768 ]; 7 : debug_test_16mux1 = debug_test_in[1023 :896 ]; 8 : debug_test_16mux1 = debug_test_in[1151 :1024 ]; 9 : debug_test_16mux1 = debug_test_in[1279 :1152 ]; 10: debug_test_16mux1 = debug_test_in[1407 :1280 ]; 11: debug_test_16mux1 = debug_test_in[1535 :1408 ]; 12: debug_test_16mux1 = debug_test_in[1663 :1536 ]; 13: debug_test_16mux1 = debug_test_in[1791 :1664 ]; 14: debug_test_16mux1 = debug_test_in[1919 :1792 ]; 15: debug_test_16mux1 = debug_test_in ; endcase end

NOTE:在for(int*)語(yǔ)句中,如果寫成debug_test_16mux1 = debug_test_in[128*i+127:128*i] , VCS會(huì)報(bào)語(yǔ)法錯(cuò)誤;只寫成debug_test_16mux1 =debug_test_in[128*i+:128],此處需要注意。

審核編輯:劉清

-

Verilog

+關(guān)注

關(guān)注

28文章

1366瀏覽量

111812 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9844 -

for

+關(guān)注

關(guān)注

0文章

44瀏覽量

16040 -

for循環(huán)

+關(guān)注

關(guān)注

0文章

61瀏覽量

2669

原文標(biāo)題:verilog語(yǔ)法:幾種可綜合的for循環(huán)語(yǔ)句

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FOR循環(huán)語(yǔ)句分析與應(yīng)用

開關(guān)語(yǔ)句和循環(huán)語(yǔ)句

C語(yǔ)言入門教程-if語(yǔ)句和while循環(huán)

Java的循環(huán)語(yǔ)句的詳細(xì)資料說(shuō)明

C語(yǔ)言的for循環(huán)語(yǔ)句的程序和電路圖免費(fèi)下載

Verilog可綜合的循環(huán)語(yǔ)句

簡(jiǎn)述HDL中循環(huán)語(yǔ)句的可綜合性

什么是python break語(yǔ)句-終止循環(huán)

C語(yǔ)言for語(yǔ)句介紹

Python的循環(huán)語(yǔ)句介紹

Verilog常用的循環(huán)語(yǔ)句及用途

MATLAB中條件語(yǔ)句和循環(huán)結(jié)構(gòu)的使用方式

條件語(yǔ)句/循環(huán)語(yǔ)句simulink的實(shí)現(xiàn)方法(一)

for循環(huán)語(yǔ)句基本用法及示例 介紹幾種可綜合的for循環(huán)語(yǔ)句

for循環(huán)語(yǔ)句基本用法及示例 介紹幾種可綜合的for循環(huán)語(yǔ)句

評(píng)論